HARDWARE IMPLEMENTATION OF THE SALSA20 AND PHELIX STREAM CIPHERS

JUNJIE YAN

# Hardware Implementation of the Salsa20 and Phelix Stream Ciphers

by

@ Junjie Yan

## A THESIS SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF

MASTER OF ENGINEERING

in

## Faculty of Engineering and Applied Science MEMORIAL UNIVERSITY OF NEWFOUNDLAND

October 2007

St. John's Newfoundland

## Acknowledgements

First of all I would like to thank my supervisor Dr. Howard Heys for his constant guidance and support. Without his supervision, this thesis would not exist.

I would also like to thank Dr. Cheng Li. His courses, especially LSI Design (Engr. 8863) and Digital Systems (Engr. 5865) not only made me familiar with the hardware design flow but also the use of VHDL as design language and input for logic synthesis. They are critical tools for my research.

I am very grateful to Canadian Microelectronic Corporation (CMC) as well as Mentor Graphics for their help in providing design tools and the access to state-of-the-art manufacturing technologies.

I thank Namin Yu for the useful literature she provided. With the literature as guidance for chapter organization, grammars and format, I saved a lot of time in terms of thesis writing.

Many thanks to Huiju Cheng for being a great lab partner, travel mate and my best friend at MUN. Our cooperation resulted in more ideas in my research, which was truly rewarding.

I thank Peter Vandrish for his insightful comments and criticism and for careful reading of my papers before publishing. I very much appreciated the pleasant and fruitful time studying together with him.

Furthermore, I would like to express my gratitude to Avalon Microelectronics Incorporation, who has provided me with a fabulous job as an FPGA designer, making it possible for me to continue my work and study on hardware implementation in a broader range of applications.

> Junjie Yan July 15, 2007

> > ii

## Abstract

This thesis investigates the hardware implementation and statistical analysis of new stream ciphers, Phelix and Salsa20. Both are candidates for the eSTREAM project, a project highlighting the state of stream cipher design and analysis.

From a physical technology perspective, hardware implementation methodology consists of Application Specific Integrated Circuit (ASIC) design and Field Programmable Gate Array (FPGA) design. When high performance is required, an ASIC is typically chosen as the implementation platform. However, FPGA platforms have become increasingly popular due to their flexibility and a diminishing performance tradeoff as compared with ASIC technology. Following this trend we have developed two versions of Salsa20, one for deployment on an ASIC, the other for an FPGA. The cipher Phelix is studied for application to ASIC environment.

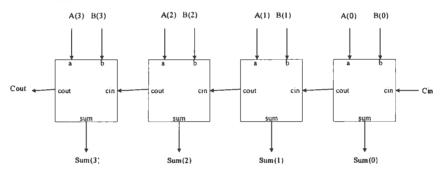

Implementing a cipher requires detailed knowledge of the cryptographic algorithm itself, particularly the underlying arithmetic. In the case of Phelix and Salsa20, both of which are composed of several simple operations: 32-bit addition, bitwise addition (exclusive or) and rotation, the most important operation is the 32-bit addition, for which we have investigated multiple structures for the adders and compared them in both speed and area. Different adder architectures are chosen for different designs, and the basic criteria is the concern of speed or area the overall implementation consumes.

Two structures for Phelix have been implemented, one is a high speed design and the other one is aimed at compactness. The simulation results shows that it consumes about 12,000 two-input NAND gates in the compact design and achieves more than one Gbps throughput in the high speed design. The speed of the compact design is 260 Mbps and the area of the high speed design is 64,200 two-input NAND gates. Up to four different structures are investigated for Salsa20 as extra considerations are given to the utilization of FPGA. The proposed VLSI implementations achieve a data throughput up to 4.8 Gbps, and a compact FPGA design uses 194 slices and 4 memory blocks in a Xilinx device. The proposed designs in the thesis serve mainly as a quick evaluation of their hardware performance; hence, further architectural optimizations are certainly possible.

Security analysis is an important concern in cipher designs. Thus, we have applied

certain statistical tests, which are publicly available in the NIST (National Institute of Standards and Technology) test suite to test various sequences produced by using the Phelix and Salsa20 algorithms. Since the test suite has not considered the relationship between key, IV, internal state and the keystream, we also applied six novel tests to examine the ciphers. Two strategies are employed to interpret the test results: the examination of the proportion of sequences that pass a statistical test and the distribution of P-values to check for uniformity. NIST gives the definition of P-value: the probability that a perfect random number generator would have produced a sequence less random than the sequence that was tested. The experimental results show that both Salsa20 and Phelix have passed the tests in NIST, considering that P-value less than 0.01 indicate a possible weakness. An easily understood deviation is observed in the correlation test for the last internal state (the state after 9 double rounds) and the keystream in Salsa20. However, how this could be exploited in an attack is an open question.

## **Table of Contents**

| Acknowledgementsii                            |

|-----------------------------------------------|

| Abstractiii                                   |

| Table of Contents                             |

| List of Figuresix                             |

| List of Tablesxi                              |

| List of Abbreviationsxii                      |

| Chapter 1 An Introduction to Cryptography 1   |

| 1.1 Brief History of cryptography 1           |

| 1.2 Information Security                      |

| 1.3 Background on Functions                   |

| 1.3.1 One-way Function                        |

| 1.3.2 Permutation                             |

| 1.3.3 Substitution                            |

| 1.3.4 Exclusive OR                            |

| 1.3.5 Modular Addition                        |

| 1.3.6 Modular Multiplication                  |

| 1.4 Symmetric-key/Private-Key Cryptography    |

| 1.4.1 Block Ciphers7                          |

| 1.4.2 Stream Cipher                           |

| 1.5 Asymmetric-key/Public-key cryptography 11 |

| 1.6 Cryptanalysis                             |

| 1.7 Summary                                   |

| Chapter 2 Cipher Implementation 15            |

| 2.1 Software Implementation                   |

| 2.2 Hardware Implementation                   |

| 2.2.1 Methodology                             |

| 2.2.1.1 Traditional Methodology Used for Non-feedback Cipher Modes |

|--------------------------------------------------------------------|

| 2.2.1.2 ASIC Design Flow & FPGA Design Flow                        |

| 2.2.2 Main Concerns in Hardware Implementation                     |

| 2.3 Software/Hardware Codesign                                     |

| 2.4 Summary                                                        |

| Chapter 3 Hardware Implementation of the Phelix Stream Cipher      |

| 3.1 Introduction of Phelix Stream Cipher                           |

| 3.1.1 Algorithm                                                    |

| 3.1.2 Security                                                     |

| 3.1.3 Previous Work on Hardware Implementation on Phelix           |

| 3.2 Compact ASIC Structure of Phelix                               |

| 3.2.1 Top Level Design                                             |

| 3.2.2 32-bit Adder                                                 |

| 3.2.3 H Function Block                                             |

| 3.2.4 Key Mixing Block                                             |

| 3.2.5 Nonce Expanding Block 40                                     |

| 3.2.6 Subkey Generator                                             |

| 3.3 High Speed ASIC Structure of Phelix                            |

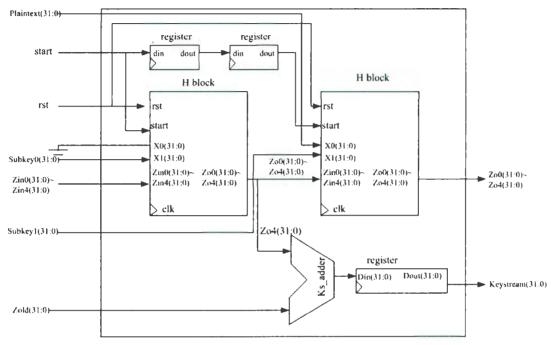

| 3.3.1 H Function Block                                             |

| 3.3.2 Key Mixing Block 44                                          |

| 3.3.3 Nonce Expanding Block 45                                     |

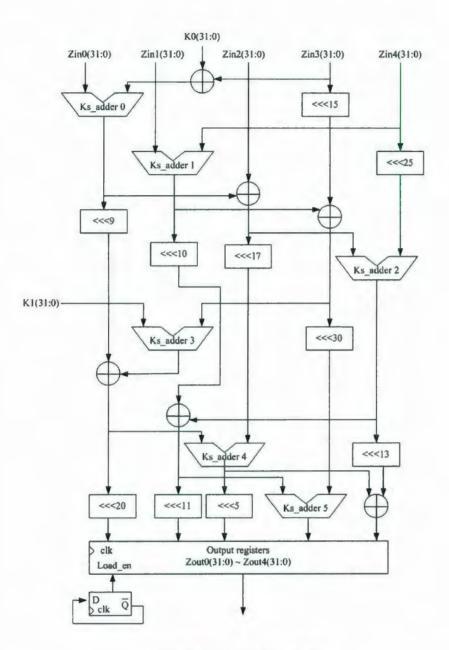

| 3.3.4 Keystream Generation Block                                   |

| 3.3.5 The Controller                                               |

| 3.4 Synthesis Results of Phelix                                    |

| 3.5 Summary                                                        |

| Chapter 4 Hardware Implementation of the Salsa20 Stream Cipher     |

| 4.1 Introduction of Salsa20 Stream Cipher                          |

| 4.1.1 Algorithm                                                         | 49 |

|-------------------------------------------------------------------------|----|

| 4.1.2 Security                                                          | 50 |

| 4.1.3 Previous Work on Hardware Implementation on Salsa20               | 50 |

| 4.2 Analysis of Salsa20 Cipher Main Components                          | 52 |

| 4.2.1 32-bit Adder                                                      | 52 |

| 4.2.2 Quarterround Block                                                | 56 |

| 4.2.3 Memory Block                                                      | 58 |

| 4.2.4 Control Unit based on Various Datapath                            | 61 |

| 4.2.4.1 Controller of the Compact ASIC Structure                        | 61 |

| 4.2.4.2 Controller of the Basic Iterative and High Speed ASIC Structure | 63 |

| 4.2.4.3 Controller of the Compact FPGA Structure                        | 64 |

| 4.3 The Synthesis Results of Salsa20                                    | 65 |

| 4.4 Summary                                                             | 66 |

| Chapter 5 Statistical Test of Salsa20 and Phelix                        | 68 |

| 5.1 Introduction                                                        | 68 |

| 5.2 General Discussion                                                  | 69 |

| 5.2.1 Randomness                                                        | 69 |

| 5.2.2 Test Statistic and P-value                                        | 69 |

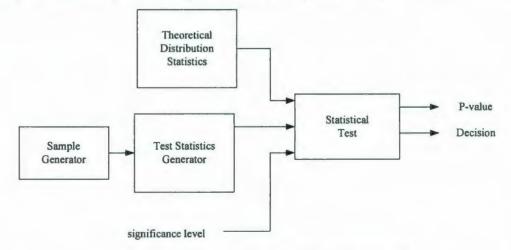

| 5.3 Test Model                                                          | 71 |

| 5.4 Keystream Tests                                                     | 72 |

| 5.4.1 Frequency (Monobit) Test                                          | 72 |

| 5.4.2 Frequency Test Within a Block                                     | 73 |

| 5.4.3 Discrete Fourier Transform Test                                   | 74 |

| 5.4.4 Runs Test (Wald-Wolfowitz Test)                                   | 75 |

| 5.4.5 Experimental Results and Analysis                                 | 75 |

| 5.4.5.1 Proportion of Sequences Passing a Test                          | 75 |

| 5.4.5.2 Uniform Distribution of P-values                                | 76 |

| 5.5 Correlation Tests                                                     |

|---------------------------------------------------------------------------|

| 5.5.1 Testing New Sequences                                               |

| 5.5.1.1 Sequence Generation Process                                       |

| 5.5.1.2 Experimental Results and Analysis                                 |

| 5.5.2 Keystream/Internal States Correlation Test                          |

| 5.5.2.1 Algorithm                                                         |

| 5.5.2.2 Experimental Results and Analysis                                 |

| 5.5.3 Internal States Correlation Test                                    |

| 5.5.3.1 Algorithm                                                         |

| 5.5.3.2 Experimental Results and Analysis                                 |

| 5.6 Conclusions                                                           |

| Chapter 6 Conclusions and Future Work91                                   |

| 6.1 Summary of Research                                                   |

| 6.2 Future Work                                                           |

| Reference                                                                 |

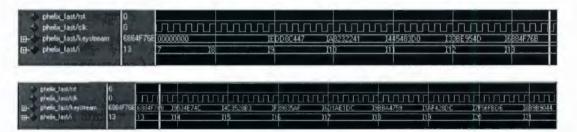

| Appendix A: Selected Simulations Results for Phelix 103                   |

| Appendix B: Selected Simulations Results for Salsa20 104                  |

| Appendix D: Selected Source Code for Phelix                               |

| Appendix E: Selected Source Code for Salsa20 120                          |

| Appendix F: Selected Codes for Statistical Tests 137                      |

| Appendix G: A Test Example to Illustrate the Distribution of P-values 148 |

## **List of Figures**

| Figure 1.1 A Taxonomy of Cryptographic Primitives [6]                | 6  |

|----------------------------------------------------------------------|----|

| Figure 1.2 Two-party Communications Using Symmetric Key Cryptography | 7  |

| Figure 1.3 Encryption/Decryption Process of Block Ciphers            | 8  |

| Figure 1.4 Encryption/Decryption Process of Stream Ciphers           | 9  |

| Figure 1.5 A Linear feedback shift registers (LFSR)                  | 10 |

| Figure 1.6 Encryption/Decryption Process for Public Key Ciphers      |    |

| Figure 1.7 Sign/Verify Process for Digital Signature                 |    |

| Figure 2.1 Architectures Used for Non-feedback Cipher Modes          | 17 |

| Figure 2.2 Comparison of ASIC & FPGA Design Flows [9]                |    |

| Figure 2.3 Gated Clock for Register Bit                              |    |

| Figure 2.4 Typical Flip Flop Cell in FPGAs                           |    |

| Figure 2.5 NAND Gate Symbol                                          |    |

| Figure 2.6 Parallel Scheme for Power Reduction [4]                   |    |

| Figure 2.7 Example Scenario for a Stream Cipher [60]                 |    |

| Figure 2.8 Typical FPGA Logic Block                                  |    |

| Figure 3.1 H Function                                                |    |

| Figure 3.2 Block Diagram of Hardware Accelerator for Phelix          |    |

| Figure 3.3 Phelix Compact Structure                                  |    |

| Figure 3.4 State Diagram of the Top Level Controller                 |    |

|                                                                      |    |

| Figure 3.5 A 4-bit RCA.                                              |    |

| Figure 3.6 One block of Phelix Encryption [22]                       |    |

| Figure 3.7 Simplified Datapath of the H Function Block               |    |

| Figure 3.8 Complete Datapath of the H Function Block                 |    |

| Figure 3.9 Datapath of the Key Mixing Block                          |    |

| Figure 3.10 Datapath of Nonce Expanding Block                        |    |

| Figure 3.11 Datapath of Subkey Generator                             | 42 |

| Figure 3.12 Phelix High Speed Structure                              | 43 |

| Figure 3.13 H Function Block                                         |    |

| Figure 3.14 Block Diagram of Keystream Generator                     |    |

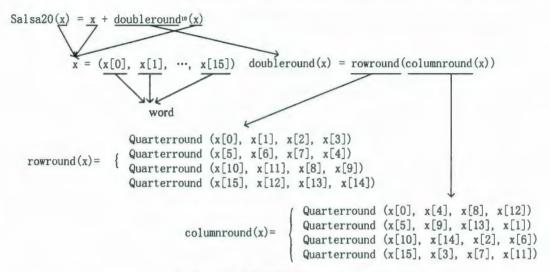

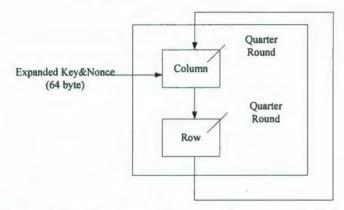

| Figure 4.1 Salsa20 Keystream Generation                              | 50 |

| Figure 4.2 Block Diagram of Hardware Accelerator for Salsa20         |    |

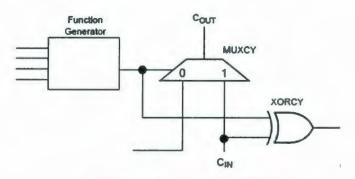

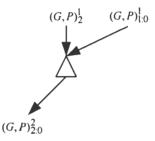

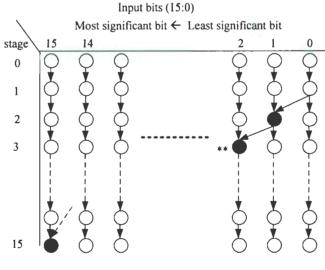

| Figure 4.3 Carry Logic Diagram [74]                                  |    |

| Figure 4.5 16-bit Ripple Carry Adder                                 | 55 |

| Figure 4.6 16-bit Kogge-Stone Parallel Prefix Adder                  |    |

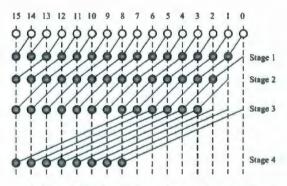

| Figure 4.7 Block diagram of a 4-bit carry select adder               |    |

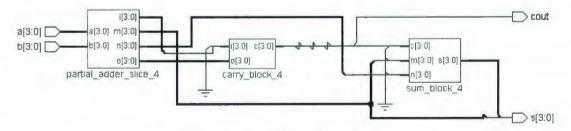

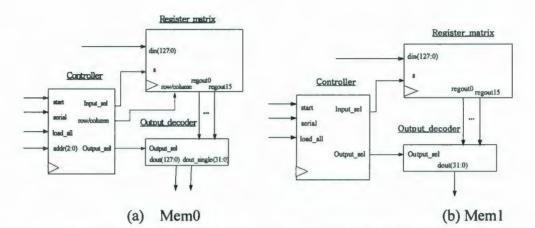

| Figure 4.8 Datapath of Quarterround Block                            |    |

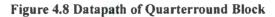

| Figure 4.9 Finite State Machine of the Sequential Quarterround Block | 58 |

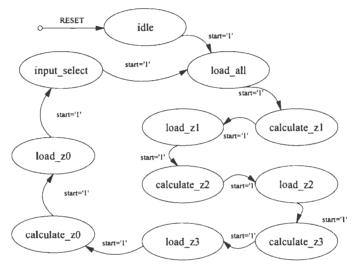

| Figure 4.10 A 32-bit Wide RAM                                        | 59 |

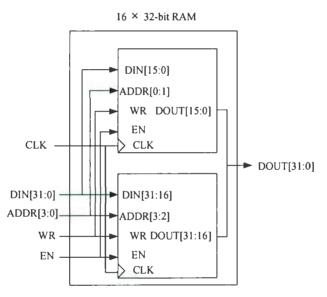

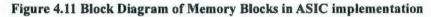

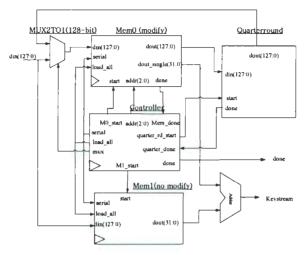

| Figure 4.11 Block Diagram of Memory Blocks in ASIC implementation    |    |

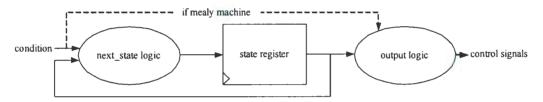

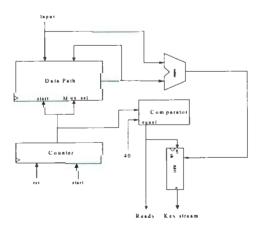

| Figure 4.12 Block Diagram of FSM                                     |    |

| Figure 4.13 Datapath of Compact ASIC Structure for Salsa20           |    |

| Figure 4.14 FSM of Compact ASIC Structure for Salsa20                | 63 |

| Figure 4.15 Salsa20 Basic Iterative ASIC Structure                   |    |

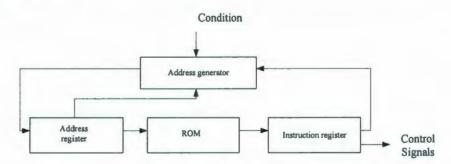

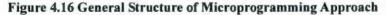

| Figure 4.16 General Structure of Microprogramming Approach           | 64 |

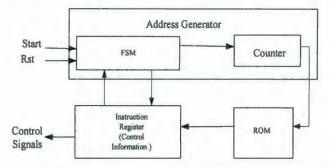

| Figure 5.1 An Example of Statistical Test [18]                       |    |

| Figure 5.2 Model for Statistical Hypothesis Test                     |    |

| Figure 5.3 Frequency Test Algorithm                                  | 72 |

| Figure 5.4 Block Frequency Test Algorithm                            | 73 |

| Figure 5.5 Discrete Fourier Transform Test Algorithm                 | 74 |

|                                                                      |    |

| Figure 5.6 Runs Test Algorithm                                   | 75 |

|------------------------------------------------------------------|----|

| Figure 5.7 Frame Correlation Sequence Generation Algorithm       |    |

| Figure 5.8 Diagram of Frame Correlation Sequence                 | 80 |

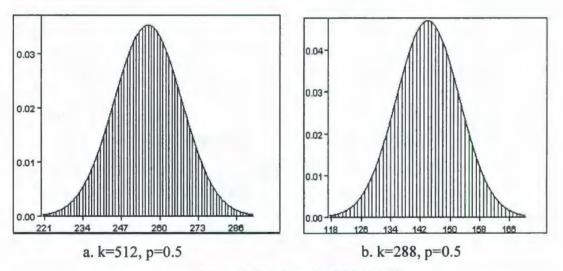

| Figure 5.9 Diffusion Sequence Generation Algorithm               |    |

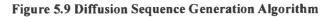

| Figure 5.10 Theoretical Distribution                             |    |

| Figure 5.11 keystream/Internal States Correlation Test Algorithm | 84 |

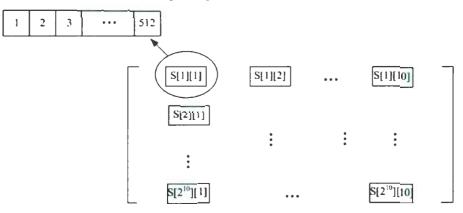

| Figure 5.12 Salsa20 Internal States Matrix                       |    |

|                                                                  |    |

## List of Tables

| Table 2.1 Area complexity of CMOS standard cells                | 22 |

|-----------------------------------------------------------------|----|

| Table 2.2 The Truth Table of NAND Gate                          | 23 |

| Table 2.3 Power Consumption of 0.18 µm CMOS Standard Cells [43] | 23 |

| Table 3.1 FPGA Hardware performance of Phelix [68]              | 31 |

| Table 3.2 Results of Phelix Co-design                           | 32 |

| Table 3.3 ASIC Implementation Results of Phelix                 | 47 |

| Table 4.1 Results of Salsa20 Co-design [60]                     | 51 |

| Table 4.2 Comparison of Adder Implementations                   | 53 |

| Table 4.3 Synthesis Results for Different Memory Blocks         | 60 |

| Table 4.4 Implementation Results of Salsa20                     | 65 |

| Table 4.5 Cipher performance and area comparison [47]           | 66 |

| Table 5.1 the Result of Proportion of Sequences Passing a Test  | 76 |

| Table 5.2 The Result of Uniform Distribution of P-values        | 78 |

| Table 5.3 Proportion of Sequences Passing a Test                | 81 |

| Table 5.4 The Result of Uniform Distribution of P-values        | 82 |

| Table 5.5 Test Results for Salsa20                              | 85 |

| Table 5.6 Test Results for Phelix                               | 86 |

| Table 5.7 Test Results for Salsa20                              | 89 |

| Table 5.8 Test Results for Phelix                               | 89 |

| Table 6.1 Comparison of FPGA Design and ASIC Design             | 93 |

## List of Abbreviations

| AES   | Advanced Encryption Standard                     |

|-------|--------------------------------------------------|

| ASIC  | Application Specific Integrated Circuit          |

| CBC   | Cipher-block Chaining                            |

| CFB   | Cipher Feedback                                  |

| ECB   | Electronic Codebook                              |

| FPGA  | Field Programmable Gate Array                    |

| FSM   | Finite State Machine                             |

| GB    | Gigabyte                                         |

| Gbps  | Gigabits per second                              |

| GF    | Galois Field                                     |

| IP    | Intellectual Property                            |

| IV    | Initialization Vector                            |

| LFSR  | Linear Feedback Shift Register                   |

| MAC   | Message Authentication Code                      |

| Mbps  | Megabits per second                              |

| MUX   | Multiplexer                                      |

| NIST  | Institute of Standards and Technology            |

| OFB   | Output Feedback                                  |

| RAM   | Random Access Memory                             |

| S-box | Substitution Box (or vectorial Boolean function) |

| VPN   | Virtual Private Network                          |

| XOR   | Exclusive OR                                     |

|       |                                                  |

## **Chapter 1 An Introduction to Cryptography**

### 1.1 Brief History of cryptography

Cryptography is a fascinating topic related to confidentiality, authenticity and integrity of information and its origin. The earliest cryptography can be traced back to the Egyptians 4000 years ago. At that time, cryptography was concerned solely with message confidentiality, such as encryption, which concerns the process of converting original information (plaintext) into indistinguishable gibberish (ciphertext). The most striking development of cryptography came with the proliferation of the computers and communication systems since 1960s. During this time, when humans communicate with each other by using digital signals instead of traditional written language symbols, large volumes of information exchanging over untrusted medium, such as the Internet, make the classical cryptographic methods out of date; security becomes a tremendously important issue to deal with. The search for new encryption schemes and improvements to existing information security mechanisms and cryptanalysis continues at a rapid pace.

In 1978, the first practical public-key encryption algorithm was discovered, known as RSA, which is based on the intractability of factoring large integers. During 1970s, IBM designed the Data Encryption Standard (DES), the most common symmetric key cryptography scheme used today. DES has been used extensively in electronic commerce. Since 1975, some people have noted that the key size of DES is too small. Moreover, some others worried about NSA's involvement. In 1987, the well known stream cipher RC4 was created by Ronald Rivest. To generate a pseudorandom keystream, the cipher makes use of a secret internal state consist of 2064 bits and two 8-bit index pointers. The plaintext is combined with the keystream using the exclusive-or (XOR) function. In 1997, NIST launched a project to find primitives that were suitable to replace DES. Among the candidates, the Rijndael algorithm was selected at last in 2001 and has become the Advanced Encryption Standard (AES). Recently, quantum computing techniques in cryptography have attracted a lot of attention as a new area of research. It is believed that quantum mechanical principles used in computation might significantly outperform the current prevailing cryptography methods.

Nowadays, the rapid growth of electronic applications and business based on the Internet has fueled the need for cryptographic methods to protect information processing.

### **1.2 Information Security**

A very important issue related to cryptography is information security. Both of them share the common goals of protecting information. However, the scope of information security is larger than cryptography. Over the centuries, information security does not only use cryptography to mask usable information, but also includes the process of protecting data from unauthorized access, use, disclosure, destruction, modification, or disruption [1]. Information security requires a vast range of methods and the technical means is typically provided by cryptography.

Some objectives are frequently used interchangeably in information security, computer security and information assurance. For example, *Data Integrity* is one of the objectives that are used in all of the three fields. It ensures that the information has not been altered by unauthorized or unknown means. Some other objectives include:

- 1. Message Authentication: corroborates of the identity of an entity.

- 2. Signature: binds information to an entity.

- 3. Validation: provides timeliness of authorization to use information.

- 4. Witnessing: verifies the existence of information by an entity.

More objectives associated with information security are listed in [6].

Information security was mostly applied in military in the past, such as the old Caesar Cipher [70] and the Playfair Cipher [70], which was widely used by the British and U.S armies in World War I. World War II probably brought about most advancement in information security. Also, it witnessed the formalized classification of data based on the information sensitivity [61].

The core principles of information security include confidentiality, integrity and availability, which are known as the CIA Triad. Confidentiality is a service used to prevent information to be accessed, used or disclosed by unauthorized parties. Approaches providing confidentiality range from physical protection to cryptographic algorithms. Integrity is used to avoid unauthorized alteration of data. Data alteration includes substitution, insertion and deletion. Availability means that all the resources used

to process and protect the information are available and work correctly when needed.

### **1.3 Background on Functions**

While this thesis will look into the details of implementation of different functions in selected ciphers, a familiarity with basic mathematical functions that are widely used in cryptography will be helpful.

#### **1.3.1 One-way Function**

A function f is called a one-way function if f(x) is easy to compute but hard to invert. "Easy to compute" means computationally feasible or equivalently, one can compute the function in polynomial time. "Hard" in the context refers to average case complexity [6].

The existence of a one-way function is partly dependent on an open conjecture  $P \neq NP$ , where P is the set of decision problems that are known to be solvable in polynomial time, and NP is the set of decision problems that can be solved by a non-deterministic Turing machine in polynomial time [51]. In other words, if P = NP, any function that can be computed in polynomial time can be inverted in polynomial time, which means that one-way functions do not exist. However, it is not know whether  $P \neq NP$  is the sufficient condition of the existence of one-way function.

Many useful cryptographic primitives like pseudorandom number generators are based on the existence of a one-way function. Obviously, it is not known whether a one-way function candidate is indeed one-way at present. Some famous candidates supported by current research results include integer factorization and discrete logarithm. The widely used RSA cryptosystem is an example that utilizes integer factorization, while the Digital Signature Algorithm (DSA) [82] uses the discrete logarithm problem.

#### **1.3.2 Permutation**

In a permutation, a set of objects or symbols are rearranged into distinguishable sequences. Permutations are invertible functions that are often used as a basic component in various cryptographic constructs, particularly in symmetric key cryptographic algorithms to encrypt large volumes of data. That is because the permutation is easy to be implemented and works fast in hardware implementations since bit or byte level permutations do not require any extra resources but simply reorder logic signals. DES and triple DES use bit level permutations to spread the redundancy of the plaintext over the ciphertext.

However, in software implementations, bit level permutations bring two challenges [63]. In existing RISC processors,  $O(n)^*$  instructions are generally required in generic ways to achieve any one of n! permutations, that is the reason for old processors not supporting arbitrary bit level permutations except a restricted subset known as rotation. The other challenge is that the instructions may need more than two word-sized operands and/or produce more than one word-size result. For example, multiplying two 1024-bit operands in RSA requires two 16-word operands, if the computer is 64-bit word based.

#### **1.3.3 Substitution**

In cryptography, substitution is a method that substitutes the units of plaintext with ciphertext according to an alphabet; the "units" might be one symbol or a mixture of symbols. The receiver decrypts the ciphertext by performing an inverse substitution.

The substitution function can be compared with transposition or permutation functions. The difference is that, in a transposition procedure, what changes is the order of the plaintext units, while in a substitution procedure, the units of the plaintext are retained in the same position in the ciphertext, but the units themselves are changed.

Old substitution ciphers are often vulnerable to frequency analysis [10]. Hence, most of them, such as a simple affine cipher, are no longer in serious use. However, the concept of substitution is still being used today. From an unusual perspective, some modern bit-oriented ciphers (e.g. DES) can be considered as substitution ciphers with an enormously large binary alphabet. Additionally, some smaller substitution tools known as an S-boxes are often used for confusion, which obscures the relationship between the plaintext and the ciphertext.

If a substitution scheme and a permutation scheme are used serially in a cipher, then it is called SP – network, or substitution-permutation network (SPN). AES is a case in

$<sup>^{\</sup>circ}$  O(n) is called big O notation in computational complexity theory. It is often used to describe the relationship between the size of the input data and the running time or memory consumption of an algorithm [24].

point [56]: in the substitution step, each byte in the process is replaced with its entry in a fixed lookup table, known as an S-box; in the permutation step, bytes in each row are shifted cyclically to the left.

#### 1.3.4 Exclusive OR

Exclusive OR, also known as XOR, is a bitwise operator from binary mathematics. In modern ciphers, XOR is often used to mix key bits into the cipher data. It can be denoted as:

$$C = P \oplus K$$

where  $\oplus$  denotes XOR operation, C is ciphertext, P is plaintext and K is key. According to the principles of XOR, the decryption process is merely reapplying the key as below:

#### $P = C \oplus K$

If the key or keystream is as long as the message, the system is similar to the one-time pad that is theoretically unbreakable. Besides, XOR is simple to implement and computationally inexpensive. It is provable that the uncertainty in attempting to guess the keystream is equal to that of directly guessing the plaintext. The security of the one-time pad is based on this. Clearly, when the length of plaintext is very long, it is impractical to maintain and distribute the keystreams. As a result, stream ciphers are introduced and developed by the loose inspiration from the one-time pad. More details will be discussed later.

#### **1.3.5 Modular Addition**

Many cryptographic primitives include modular *addition* because addition mod  $2^n$  is a nonlinear transformation over GF(2) and the operation is fast in both software and hardware. GF(2) is the Galois Field of elements 0 and 1. Nonlinear transformation is of great importance in cryptography as it makes functions hard to invert.

Keeping with the popularity of addition in ciphers, Klimov and Shamir proposed T-function in 2002 [5]. T-function employs *addition* mixed with *multiplication* and *or* in a certain way to update every bit the internal state. The authors of [57] investigated the probability distribution of the carry chain for integer addition. More literature that looked into modular addition for various aspects can be found in [33], [32], [13] and [37].

#### **1.3.6 Modular Multiplication**

Modular multiplication is widely used in cryptography as it has good diffusion properties [76]. It is a multiplication performed over a finite field. The most straightforward method for performing modular multiplication is to compute the remainder on division by the modulus. This is referred to as the classical modular multiplication algorithm.

Since most applications are based on the binary representation system, the modulus is often a power of two (as in RC6). Therefore, some efficient algorithms without explicitly carrying out the classical modular reduction step are widely exploited. For example, in [76] a technique is proposed, which efficiently implements  $2^{n}+1$  prime modulus operation by using only two additional additions and one multiplication.

### 1.4 Symmetric-key/Private-Key Cryptography

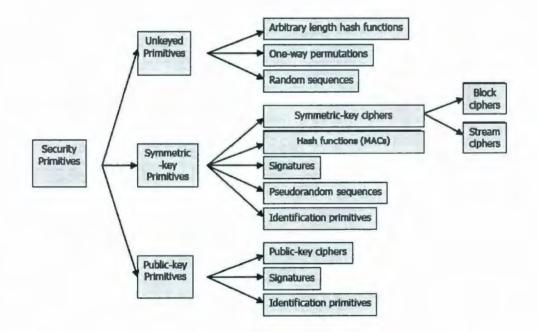

There are many ways to divide cryptographic primitives. Figure 1.1 provides a schematic listing of the primitives considered.

Figure 1.1 A Taxonomy of Cryptographic Primitives [6]

Among the list shown above, our main concern is symmetric-key cryptography and

6

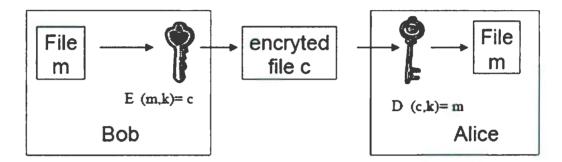

public-key cryptography. Symmetric-key/Private-Key cryptography was the only kind of encryption publicly known until 1976 [73]. In this method, both sides of information communication share the same secret key, or different keys that are related in an easily computable way. The scenario can be described by the block diagram of Figure 1.2.

Figure 1.2 Two-party Communications Using Symmetric Key Cryptography

It is assumed that both the sender Alice and the receiver Bob know the encryption/decryption scheme. The ciphertext is transmitted through an insecure channel, which is possibly eavesdropped by a third party Eve.

An encryption algorithm E is employed to encrypt the plaintext m with the secret key k; c is the resulting output as the ciphertext. After Alice receives the ciphertext, the corresponding decryption algorithm D is used with the same secret key k to reveal the original plaintext m.

Symmetric-key encryption can be divided into stream ciphers and block ciphers.

#### 1.4.1 Block Ciphers

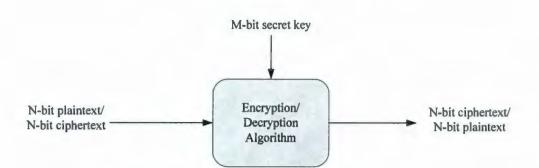

A block cipher is a symmetric-key cipher that operates on data in blocks. The input plaintext and the output ciphertext have fixed lengths, often 64, 128 or 256 bits. Another input is the secret key as shown below:

**Figure 1.3 Encryption/Decryption Process of Block Ciphers**

The size of key is closely related to the security of the cipher. Typically, the key size relates to the effort and time needed to decrypt it by brute force. It is widely accepted that a key should be large enough to prevent a brute force attack. Different cryptographic systems may have different key sizes but with the same level of security in relation to other non-brute force attacks.

For a specific block cipher, the length of a data block is fixed. When the message is longer than one block size, a mode of operation is required. Some modes of operation allow block ciphers to operate on a message of arbitrary length. The earliest modes described in the literature include Electronic Codebook mode (ECB), Cipher Block Chaining mode (CBC), Cipher Feedback mode (CFB), and Output Feedback mode (OFB). Another aspect to consider for messages coming in a variety of lengths is padding, which pads the final block before encryption. The simplest padding is to add null bytes or bits to the plaintext to make it a multiple of the block size. More padding methods can be found in [81].

Block ciphers are widely used in many applications and cryptosystems. An old and prevailing block cipher was the Data Encryption Standard (DES) with a block size of 64 bits and a key size of 56 bits. In October 2000, the National Institute of Standard and Technology (NIST) selected Rijndael algorithm for a standard known as the Advanced Encryption Standard (AES) [72] with the objective to replace DES. The result is a block cipher that is capable of supporting a block size of 128 bits and key sizes of 128, 192, and 256 bits.

#### 1.4.2 Stream Cipher

Stream ciphers treat the plaintext bit by bit or byte by byte continuously and generate one

bit/byte of ciphertext at a time. Much of the popularity of stream ciphers is due to the theory of one-time pad; originally known as the Vernam cipher [28].

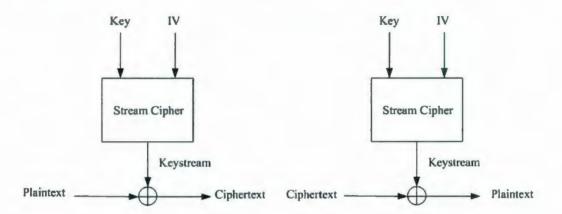

Typically a stream cipher has a key setup phase and a pseudorandom bit generation phase (keystream generation). In the key setup phase, a secret key and a known initial vector IV are fed into the keystream generator to generate the initial internal state of the cipher and expand the original key when needed. In the pseudorandom bit generation phase, the keystream generator creates pseudo-random sequences to XOR with the plaintext bits. The encryption and decryption processes are shown in Figure 1.4.

**Figure 1.4 Encryption/Decryption Process of Stream Ciphers**

As shown above, the sender and the receiver must be exactly synchronous. If digits are altered or removed from the message during transmission, it might cause decryption failure. However, several schemes can be used to rebuild synchronization. For example, regular points in the output can be selected and added with tags, which functions like a marker to inform the receiving side.

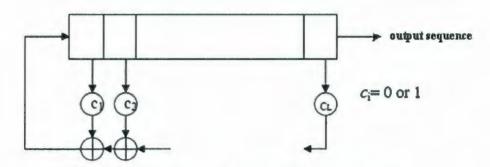

Many stream cipher designs are based on linear feedback shift registers (LFSRs) [80] as shown in Figure 1.5. LFSRs by themselves are trivially breakable but non-linear functions such as the use of clock-controlled generators [80] can be added to increase security. LFRS based stream ciphers are very popular since it is easy for them to be implemented in hardware, and their properties are well-understood.

9

Figure 1.5 A Linear feedback shift registers (LFSR)

Sometimes, a stream cipher can be derived from a block cipher. For example, a block cipher in the output feedback (OFB) mode generates keystream blocks, which are then XORed with the plaintext to produce the ciphertext. Counter mode is another method to turn a block cipher into a stream cipher. It has similar characteristics to OFB; the difference is that it allows a random access within the keystream during decryption because each encryption block operates on independent input, contrary to OFB, in which every output feedback block cipher operation depends on all previous ones. An example for counter mode is Salsa20 [20], a new stream cipher that will be introduced in Chapter 4. It generates the next block of keystream by making use of successive values of a counter.

Even when derived from a block cipher, most stream ciphers in practical use are still generated independently from the plaintext. It is error propagation free, but also has a drawback of requirement for synchronization. However, some stream ciphers violate the model: the keystream depends on the plaintext. An example is Phelix [22]. The authors claim that the basic reason for this violation is to incorporate message authentication "for free".

The security of a stream cipher significantly depends on the period of the keystream, that is, the size of the keystream before it starts to repeat itself. It is a very practical concern and tradeoff between the security and the size of the keystream should be made based on the requirement of the targeted application.

Compared with block ciphers, stream ciphers are more suitable for applications where plaintext comes in bursts, since the former works on blocks of fixed length, leading to a choice between transmission efficiency or implementation complexity. Although it is impossible to conclude which one is more superior, block ciphers have received more attention when comparing the proceedings of the major cryptography conferences. This imbalance may due to the preoccupation of the block cipher Data Encryption Standard (DES) [70], which had mastered the area of symmetric key cryptography for many years.

In October 2004, the state of stream cipher design and analysis were highlighted by the ECRYPT Network of Excellence in Cryptology, which initiated a workshop to develop a project called the ECRYPT Stream Cipher Project [34], with the goal to identify new stream ciphers that might become suitable for widespread adoption.

### 1.5 Asymmetric-key/Public-key cryptography

Public-key cryptography is also known as asymmetric cryptography. It uses a pair of keys (a secret key and a public key) instead of one secret key during the encryption and decryption process. The public key, as the name indicates, may be widely distributed, while the secret key is kept private. Only with the corresponding secret key, the plaintext encrypted with the public key can be decrypted.

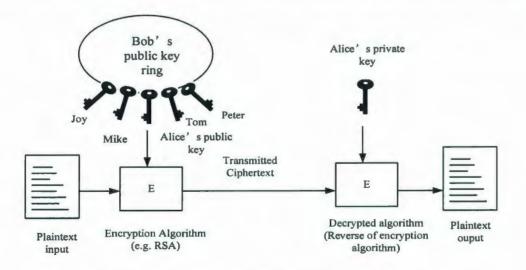

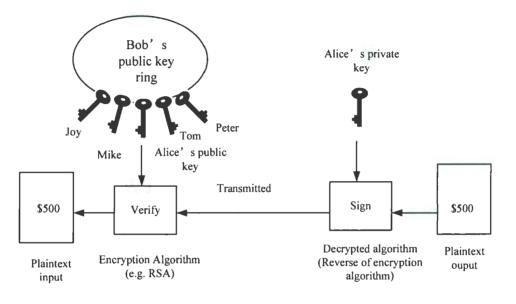

Public key cryptography is often divided into two categories based on their applications: public key ciphers and digital signatures, which are shown in Figure 1.6 and Figure 1.7, respectively. Only one transmission direction is shown in the figures since the other one is exactly the same except that the names "Bob" and "Alice" exchange.

Figure 1.6 Encryption/Decryption Process for Public Key Ciphers

Public key ciphers are used to ensure confidentiality, since only the receiver's secret key can decrypt the message. To the contrary, in a digital signature, any one that holds the sender's public key can verify a message signed with the sender's secret key. This method is used for message authenticity.

Figure 1.7 Sign/Verify Process for Digital Signature

Normally, a symmetric-key algorithm runs much faster than a public-key algorithm because of fewer computations, but public-key algorithms can facilitate key distribution. For example, if there is a communication group of n people, n(n-1)/2 secret keys are required to ensure security in a symmetric-key system, and they should be changed regularly during distribution. It indicates that symmetric keys need to be distributed in an authentic and confidential manner. But in a public-key system, only authenticity is considered, thus, it simplifies key management. To take advantage of both, symmetric-key algorithms and public-key algorithms are not typically used alone. In modern cryptographic algorithm implementations, they are often used as a combination.

### 1.6 Cryptanalysis

Although breaking codes and ciphers has a very long history, the systematic study of cryptanalysis is relatively recent. In 1920, William Friedman firstly proposed the word "*Cryptanalysis*" for the methods and study to obtain the encrypted message, without

knowing the secret information, such as a secret key. The development of computers allows more complex encryption schemes related to binary format information. However, it has also facilitated cryptanalysis.

During many years, the main concern in cryptography is to propose and implement good ciphers that stay ahead of cryptanalysis. Normally, a "good" cipher does not indicate absolute security, but is based on the standard that breaking it requires an effort that makes cryptanalysis too inefficient and impractical.

Nowadays, many types of attacks on cryptographic systems have been invented. Most of them can be categorized into two branches:

- A passive attack: threatens message confidentiality since the adversary can monitor the communication channel.

- An active attack: not only threatens message confidentiality but also data integrity since the adversary might add, delete, or alter the original message that is transmitted through the communication channel.

The objective of cryptanalysis can be recovering plaintext from ciphertext, or even deducing the decryption key. Based on the assumptions about how much information could be obtained by the adversary, cryptanalysis can be performed under the attacks below:

- Ciphertext-only attack: the cryptanalyst only observes a collection of ciphertexts, and tries to deduce the decryption key.

- Known-plaintext attack: the cryptanalyst has a group of ciphertexts and their corresponding plaintext.

- Chosen-plaintext (chosen-ciphertext) attack: the cryptanalyst can access the ciphertext (plaintext) for an arbitrary chosen plaintext (ciphertext).

- Adaptive chosen-ciphertext attack: improved version of chosen-ciphertext attack since the cryptanalyst chooses ciphertext based on information learned from previous requests.

Practically, determining whether an attack is successful depends on the amount of resources it requires, or more specific, time complexity and space complexity. The former could be from a measurement on the number of basic computer instructions; the latter often indicates the amount of storage required to perform the attack. One of the

most important assumptions in modern cryptography is Kerckhoffs' Principle [11]: In assessing the security of a cryptosystem, on should always assume the enemy knows the details of the cipher being used. As a result, the security of a cryptosystem should be based on the key instead of the encryption/decryption algorithm it uses.

### 1.7 Summary

This chapter introduces various aspects of cryptography. Emphasis has been placed on the basic issues of block cipher and stream cipher. The discourse on the rudiments of cryptography leads us gradually to move deeper into the implementation and performance evaluation of ciphers. One of the major inspirations for working on hardware implementation of specific ciphers is the rapidly increasing demand for different hardware designs for various applications, some of which, such as cell phones, take compactness as most important factor in real use while others, such as virtual private network (VPN) applications, prefer high speed.

The following chapter is about software implementation and hardware implementation design and methodologies. Selected topics about software/hardware co-designs and considerations for trade-offs can be found too.

## **Chapter 2 Cipher Implementation**

A cryptosystem can be developed by implementing one or several cryptographic algorithms either on general-purpose microprocessor [45] or on ASICs/FPGAs. Typically, the former is called software implementation, and the latter is known as hardware implementation.

Also, to match the challenges of modern applications that have different requirements about speed and area efficiency, hardware/software codesign for cryptographic systems as a standard design technique has attracted much attention in recent years.

### 2.1 Software Implementation

Software implementation is a very flexible method to realize encryption/decryption algorithms. Most software implementations are based on a general-purpose processor and its corresponding instruction set. The algorithm is translated into a group of instructions, which will be accessed one by one, decoded into machine language and executed to fulfill encryption/decryption tasks.

One important factor that decides the efficiency of software implementation is the basic underlying architectures, such as the word size of the processor. This is evident if one looks into the performance of AES on different platforms [29]. In the eSTREAM project, most stream ciphers are simple designs composed of a series of simple operations. Thus, when their corresponding codes run on a general processor, the hits or misses on L1 cache that is a typical component of today's RISC processors can have a significant impact on the performance.

Another factor is the software language used. In most of the cases, ciphers implemented by assembly language generally produce better performance compared with interpreted language [39]. That is why most benchmarks to measure the performance of algorithms tend to choose low-level language for implementation. However, it does not mean giving up high-level language implementations. Some languages like Java have priority in flexibility with an interpreter, and they are very suitable for a wide range of cross-platform software implementations. In our hardware implementation, we also use a

Java software implementation to verify the generated keystreams.

Sometimes, bad coding style may have a significant impact on the performance. For example, executing the code " $c = 8 \times a$ " can be much slower than executing an equivalent code " $c = a \ll 3$ ", where " $\ll$ " means shift left.

Nowadays, a majority of software implementations for symmetric-key cryptographic algorithms have a speed level of several hundred Mbps for the throughput.

### 2.2 Hardware Implementation

For the last decade, high-speed applications such as virtual private network (VPN) applications and secure e-commerce web servers have gained increasing acceptance in the industry. To sustain the high throughput, the demand for high-speed encryption is also rapidly increasing. A hardware implementation typically runs faster than its software counterpart. The main reason is that an application specific chip contains none of the baggage necessary to execute non-cryptographic workloads. Hence, many block ciphers implemented in hardware achieve throughput in Gbps by taking advantage of parallelism. For example, a full pipelined AES-128 hardware implementation that runs at 200 MHz has a throughput of 128 bits  $\times$  200 MHz = 25.6 GB/s.

However, some ciphers are sequential in nature, such as LFSRs based stream ciphers. Hence, they can not be pipelined. Thus, the throughput is directly decided by the clock frequency. In general, the throughput can be defined as below [44]:

Throughput =  $N \times clock$  frequency

where N is the width of the output processed per clock cycle.

The clock frequency typically depends on the critical path, that is, the longest path between registers. When the critical path is relatively long, higher N can compensate to improve throughput.

Except the advantage in speed, hardware implementation provides a suitable level of security related to side-channel attacks [15], which are based on considerable technical knowledge of the physical system, rather than the weakness of the algorithm itself. For instance, the timing information or the power leaks could provide the information for cryptanalysis. Thus, the well-studied underlying structure of a general processor saves much effort for cryptanalyst. Alternatively, a hardware implementation can be designed to

be explicitly resistant to side channel attacks.

#### 2.2.1 Methodology

#### 2.2.1.1 Traditional Methodology Used for Non-feedback Cipher Modes

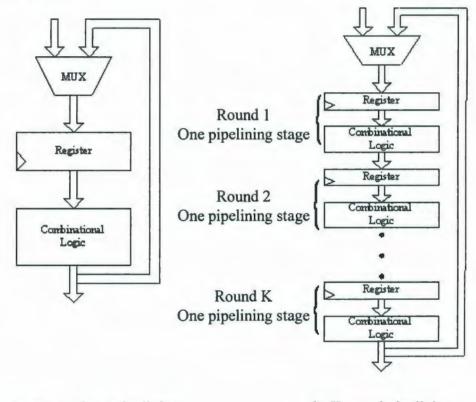

The traditional methodology for efficient implementations of secret key block ciphers is shown in Figure 2.1.

a) one round, no pipelining b) K round pipelining

Figure 2.1 Architectures Used for Non-feedback Cipher Modes

Figure 2.1.(a) is known as a basic iterative structure. Based on the basic iterative architecture, a reasonable estimation for speed and area for a single round can be estimated. From these estimations, the pipeline stages can be decided without exceeding the available hardware resources. Usually, a single stage is the implementation for a basic round. Figure 2.1.(b) is a partial outer-round pipelined structure applied for limited resources. Extra registers are inserted between any two stages. In this way, with a K-stage pipeline, K blocks of data can be processed by the circuit at the same time. At the end of

a clock cycle, the output of each block will be stored in those registers. The throughput as well as the area increase proportionally to the number of stages, while the latency for encryption and decryption remains the same as in a basic iterative structure.

Although pipelining increases the speed of the implementation significantly, equalizing data and control path latency are very important issues to guarantee the overall efficiency. Moreover, it cannot be used with the standard feedback modes such as OFB and CFB since the output of one iteration of the encryption/decryption process must be available before the next iteration can start. In our design, both iterative structure and pipelined structure are investigated for comparison on speed and area.

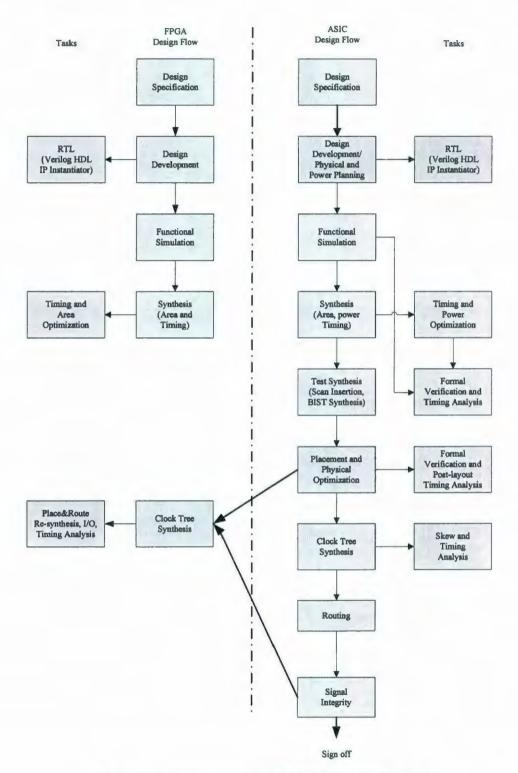

#### 2.2.1.2 ASIC Design Flow & FPGA Design Flow

From a physical technology perspective, hardware implementation methodology consists of ASIC design and FPGA design. The cost of designing application specific integrated circuits (ASICs) is increasing every year. Issues such as non-recurring engineering (NRE) cost, clock tree synthesis, and time-to-market delays can have significant impact on ASIC design.

In hardware implementations, major parts such as CPU and memories need to be connected by extra custom electronic circuitry. Glue logic is designed to do this job. Since the first programmable device with glue logic, both the speed and the density have increased dramatically. Hence, today's field programmable gate arrays (FPGAs) play a central role in digital hardware implementations. With the support for numerous EDA tools, designers tend to choose FPGA when the volume of the product is less than millions of chips. Typical ASIC and FPGA design flows are shown in Figure 2.2.

Figure 2.2 Comparison of ASIC & FPGA Design Flows [9]

The ASIC back-end design involves more tasks than FPGA design. In both of them,

19

an initial design idea has to go through several steps before it is completely implemented in hardware or chips. In our design, we followed the guidelines shown in Figure 2.2, because formalized flows can improve design debugging capabilities.

In the design specification step, we used a divide-and-conquer strategy called top-down methodology, while in more concrete design development stage we chose the modular design approach bottom-up methodology. More technical details can be found in [79].

Normally, for a design with sequential logic, we have two choices before RTL coding: synchronous design or asynchronous design. In synchronous design, there is a global clock to control all registers. Asynchronous design is widely used in communication system, where two or more different clock frequencies result in different clock domains, which require extra logic for synchronization. The main disadvantage is the existence of race conditions. In ASIC libraries, registers with asynchronous built-in "reset" pin consume more area and appear slower, therefore, all of our ASIC designs use registers with an external gate on the data path for a reset. That is, the reset is routed through the data pin. The clock must be running when the reset signal is asserted. However, it is not a problem for our FPGA design as there is already a reset tree in place. All registers have a built-in reset, so no extra care is needed.

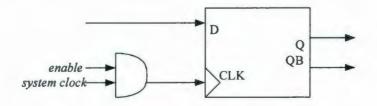

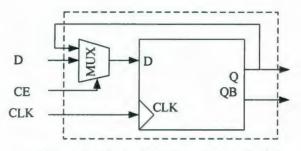

Clock gating is used in our ASIC designs for power optimization as memories have been used and data can be accessed only when the Write/Read enable signal is asserted. Read enable signal and write enable signal could be either separate or a same signal. Figure 2.3 shows an example for gated clock. Glitches may appear in such a design. However, the simulation results show that the period of the clock is long enough to ignore the glitches. FPGA designs have no such potential dangers since they have a clock enable pin that can be used to avoid the gate clocking.

Figure 2.3 Gated Clock for Register Bit

20

Figure 2.4 Typical Flip Flop Cell in FPGAs

### 2.2.2 Main Concerns in Hardware Implementation

Before mid 1990s, the limits in VLSI technology and clock rate made the pursuit for speed in a hardware implementation become a general goal. However, with the fast development of VLSI design, the achievement of sheer speed occurs much easier than before. As a result, the considerations for cost and security of cryptographic implementation start to play a more important role in many applications.

#### Speed

The most well-known and universal techniques used to speed up the hardware implementation are pipelining and parallel processing, which allow multiple blocks of data processed simultaneously. However, neither of them is suitable for the cipher feedback modes (e.g. CBC and CFB mode), as one iteration of the encryption/decryption process needs the results of the previous one.

Moreover, different schemes are often applied based on the concrete arithmetic operations required in a cryptographic algorithm. For example, modular exponential operation is key part in public-key cryptography as the operands are usually very large. For the sake of speed, the number of time-consuming modular multiplications should be reduced as many as possible. A systolic array for modular multiplication is presented using the algorithm of P. L. Montgomery in [16]. Some other speed-up methods include Barret-Booth's method and [3] and Brickell's algorithm [25].

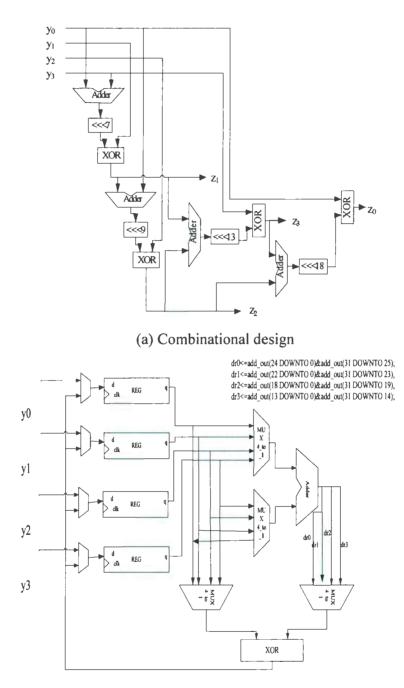

In some ciphers, such as Salsa20 and Phelix, which we implemented in hardware, the dominant cost operation is addition. Therefore, the subject of various adder structures is introduced and investigated in Chapter 4.

Many ciphers take advantage of S-boxes, an array lookup table using an

21

input-dependent index. A case in point is the AES algorithm. The contents of an S-box is the multiplicative inverse in Galois Field  $(2^8)$ , combined with an affine transformation over GF(2). Unfortunately, GF arithmetic approach yields up to 15 XOR gate delays [65] though it is area efficient. In most Gbps applications, a single look-up table is constructed. Till now, a twisted binary decision diagrams (TBDD) approach is the fastest reported so far [53], where the fanout of signals is distributed in all of the S-boxes.

Obviously numerous speed improvement methods may be done considering the properties of a specific algorithm.

#### • Cost ( area and power consumption)

"Cost" can mean different things in real life. However, when it comes to hardware implementation, it typically indicates chip area and power consumption. Sometimes, when subtle aspects are considered, "cost" may include the actual cost financially.

The first step to evaluate the area cost of a cipher is to define a metric for comparing digital logic. Traditionally, transistors are the atomic device in digital design. Table 2.1 provides the area complexity in terms of transistors for a standard cell library from [69].

| Components   | Transistors |

|--------------|-------------|

| 2-input NAND | 4           |

| 2-input AND  | 6           |

| 2-input XOR  | 12          |

| D Flip Flop  | 26          |

| 2:1 MUX      | 12          |

Table 2.1 Area complexity of CMOS standard cells

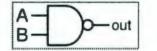

However, the popular metric nowadays is a count of the number of a standard two-input NAND gates that would be equivalent to the area of the design, since cell-based methodology makes it possible for hardware designers to focus on the high-level (logical function) aspect of digital-design. Table 2.2 is the truth table for NAND gate's behavior; Figure 2.5 is the NAND gate symbol that is in common use.

Table 2.2 The Truth Table of NAND Gate

| INP | UTS | OUTPUT   |

|-----|-----|----------|

| A   | В   | A NAND B |

| 0   | 0   | 1        |

| 0   | 1   | 1        |

| 1   | 0   | 1        |

| 1   | 1   | 0        |

Figure 2.5 NAND Gate Symbol

For most portable devices such as mobile phones, which run on battery, power consumption is a major concern, even more important than compactness requirement, because the development of the techniques for energy storage is far behind that for cell technology [43]. Another concern related to power consumption is the cooling system of the chip. For some futuristic applications like smart card, the chip runs at ultra-low power. Sequential logic is carefully employed since flip flops require a clock to drive them, which consumes extra power. The relative power consumption for various CMOS components is illustrated in Table 2.3.

| Components   | Normalized Power |

|--------------|------------------|

| 2-input NAND | 1                |

| 2-input AND  | 2.14             |

| 2-input XOR  | 3.36             |

| D Flip Flop  | 22.55            |

| 2:1 MUX      | 2.77             |

Table 2.3 Power Consumption of 0.18 µm CMOS Standard Cells [43]

The methods used to reduce power can be divided into two categories: technology-based approaches and architecture-based approaches. Technology-based approaches focus on reducing the voltage. It is well known that for a CMOS circuit, the

23

power dissipation is due to three aspects: dynamic power, short-circuit power and leakage power. Among them, dynamic power is the largest. It is given by the equation shown below:

$P_{dyamic} = N (f \times C_L \times V_{dd}^2)$ where f is the clock rate,  $C_L$  is the switched capacitance,  $V_{dd}$  is the supply voltage and N is the number of gate switches. Thus, power reduction can be achieved by voltage decrease.

However, Kakumu and Kinugawa's critical voltage provides an lower bound on the supply voltage [48]. Therefore, it is more attractive to make efforts on architectural improvement. Moreover, architecture-based approaches often make compensation for the reduced circuit speed that is due to the lower operating voltage (CMOS gate delay increases according to the voltage decrease).

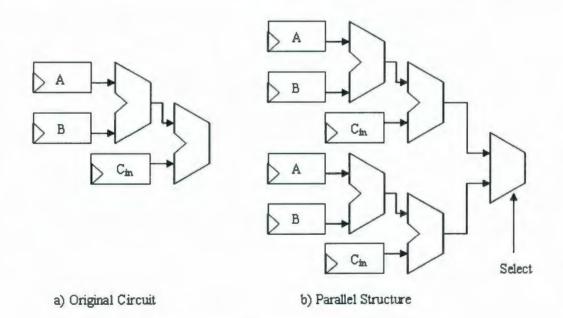

The authors of [4] illustrate several architectural methods. One of them is a parallel structure, which makes sacrifice in area. This can be seen from Figure 2.6.

Figure 2.6 Parallel Scheme for Power Reduction [4]

The circuit shown in Figure 2.6.b runs at half of the original frequency with the same throughput. It should be note that the power consumption is not doubled though it looks like that with a doubled circuit structure. Assuming the original power consumption is  $P_1$  = N  $(f_I \times C_{L1} \times V_{dd 1}^2)$ , then the new power assumption is  $P_2 = 2.15N (f_1/2 \times C_{L1} \times (0.58V_{dd 1})^2) \approx 0.36P_1$ .

#### • Security/ Implementation Attacks

In addition to implementation efficiency (i.e. speed and area), security is very important. Implementation or side channel attacks are targeted on the possible weaknesses in specific implementation platforms instead of in the algorithm. These attacks include power analysis [59] and fault attacks [38].

In 1996 Kocher et al. introduced the concept of a timing attack, which is one of the general classes in side-channel attacks, by measuring how much time different computations take to perform to reveal sensitive information. For example, with detailed knowledge of a cryptographic algorithm, it is sometimes possible to determine the length of the key by watching data transmission with the CPU. Two years later Kocher et al. [59] proved that the power consumption in a cryptographic circuit could reveal the secret information too. In [38], a comprehensive study at fault attacks is provided. In a fault attack, errors are injected to the cryptographic core, while the resulting outputs reflect the faults. Current methods to avoid fault attacks, especially on symmetric ciphers, include linear error-detecting codes, such as Reed-Solomon code [64]. Rather than focusing on the overall possible faults, they concentrate on a certain group of possible faults for practical reason.

However, side-channel attacks do not threaten stream ciphers as much as they do to block ciphers. This is because, in a stream cipher, the keystream process is typically independent of externally known data. In [15], the authors pointed out that side-channel attack related publications on stream ciphers have only aimed at RC4 stream cipher. Attacks on other stream ciphers, especially LFSRs based ones are not available in the public literature yet.

# 2.3 Software/Hardware Codesign

Considering the advantages and disadvantages of software and hardware implementations, it is believed that some hybrid co-designs can provide excellent performance while maintaining the flexibility. Smart cards that are used in secure financial applications and e-commerce is an example of software/hardware codesign. In a smart card, the most computationally intensive blocks run in targeted circuit to provide the speed and more physical security, and other blocks run on a general processor for flexibility.

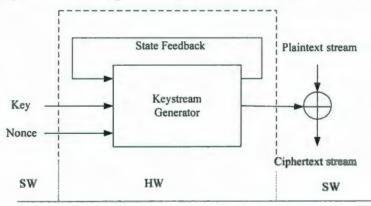

The main concern of co-designs is which parts of the cipher are mapped into hardware and software. There are two trends. One aims at adding hardware resources to a general purpose processor [45]. For example, a new instruction set is also added to the processor to facilitate cryptographic implementation. The other trend is to divide cryptographic algorithms into two stand-alone components; one runs on general processor and the other one runs on additional core. In [60], a stream cipher is modeled abstractly, as shown in Figure 2.7. It indicates that the stream cipher kernel and the iterated state variables are mapped into hardware (HW) while software (SW) provides the initial key and the nonce, which is often a pseudo-random number used only once. The keystream and the plaintext stream processing are also handled by software.

Figure 2.7 Example Scenario for a Stream Cipher [60]

FPGAs are practically attractive to use in co-designs. The overwhelming problem to resolve before implementing a software/hardware codesign is how to split the work between the general processor and the application specific circuit. This problem includes many aspects, some of which can be very subtle. However, the decisions on the work which is allocated to FPGAs are relatively simpler to make because of FPGAs' inherent flexibility. FPGAs are very suitable to process large amounts of data, which indicates that a complex computational component or a bus interface can be implemented in them.

A key factor in deciding how much computational task to assign to an FPGA is the "logic gate equivalence". It is the total number of logic gates that can work at the same time. Figure 2.8 shows a typical structure of FPGA logic block. However, in practice

26

many blocks will not work in a computation even if they are supposed to. It is largely because of improper routing, which is normally done by EDA tools instead of manually. The problem of routing problem for real implementation is studied by Inuani and Saul in [49].

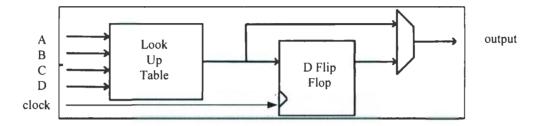

Figure 2.8 Typical FPGA Logic Block

One of the most attractive uses of FPGA in co-designs is the soft processors which can be configured to suit different applications. For example, the Virtex chips from Xilinx have 32-bit built-in soft processor known as MicroBlaze [52], which provides high speed hardware/software interfaces. This technique allows the designers to take an FPGA as a simple cross-compiler. In [36], the authors investigated the implementation of several most typical cryptographic algorithms based on MicroBlaze. They found that the flexibility offered by FPGAs can be used to notably increase the throughput of a software/hardware hybrid system.

# 2.4 Summary

This chapter addresses the methodologies and main concerns for software and hardware implementations, respectively. In addition, it draws analogies between typical FPGA and ASIC design processes.

Various trade-offs are very important. In software implementation, it is often reasonable to generate ciphertext for block cipher or keystream for stream cipher in blocks, whose size equals a multiple of the word size of the processor. As a result, the available bandwidth in the system can get optimum use.

Software inherently has the ability for fine-granular control on the internal configuration and behavior of a cryptographic algorithm by using particular instructions.

However, performing such operations would require extra memory and execution time which decrease the speed of the implementation. In hardware implementation, the typical trade-off concern is the speed-area tradeoff. Considering the pipeline structure in Figure 2.1, it is obvious that with more pipeline stages there is more speed gain but higher area consumption.

The following two chapters illustrate the details of our hardware designs for Phelix and Salsa20 stream ciphers. Both of the ciphers were claimed to be designed with the special emphasis on their suitability for not only software implementations but also hardware implementations.

# Chapter 3 Hardware Implementation of the Phelix Stream Cipher

# 3.1 Introduction of Phelix Stream Cipher

Phelix [22] is claimed to be a high-speed stream cipher. It is selected for both software and hardware performance evaluation by the eSTREAM project. The cipher supports an 8-bit to 256-bit length key and a 128-bit nonce to generate the keystream bits. The plaintext is incorporated during the computation to produce a built-in Message Authentication Code (MAC).

Our goal in implementing Phelix is to find out a reasonable synthesis result for two extreme situations: the compactness it can achieve without considering the throughput; the speed/throughput it can achieve without considering the area. Since circuits implemented in FPGAs are at least ten times larger and three times slower than the custom implementations [67], we have chosen ASIC-based approach to implement the two proposed designs for Phelix: compact Phelix implementation and high speed implementation. The basic features underlying FPGAs are explored in the next chapter that introduces various structures for Salsa20 as the property of Salsa20 is more suitable for a FPGA-based implementation, such as a relatively big requirement for memory compared with some popular stream ciphers.

It should be noted that in block diagrams representing the designs, the input and output are not real I/Os in a system. The designs are core based and the input and output could be internally interfaced with external circuits.

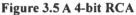

# 3.1.1 Algorithm

Phelix is targeted at 32-bit platforms. It is composed of simple operations: addition modulo  $2^{32}$ , exclusive or, and rotation by a fixed number of bits. There are 5 words that are updated during each round, and 4 "old" words are stored in memory to be used in the keystream output function.

One block that produces one word of keystream consists of two "half-block" functions

H, which is defined as:

```

Function H(w_0, w_1, w_2, w_3, w_4, K_0, K_1)

Begin

w_0 := w_0 \boxplus (w_2 \oplus K_0); \quad w_2 := w_3 \lll 15;

w_1 := w_1 \boxplus w_4; \quad w_4 := w_4 \lll 25;

w_2 := w_2 \oplus w_0; \quad w_0 := w_0 \lll 9;

w_3 := w_2 \oplus w_1; \quad w_1 := w_1 \lll 10;

w_4 := w_4 \boxplus w_2; \quad w_2 := w_2 \lll 17;

w_0 := w_0 \oplus (w_2 \boxplus K_1); \quad w_3 := w_3 \lll 30;

w_1 := w_1 \oplus w_4; \quad w_4 := w_4 \lll 13;

w_2 := w_2 \boxplus w_0; \quad w_0 := w_0 \lll 20;

w_3 := w_3 \boxplus w_1; \quad w_1 := w_1 \lll 11;

w_4 := w_4 \oplus w_2; \quad w_2 := w_2 \lll 5;

Return (w_0, w_1, w_2, w_3, w_4);

End.

```

**Figure 3.1 H Function**

The bitwise exclusive-or of two words, denoted as " $\oplus$ ", is the sum of the words with carries suppressed. The symbol "<<?" represents left rotation, and " $\boxplus$ " represents addition modulo  $2^{32}$ .

During the encryption, defining one step as a complete step for Phelix to update five active state words ( $w_0$ ,  $w_1$ ,  $w_2$ ,  $w_3$ ,  $w_4$ ), at i<sup>th</sup> step, two 32-bit secret subkeys ( $X_{i,0}$ ,  $X_{i,1}$ ) and one plaintext word  $P_i$  are applied to executions of the H function. The generation of the subkeys is introduced in Section 3.3.5.

Selected details of the algorithm will be discussed in the analysis of Phelix cipher main components. For more insight of those components, refer to the initial paper [22].

# 3.1.2 Security

The authors of Phelix claimed that there is no attack against Phelix with less than 2<sup>128</sup> operations. Actually, Phelix is a strengthened version of an earlier cipher, Helix [55], which was targeted by two attacks in 2004. One is an adaptive chosen-plaintext attack created by Muller [26]. The other one was also published by Muller, which is a distinguishing attack [26]. The Phelix primitive was largely motivated to increase the security against the distinguishing attack. It expands Helix's 160-bit internal state to 288 bits.

However, in November 2006, Hongjun Wu and Bart Preneel published a paper titled "Differential Attacks against Phelix" [35]. This paper was largely derived from the differential attack against Helix stream cipher to recover the key. Their work mainly aims at weak nonces and keys. They concluded that Phelix fails to strengthen Helix since the computational complexity of the attack is much less than that of the attack against Helix. However, a good cipher does not imply absolute security, and the confidence level in the amount of security is not merely dependent on several results of attacks. Selecting a potential prevalent cipher is even more complicated, and security is only one consideration among a large pool.

# **3.1.3 Previous Work on Hardware Implementation on Phelix**

Until now there has been insufficient work on the hardware implementations of the candidate stream ciphers proposed for eSTREAM project. Most discussion and comparison focus on cryptanalysis. However, the authors of [68] demonstrated the FPGA performance of Phelix. The results are shown in Table 3.1. In order to avoid specific metric for individual devices, the authors of [68] chose the number of equivalent gates to measure area, where one gate is a two-input NAND gate (6 transistors).

|             |        | Throughput | Gate     | Implementation                                         |

|-------------|--------|------------|----------|--------------------------------------------------------|

| Xilinx Chip | Slices | Mbit/s     | Equiv    | Description                                            |

|             |        |            | Estimate |                                                        |

| XC2S100-5   | 1198   | 960.0      | 20404    | (A) full-round 160-bit design, as per developers paper |

| XC2S100-5   | 1077   | 750.0      | 18080    | (B) half-round 160-bit design                          |

| XC2S30-5    | 264    | 3.2        | 12314    | (C) 32-bit data path                                   |

Table 3.1 FPGA Hardware performance of Phelix [68]

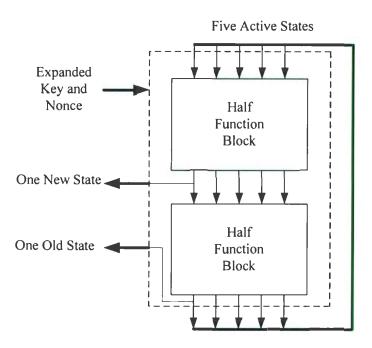

The software/hardware codesign of Phelix has been studied in an undergraduate course at Virginia Tech called "Introduction to Codesign" [60]. They implement two identical half function blocks as the hardware component.

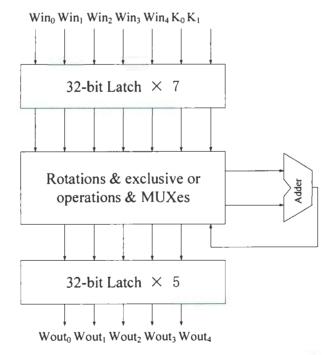

Figure 3.2 Block Diagram of Hardware Accelerator for Phelix

The hardware design of one student group shown in Figure 3.2 is of pure combinational logic, which can accomplish one state updating process in a single clock cycle, and leave the whole control complexity in software.

Another two teams are more aggressive since the one implemented a half block as the basic iterative H function circuit, and the other one implemented eight double H function blocks as a parallel structure to relieve the communication bottleneck between software and hardware. Obviously, the synthesis result for the eight-full-H-block is quite large. A careful trade-off decision should be made. Table 3.2 shows the results for those three structures. All of them are implemented targeted on Xilinx Spartan3e FPGAs.

| Table | 3.2 | Results | of Phelix | Co-design |

|-------|-----|---------|-----------|-----------|

|-------|-----|---------|-----------|-----------|

| Version       | Area (slices) | Frequency(MHz) |

|---------------|---------------|----------------|

| 8x Full Block | 4301          | 7.7            |

| Full Block    | 1190          | 48.6           |

| Half Block    | 459           | 76             |

Unfortunately, the results are not good for comparison since the authors only provide the frequency instead of the throughput.

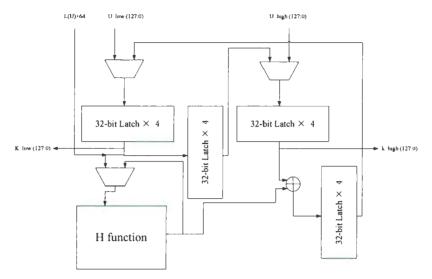

# **3.2 Compact ASIC Structure of Phelix**

# **3.2.1 Top Level Design**

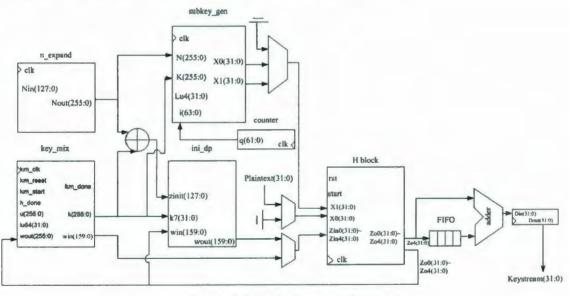

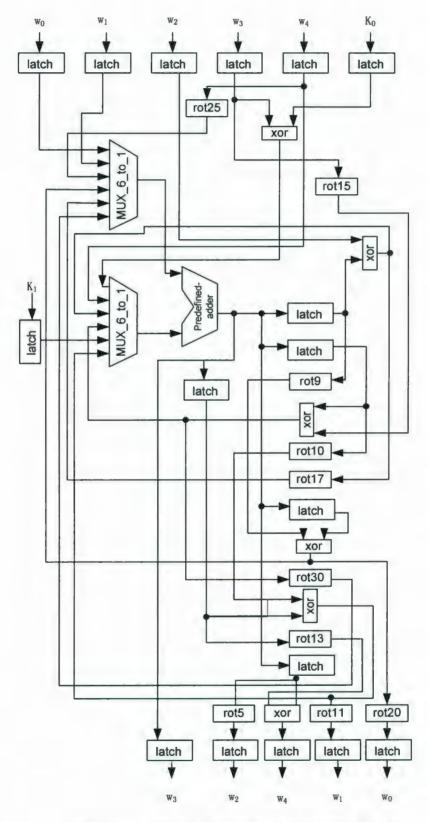

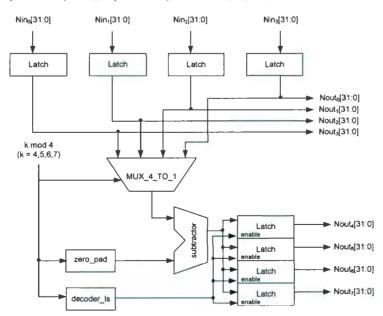

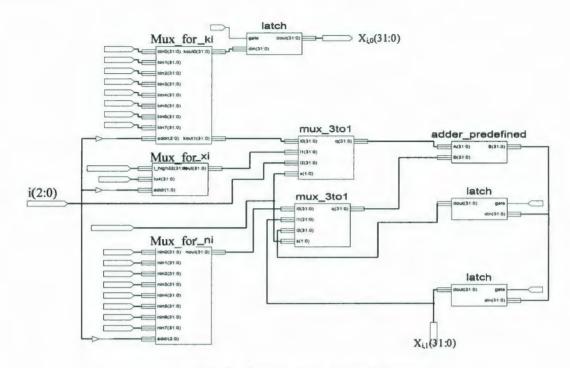

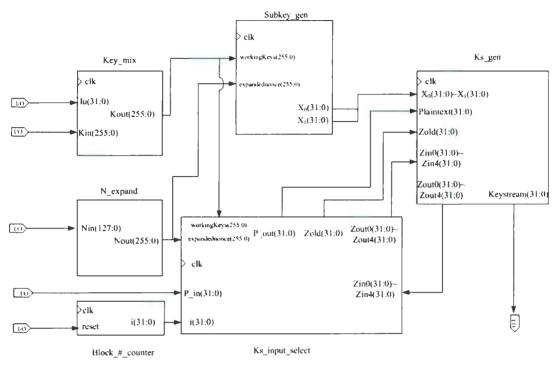

The Phelix stream cipher can be implemented in many ways. The proposed compact structure focuses on function sharing to optimize the area. Figure 3.3 illustrates a minimal ASIC implementation consisting of one round of encryption and a memory recording the four old states. The specifications of the main blocks are given below:

n\_expand: converts a 128-bit input nonce to the 256-bit working nonce.

key\_mix: converts a variable-length input key to the fixed-length working key.

subkey\_gen: generates subkeys  $X_{i,0}$ ,  $X_{i,1}$  for each block.

**ini\_dp**: decides the input of H\_func. For the first eight blocks (initialization phase), the generated keystream is discarded.

**H** block: performs function H  $(w_0, w_1, w_2, w_3, w_4, K_0, K_1)$ .

FIFO: the "first in, first out" memory that stores the old states.

**Figure 3.3 Phelix Compact Structure**

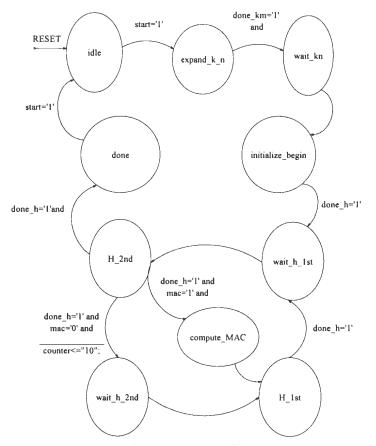

The top level controller can be presented by a finite state machine shown in Figure 3.4. When the system is turned on with the power plugged in or the *Reset* signal is triggered, the controller transfers to *Idle* state. When the *start* signal is asserted, the encryption circuit starts to work.

Figure 3.4 State Diagram of the Top Level Controller

The specifications of the states are given below:

expand\_kn: Convert a input key/nonce to the fixed-length working key/nonce.

**wait\_kn**: While stopping *key\_mix* block and *n\_expand* block, enable *subkey\_gen* block, putting the first old state into the FIFO.

initialize\_begin: Set the initial five states of the H function, and enable the counter, which provides the block number.