# IMPLEMENTATION OF SELECTED CRYPTOGRAPHIC ALGORITHMS ON A RECONFIGURABLE MICROPROCESSOR PLATFORM

CENTRE FOR NEWFOUNDLAND STUDIES

TOTAL OF 10 PAGES ONLY MAY BE XEROXED

(Without Author's Permission)

ANDREW L. COOK

National Library of Canada

Acquisitions and Bibliographic Services

395 Wellington Street Ottawa ON K1A 0N4 Canada

Bibliothèque nationale du Canada

Acquisisitons et services bibliographiques

395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-612-93019-X Our file Notre référence ISBN: 0-612-93019-X

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur a accordé une licence non

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it. may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou aturement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this dissertation.

While these forms may be included in the document page count, their removal does not represent any loss of content from the dissertation.

Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de ce manuscrit.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manguant.

# IMPLEMENTATION OF SELECTED CRYPTOGRAPHIC ALGORITHMS ON A RECONFIGURABLE MICROPROCESSOR PLATFORM

BY

© ANDREW L. COOK

A Thesis submitted to the School of Graduate Studies in partial fulfillment of the requirements for the degree of Master of Engineering

# FACULTY OF ENGINEERING AND APPLIED SCIENCE MEMORIAL UNIVERSITY OF NEWFOUNDLAND

September 2003

Newfoundland

#### Abstract

This research was performed to evaluate the cryptographic capabilities of the Chameleon CS2112 Reconfigurable Communications Processor. The CS2112 is a processor architecture which closely couples a general purpose microprocessor with a specialized reconfigurable core.

To evaluate the architecture, five cryptographic algorithms were chosen for implementation. The first algorithm, the Data Encryption Standard (DES), was the United States National Cryptographic Standard from 1977 until 2001 and has been the most widely used cryptographic algorithm in computing and communications environments. DES's successor, the Advanced Encryption Standard (AES or Rijndael) which was chosen in the fall of 2000, was also implemented. Since the CS2112 is targeted toward wireless communications applications the other three algorithms - E0, KASUMI, RC4 - were chosen as they are currently used to provide security in common wireless protocols. The Bluetooth protocol, developed to provide a cheap and easy method for users to create wireless connections between devices, uses E0 to secure connections. The RC4 algorithm is part of the 802.11b wireless data communications standard and KASUMI forms an integral part of the authentication and privacy portions of the 3rd Generation GSM cell phone standard.

DES and AES were fully implemented on the CS2112 and a working executable application was developed. Our efforts to exploit the parallelism and pipelining capability of the CS2112 and multiple implementations are described for these two algorithms. The maximum throughputs for the DES and AES implementations were

found to be 322.5 Mbits/sec and 1.1 Gbits/sec respectively. Also, although complete implementations were not finalized, preliminary implementations for E0, KASUMI, and RC4 were developed with a view to allow performance estimates to be made and provide a basis for future work.

The Chameleon CS2112 implementations of the above algorithms performed respectably and the architecture could be useful in cryptographic applications. However, the architecture does constrain design size considerably. Unfortunately, the CS2112 is no longer commercially available since Chameleon Systems Inc. has ceased operations. However, this architecture, with some modifications, could be used as the basis for a new general cryptographic accelerator.

#### Acknowledgments

This thesis owes its existence to the encouragement, support and inspiration of many people. Firstly, I would like to thank my supervisors, Dr. Howard Heys and Dr. R. Venkatesan, for their guidance and support through the course of my studies and research. Secondly, I would like to thank Chameleon Systems Inc. and Mark Rollins for their financial and technical support. As well, I would like to thank all of my friends and colleagues, most notably Darrell and Jason, for keeping me focused on my work. Last, but not least, I would like to thank my family for their encouragement and support throughout my university years; without them none of this would have been possible.

### Contents

| A                | bstra  | ct     |                                                   | ii  |

|------------------|--------|--------|---------------------------------------------------|-----|

| A                | ckno   | wledgr | nents                                             | iv  |

| $\mathbf{T}_{i}$ | able ( | of Con | tents                                             | v   |

| Li               | st of  | Table  | s                                                 | ix  |

| Li               | st of  | Figur  | es                                                | x   |

| Li               | st of  | Abbro  | eviations and Symbols                             | xii |

| 1                | Inti   | oducti | ion                                               | 1   |

| 2                | Cry    | ptogra | aphy Overview and Selected Algorithm Descriptions | 6   |

|                  | 2.1    | Crypt  | ography                                           | 7   |

|                  |        | 2.1.1  | Private Key Block Ciphers                         | 8   |

|                  |        | 2.1.2  | Stream Ciphers                                    | 9   |

|                  | 2.2    | Data I | Encryption Standard                               | 10  |

|                  | 2.3    | Advar  | nced Encryption Standard                          | 13  |

|                  |        | 2.3.1  | Byte Substitution                                 | 14  |

|                  |        | 2.3.2  | Row Shift                                         | 14  |

|                  |        | 2.3.3  | Column Mixing                                     | 15  |

|                  |        | 2.3.4  | Key Addition                                      | 15  |

|   |     | 2.3.5  | Rijndael Operation                                    | 15 |

|---|-----|--------|-------------------------------------------------------|----|

|   | 2.4 | Blueto | oth Encryption Algorithm - E0                         | 16 |

|   | 2.5 | KASU   | MI                                                    | 18 |

|   |     | 2.5.1  | Function $FL$                                         | 19 |

|   |     | 2.5.2  | Function $FI$                                         | 20 |

|   |     | 2.5.3  | Function $FO$                                         | 20 |

|   |     | 2.5.4  | Key Scheduling Algorithm                              | 21 |

|   | 2.6 | RC4    |                                                       | 21 |

| 3 | Cry | ptogra | phic Algorithm Implementation                         | 23 |

|   | 3.1 | Recon  | figurable Processor Architectures                     | 25 |

|   |     | 3.1.1  | Microprocessor Architecture                           | 28 |

|   |     | 3.1.2  | Logic Block Granularity                               | 28 |

|   |     | 3.1.3  | Data Interconnection                                  | 30 |

|   |     | 3.1.4  | Reconfiguration Models                                | 31 |

|   |     | 3.1.5  | Programming Models                                    | 33 |

|   | 3.2 | Recon  | figurable Computing and Cryptographic Hardware        | 35 |

| 4 | The | e Cham | neleon CS2112 Reconfigurable Communications Processor | 39 |

|   | 4.1 | Cham   | eleon CS2112 Architecture                             | 39 |

|   |     | 4.1.1  | Datapath Units                                        | 40 |

|   |     | 4.1.2  | Multipliers                                           | 41 |

|   |     | 4.1.3  | Local Store Memories                                  | 42 |

|   |     | 4.1.4  | Control Logic Units                                   | 42 |

|   |     | 4.1.5  | Data Path and Control Routing                         | 42 |

|   | 4.2 | CS211  | 2 Design Methodology                                  | 43 |

|   |     | 4.2.1  | Software Model                                        | 44 |

|   |     | 122    | Decim Phace                                           | 45 |

|   |      | 4.2.3   | Synthesis and Mapping Phase        | 47 |

|---|------|---------|------------------------------------|----|

|   |      | 4.2.4   | Integration and Verification Phase | 48 |

| 5 | Dat  | a Enci  | ryption Standard Implementation    | 50 |

|   | 5.1  | Iterati | ive Kernel                         | 51 |

|   |      | 5.1.1   | Architecture Description           | 51 |

|   |      | 5.1.2   | Synthesis and Mapping              | 59 |

|   |      | 5.1.3   | Testing and Performance            | 60 |

|   | 5.2  | Multip  | ple Pipelined Kernel               | 60 |

|   |      | 5.2.1   | Architecture Descriptions          | 62 |

|   |      | 5.2.2   | Synthesis and Mapping              | 65 |

|   |      | 5.2.3   | Testing and Performance            | 66 |

|   | 5.3  | Pipeli  | ned Kernel                         | 67 |

|   |      | 5.3.1   | Architecture Description           | 67 |

|   |      | 5.3.2   | Synthesis and Mapping              | 69 |

|   |      | 5.3.3   | Testing and Performance            | 70 |

|   | 5.4  | Summ    | nary                               | 71 |

| 6 | Rijr | ndael I | mplementation                      | 72 |

|   | 6.1  | Iterati | ve Kernel                          | 73 |

|   |      | 6.1.1   | Synthesis and Mapping              | 76 |

|   |      | 6.1.2   | Testing and Performance            | 76 |

|   | 6.2  | Pipelin | ned Kernel                         | 77 |

|   |      | 6.2.1   | Synthesis and Mapping              | 80 |

|   |      | 6.2.2   | Testing and Performance            | 8. |

|   | 6.3  | Summ    | ary                                | 8. |

| 7 | Blu  | etooth  | , KASUMI and RC4                   | 82 |

|   | 7 1  | Pluoto  | ooth Encryption Algorithm FO       | Q. |

|                           | 7.2   | KASUMI                               | 85  |

|---------------------------|-------|--------------------------------------|-----|

|                           | 7.3   | RC4                                  | 90  |

|                           | 7.4   | Summary                              | 94  |

| 8                         | Con   | clusions                             | 95  |

| Li                        | st of | References                           | 99  |

| $\mathbf{A}_{\mathbf{j}}$ | ppen  | dicies                               | 106 |

| A                         | Ver   | ilog Examples                        | 107 |

|                           | A.1   | Rotate 11 bits Left Module           | 107 |

|                           | A.2   | Pipelined Rotate 11 bits Left Module | 108 |

| В                         | Cha   | ameleon Preprocessor Example         | 110 |

|                           | B.1   | Original Code                        | 110 |

|                           | B.2   | Chameleon Preprocessor Output        | 111 |

| $\mathbf{C}$              | IP I  | Data Path Verilog Module             | 113 |

| D                         | Tes   | bench Examples                       | 123 |

|                           | D.1   | Verilog Testbench                    | 123 |

|                           | T) 0  | C Touthonoh                          | 194 |

## List of Tables

| 2.1 | DES S-Box S1                                       | 11         |

|-----|----------------------------------------------------|------------|

| 2.2 | E Expansion                                        | 12         |

| 2.3 | P Permutation                                      | 13         |

| 2.4 | Number of Rounds in Rijndael                       | 13         |

| 2.5 | Rijndael Row Shifts                                | 14         |

| 2.6 | LFSR Feedback Polynomials                          | 18         |

| 3.1 | Cipher Performance Figures                         | 37         |

| 5.1 | Iterative Kernel Resource Utilization              | 60         |

| 5.2 | IP Kernel Resource Utilization                     | <b>6</b> 5 |

| 5.3 | SRK Kernel Resource Utilization                    | 65         |

| 5.4 | IP <sup>-1</sup> Kernel Resource Utilization       | 66         |

| 5.5 | Pipelined Kernel Resource Utilization              | 69         |

| 6.1 | Resource utilization for iterative Rijndael design | 76         |

| 6.2 | Resource utilization for pipelined Rijndael design | 80         |

# List of Figures

| 2.1 | Block Cipher Modes of Operation                                   | ) |

|-----|-------------------------------------------------------------------|---|

| 2.2 | Stream Cipher Operation                                           | ) |

| 2.3 | DES Structure                                                     | Ĺ |

| 2.4 | DES F-Function                                                    | 2 |

| 2.5 | Example of STATE for a block size of 128 bits                     | 1 |

| 2.6 | Rijndael Encryption                                               | 3 |

| 2.7 | Bluetooth Stream Cipher                                           | 7 |

| 2.8 | E0                                                                | 7 |

| 2.9 | KASUMI Algorithm                                                  | 9 |

| 3.1 | Xilinx XC3000 Series Configurable Logic Block                     | 9 |

| 3.2 | CS2112 Example                                                    | 0 |

| 3.3 | Segmented (A) and Hierarchial Routing (B) Examples                | 1 |

| 3.4 | Ideal Software Development Environment for Coupled Reconfigurable |   |

|     | Devices                                                           | 4 |

| 4.1 | CS2112 High Level Architecture                                    | 0 |

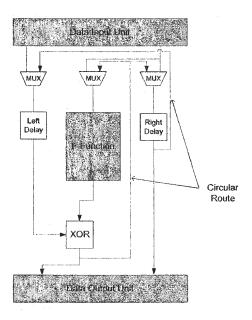

| 4.2 | CS2112 DPU                                                        | 1 |

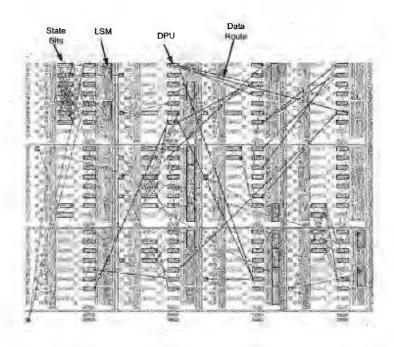

| 4.3 | CS2112 Fabric Routes                                              | 3 |

| 4.4 | Design Flow                                                       | 4 |

| 4.5 | Single DPU Rotate Left by 11 Bits                                 | 7 |

| 4.6 | Pipelined Rotate Left by 11 Bits                                  | 7 |

| 4.7 | $C \sim Side^{TM}$ Graphical Floorplanner                         | 8 |

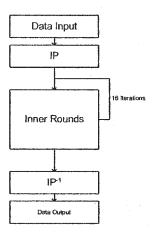

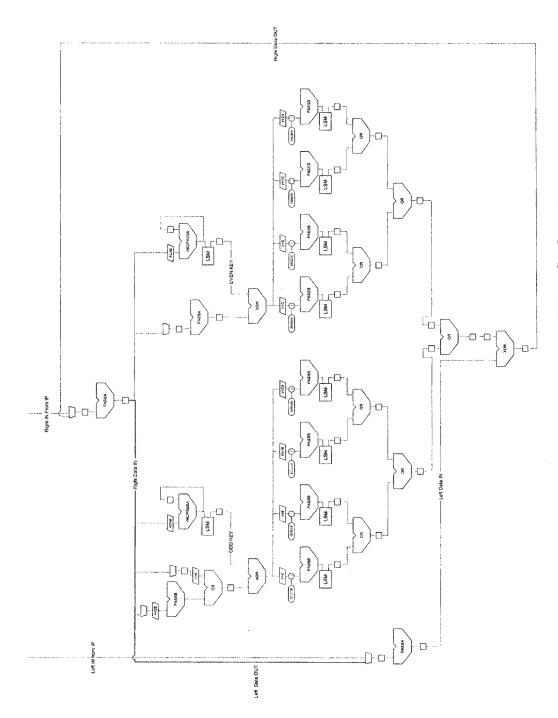

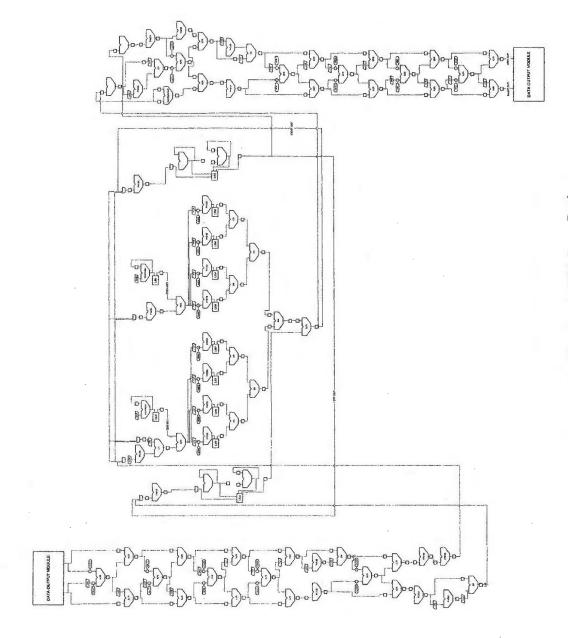

| 5.1  | Iterative DES Kernel                                         | 50 |

|------|--------------------------------------------------------------|----|

| 5.2  | Iterative DES Kernel Blocks                                  | 52 |

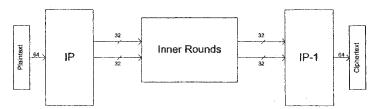

| 5.3  | Example Hardware Mapping for a Subset of IP Stage Pseudocode | 54 |

| 5.4  | IP Hardware Configuration                                    | 55 |

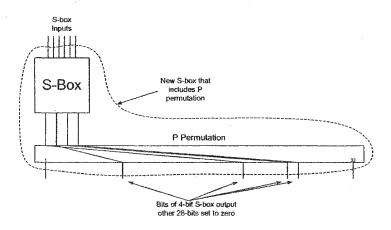

| 5.5  | S-box and P Permutation Combination                          | 56 |

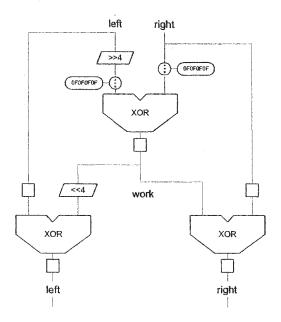

| 5.6  | DES Round Function Block Diagram                             | 57 |

| 5.7  | DES Round Function Fabric Configuration                      | 58 |

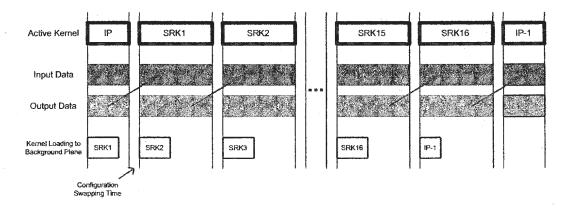

| 5.8  | Pipelined Multi-Kernel DES Kernel Swapping                   | 61 |

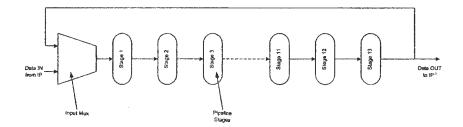

| 5.9  | Circular Pipeline Concept                                    | 63 |

| 5.10 | SRK Delay Illustration                                       | 64 |

| 5.11 | Pipelined DES Data Path                                      | 68 |

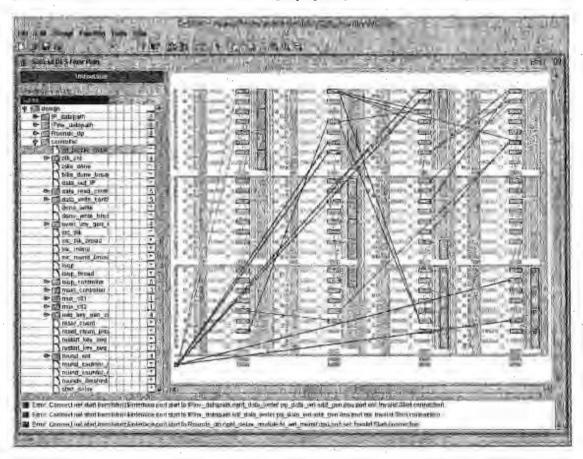

| 5.12 | Pipelined DES Floorplan                                      | 70 |

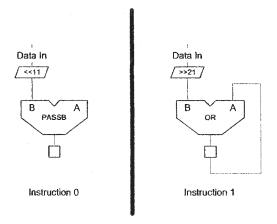

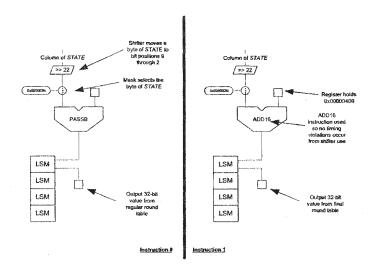

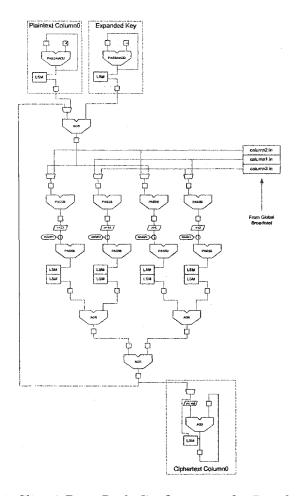

| 6.1  | Table Address Generator Instructions                         | 74 |

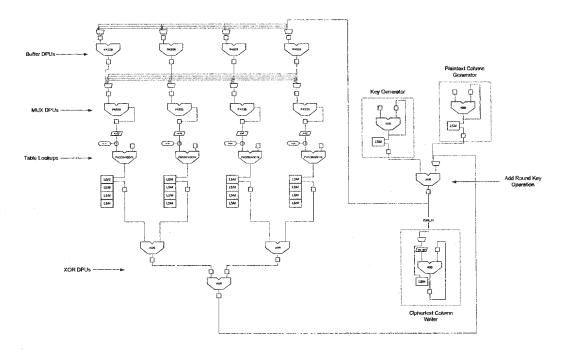

| 6.2  | Iterative Rijndael Kernel Data Path Configuration            | 75 |

| 6.3  | Iterative Rijndael kernel floorplan                          | 76 |

| 6.4  | Pipelined Table Address Generator Instructions               | 78 |

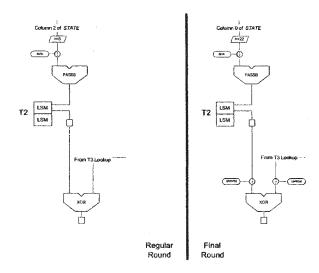

| 6.5  | Slice 0 Data Path Configuration for Regular Round            | 79 |

| 6.6  | Pipelined Rijndael kernel floorplan                          | 80 |

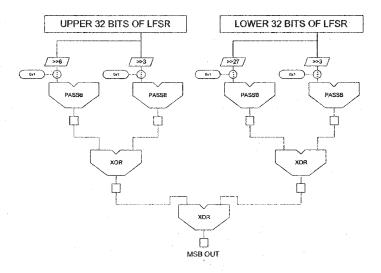

| 7.1  | MSB Generation Data Path Structure                           | 84 |

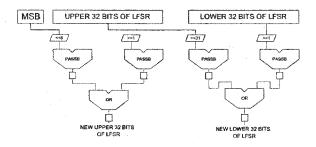

| 7.2  | Shifting LFSR and Combining with New MSB                     | 85 |

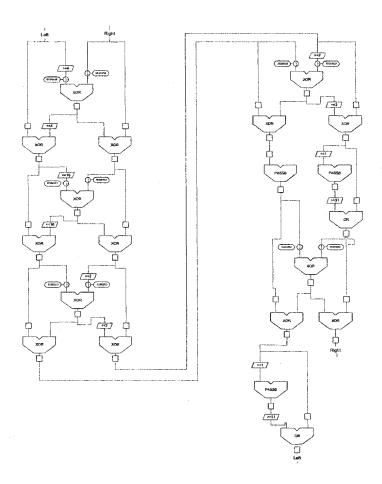

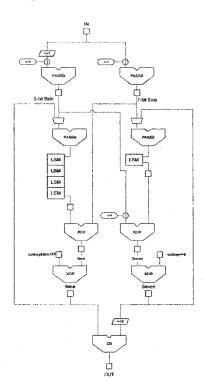

| 7.3  | FI Subfunction                                               | 86 |

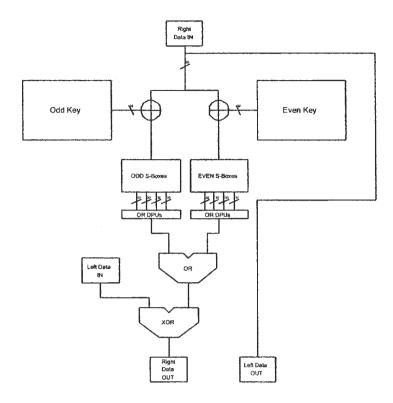

| 7.4  | KASUMI FO Subfunction                                        | 88 |

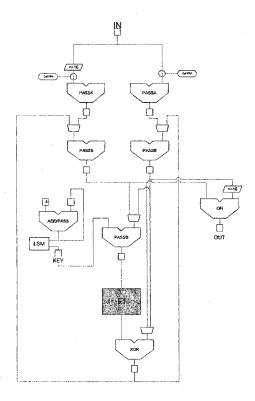

| 7.5  | KASUMI $FL$ Subfunction                                      | 89 |

| 7.6  | Full KASUMI Data Path                                        | 90 |

| 7.7  | Iterative RC4 Kernel High Level Diagram                      | 91 |

| 7.8  | RC4 Operation Timing                                         | 93 |

#### List of Abbreviations and Symbols

3GPP 3rd Generation Partnership Project

**AES** Advanced Encryption Standard

ALU Arithmetic Logic Unit

ARC Argonaut RISC Core

ASIC Application Specific Integrated Circuit

ATM Automated Teller Machine

CBC Cipher Block Chaining

**CLB** Configurable Logic Block

CLU Control Logic Unit

CSM Control State Memory

**DES** Data Encryption Standard

DPU Data Path Unit

ECB Electronic Code Book

FPGA Field Programmable Gate Array

FSM Finite State Machine

LFSR Linear Feedback Shift Register

LSM Local Store Memory

LUT Lookup Table

MUL Multiplier Unit

MSB Most Significant Bit

NIST United States National Institute of Standards and Technology

NSA United States National Security Agency

**OFB** Output Feedback

PIO Programmable I/O

PLA Programmable Logic Array

RFU Reconfigurable Functional Unit

RISC Reduced Instruction Set Computer

SAGE Security Algorithms Experts Group

SoC System On Chip

SRK Single Round Kernel

SIMD Single Instruction Multiple Data

#### Chapter 1

#### Introduction

I can add colors to the chameleon,

Change shapes with Proteus for advantages,

And set the murderous Machiavel to school.

William Shakespeare, King Henry VI Pt. III

At the beginning of 2003 there were more than 170 million hosts connected to the Internet and this number is expected to surpass the 200 million mark by the end of the year [1]. However, demand is also growing from a user's perspective, not just for simple Internet connectivity, but also for high bandwidth, permanent connections. Gone are the days of dialing into a pool of modems at your local Internet service provider. Now, high speed data connection technologies offered by telecommunications and cable companies can give people a permanent link to the Internet in their homes making it a part of daily life for many people. This growth has, in turn, fuelled higher bandwidth demands from business. Online shopping and banking have become as commonplace as going to the market to buy bread or going to a bank to pay bills.

Alongside the growing use of the Internet has come another trend - the desire for mobility. The wireless market worldwide is over a 120 billion dollar industry and it is estimated that by 2006 there will be 64 million mobile Internet subscribers [2]. This estimate does not include the users of devices employing technologies such as WiFi

(or 802.11b) or Bluetooth that allow easy setup of wireless local area networks in homes and allow printers to be connected to a PC without a cable. The speed and range of wireless devices is also constantly improving as new standards are developed. For example, the 802.11b standard supports data rates of up to 11Mbps whereas the 802.11g standard, which is currently under development, will support data rates of up to 54Mbps at a similar range. Such developments have the potential to make wired connectivity a thing of the past.

A result of these two trends is the need for improved security. Internet users, for instance, worry about hackers gaining access to their credit card information from an online store's database or wonder if somebody connected to their network was observing the purchase they just made. If they are using a wireless connection, a malicious user could be observing their transactions from a great distance using a sensitive antenna. In 1990 CERT [3] recorded only 252 security related incidents on the Internet. But by 2002 this number had swollen to over 80,000 with another 40,000 in only the first quarter of 2003 [4]. Of course, many more incidents were not recorded. Although most new communications protocols now include some mechanism for providing authentication, data integrity and privacy, the demand for more bandwidth requires the development of new cryptographic algorithms and devices that can keep up at higher speeds. As well, wireless connectivity adds the extra complication of low power usage on system designers.

To meet the needs of the market, the communications industry has been changing rapidly over the last two decades. For example, Ethernet connection speeds have moved from 2.94Mbps to now 1Gbps and soon 10Gbps [5]. System designers are now turning to hardware devices more than ever to meet the demanding requirements of the communications industry. To achieve these changes, designers have also been frequently turning to configurable devices, such as Field Programmable Gate Arrays (FPGAs), to improve their time to market and lower their development costs. As well,

such devices can be reconfigured as standards and requirements evolve. However, custom Application Specific Integrated Circuits (ASICs) are still used for the highest speed applications where large volume production is expected.

In recent years, researchers have begun coupling a general purpose microprocessor with reconfigurable logic in order to gain the benefits of a hardware implementation while still having the flexibility of software. In a rapidly changing market this is a definite advantage. Initial research into reconfigurable microprocessors began at a university level. Such systems began at the board level with a microprocessor externally linked to an FPGA [6][7]. Over time, however, architectures began to evolve in which the processor and reconfigurable logic resided on the same chip [8][9][10]. As well, such architectures recently began to appear commercially when companies such as Triscend, BOPS and Chameleon Systems released reconfigurable microprocessors to the market. Unfortunately, many of the companies offering reconfigurable microprocessor devices, including BOPS and Chameleon Systems, are no longer operating. A probable reason for their demise was their inability to provide the necessary development tools to easily take advantage of the technology. Although they were able to "add colours to the chameleon, and change shapes with Proteus", it was not enough to become a king.

#### Motivation, Scope and Organization of Research

In the Fall of 2000, Chameleon Systems Inc. proposed that researchers at Memorial University of Newfoundland, led by Dr. Howard Heys and Dr. R. Venkatesan, study the suitability of their new product for cryptographic algorithms. The Chameleon Systems CS2112 RCP chip was considered the industry's first reconfigurable processor targeted at communications applications. Although designed for protocol processing and signal processing, potential cryptographic capabilities would further its suitability for communications applications. A number of cryptographic algorithms that are part

of current communications standards were selected for implementation on the CS2112. In total, five cryptographic algorithms were chosen for implementation, including the Data Encryption Standard (DES), a widely used cryptographic standard released in 1977, and its successor the Advanced Encryption Standard (AES) which was finalized in 2001. As well, the algorithms E0, KASUMI and RC4 which are all utilized in current wireless protocols were chosen since the CS2112 is targeted toward wireless communications applications. The goal was to implement the chosen algorithms in hardware so as to achieve a performance increase over pure software implementations. Chameleon Systems provided Memorial with their proprietary set of design tools as well as a development board for testing the resulting designs. Although the company stopped production of the CS2112 in early 2002, Chameleon Systems still provided technical support as needed. In early 2003, Chameleon Systems Inc. ceased operations but all major research was completed before this occurred.

The following is an outline of the research presented in the following chapters:

- Chapter 2 presents a brief overview of cryptography as well as descriptions of the algorithms selected for implementation on the CS2112.

- Chapter 3 provides some background in the field of reconfigurable computing and some recent results using such hardware for cryptographic purposes.

- Chapter 4 details the Chameleon CS2112 processor architecture and gives the reader insight into the design methodology used when implementing algorithms on the CS2112.

- Chapter 5 describes research efforts related to the implementation of the Data Encryption Standard.

- Chapter 6 presents efforts in the development of Advanced Encryption Standard functions on the CS2112.

- Chapter 7 details some preliminary design work completed with three other ciphers used in current communications standards the Bluetooth encryption algorithm E0, KASUMI, and RC4.

- Chapter 8 summarizes the results of this research and provides recommendations for future work.

#### Chapter 2

# Cryptography Overview and Selected Algorithm Descriptions

Cryptography, from the Greek kryptos meaning hidden and graphein meaning to write, is the art and science of making communications unintelligible to all except the intended recipient(s). Cryptographic techniques attempt to protect information by altering its form. The origins of secret writing can be traced back nearly four millennia to the hieroglyphic writing system of the Egyptians [11]. Until recently, the use of cryptographic methods to secure communication has been within the realm of governments and has been directed by their associated national cryptographic services. With the steady growth of the Internet and the ever-increasing private use of communications channels comes the need for public cryptographic standards. Without such standards, users are forced to improvise on their own which can lead to relatively insecure cryptographic methods being employed. The following sections provide a brief overview of some cryptographic principles as well as descriptions of the cryptographic algorithms studied in this research.

#### 2.1 Cryptography

As stated above, cryptography protects information by making it unreadable to all but the authorized parties. Encipherment  $(E_k)$  is the process whereby the original text, called the plaintext (P), is replaced by random-looking text called the ciphertext (C). Both texts are composed of a concatenation of symbols from an alphabet. Decipherment  $(D_k)$  is the process whereby C is transformed back into the original P. Notationally:

$$P \xrightarrow{E_k} C \xrightarrow{D_k} P$$

A cryptographic system is a family of transformations on plaintexts. The members of the family are indexed by a parameter called the key, k. Typically, the key is a sequence of symbols from an alphabet and the associated transformation  $E_k$  (or  $D_k$ ) is an algorithm determined by k. A key is used since it is much simpler to change a key than to change the entire algorithm used to protect the data.

There are two general classifications for cryptographic algorithms: Public Key and Private (or Symmetric) Key [12]. In public key cryptography, the sender uses a publicly known key generated by the receiver to encrypt a secret message before sending it through an insecure communications channel. The receiver then uses a combination of a private key, known only to them, and the public key to decrypt the message. In general, public key algorithms are much more computationally intensive than private key algorithms since the former rely on the principle that it is infeasible to find the private key given the public key. If otherwise, it would be trivial for an attacker to decode the secret message. One example of such a suspected computationally infeasible problem used by public key algorithms is the factorization of a number composed solely of two very large prime numbers. The best known public key algorithm is RSA which was invented by Ronald L. Rivest, Adi Shamir, and Leonard Adleman in 1977.

Public key systems are typically used to share secret symmetric keys between two communicating parties so that a faster private key system can be used. In private key cryptographic systems, the sender and receiver share a secret key that is used to both encrypt and decrypt secret messages sent on an insecure channel. Private key systems rely on the principle that it is computationally infeasible to decrypt the encrypted message without knowledge of the private key. Two general classifications of private key ciphers, block ciphers and stream ciphers, are discussed in the following sections.

#### 2.1.1 Private Key Block Ciphers

Private-key (also called symmetric-key) block ciphers are probably the most prominent and important elements in many cryptographic systems. Such a cipher is a function that maps n-bit plaintext blocks into n-bit ciphertext blocks. The function depends on a k-bit key that is usually chosen at random from the key space K. Each key could define a different function output for a given plaintext but this is not necessarily the case - multiple keys may give the same ciphertext result. However, to allow for unique encryption the function must be one-to-one. This means that for a specified key, only one ciphertext results from a specified plaintext [13].

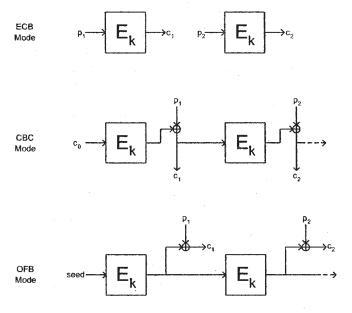

Many modes of operation can be applied to any block cipher and are illustrated in Figure 2.1. The  $\oplus$  symbol in this figure represents a bitwise exclusive OR (or XOR) operation. In Electronic Code Book (ECB) mode, the blocks are simply encrypted or decrypted one at a time with a key. If the same key is used, each time a particular plaintext is encrypted it will result in the same ciphertext. But with Cipher Block Chaining (CBC) mode this is not the case. In this mode the previous ciphertext output is XORed with the next plaintext to be encrypted before encryption takes place. The first plaintext is XORed with the ciphertext of a non-secret initialization block,  $c_0$ . In this way, multiple ciphertexts for a particular plaintext will not necessarily

Figure 2.1: Block Cipher Modes of Operation

be equivalent even if the same key is used. Another mode of operation is Output Feedback (OFB) mode in which a pseudo random sequence is produced by the block cipher algorithm. The resulting blocks generated by the algorithm are XORed with the plaintext blocks to produce the ciphertext. Given the block cipher algorithm and a non-secret initialization value or "seed" the pseudo random sequence can be reproduced. In this research only the ECB mode of operation was considered.

#### 2.1.2 Stream Ciphers

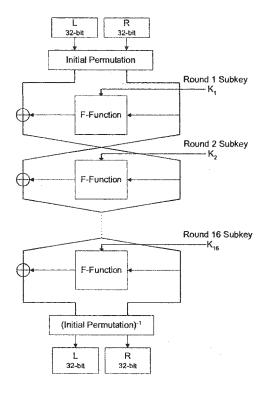

In a stream cipher a sequence of bits called the keystream is generated randomly or by some algorithm that generates bits based on an initial seed value and/or previous ciphertext values. This keystream is then combined with the plaintext bits, usually with a simple bitwise XOR operation, to produce the ciphertext as illustrated in Figure 2.2. Decryption is simply the reverse process using the same keystream bits. In general, the most complex portion of a stream cipher system is the keystream generation algorithm. Stream cipher systems are used when it is advantageous to

Figure 2.2: Stream Cipher Operation

process data on a bit-by-bit basis where, in such a situation, data would potentially have to be buffered before processing if a block cipher were used. As well, since stream ciphers operate on a bit level, error propagation is limited when compared to block ciphers.

#### 2.2 Data Encryption Standard

In the early 1970s, a banking customer asked IBM to develop a system for encrypting Automated Teller Machine (ATM) data. IBM's team (with some help from the United States National Security Agency (NSA)) developed a new encryption algorithm that was submitted to the United States National Institute of Standards and Technology (NIST). It was adopted in 1977 as a national cryptographic standard: the Data Encryption Standard [14].

DES operates on 64-bit blocks of plaintext and utilizes a 56-bit key. The key is actually supplied to the algorithm as 64-bits, but 8 of these are parity bits. The internal operation of DES is based on two general concepts: product ciphers and Feistel ciphers. In a product cipher, the overall function is composed of a number of simpler operations. Such operations could include bit transpositions, translations, arithmetic operations, modular multiplication and simple substitutions. These simple operations provide no security individually, but together they provide sufficient protection[13]. Fiestel ciphers are a special case of an iterated block cipher in which the ciphertext is calculated by repeated application of the same transformation or "round function".

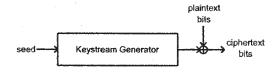

Figure 2.3 shows the overall structure of DES and, as can be seen, it is composed

Figure 2.3: DES Structure

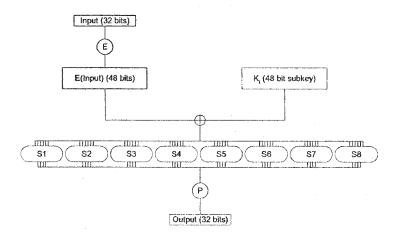

of 16 inner rounds. The input block passes through an initial permutation (IP) stage before entering the first round of the cipher and an IP<sup>-1</sup> stage after round 16. In each round, 32-bits of data enter the F-function. Figure 2.4 illustrates the internals of this function. Inside the F-function, S1-S8 are the 8 substitution mappings, called S-boxes, that map a 6-bit input into a 4-bit output. The 1st and 6th bits of the S-box input are used to select the row of the substitution table while the 2nd to 5th bits are used to select the column of the table. As an example, S-box S1 is given in Table 2.1. From this table, if the input to S1 is 101011 the S-box output would be found in row 3, column 5 which is 1001. As well, in Figure 2.4, E is a fixed

|    |    |     | ······ |    |    |    | S  | 1  |    |    |    |     |    |   |    |

|----|----|-----|--------|----|----|----|----|----|----|----|----|-----|----|---|----|

| 14 | 4  | 13  | 1      | 2  | 15 | 11 | 8  | 3  | 10 | 6  | 12 | - 5 | 9  | 0 | 7  |

| 0  | 15 | 7   | 4      | 14 | 2  | 13 | 1  | 10 | 6  | 12 | 11 | 9   | 5  | 3 | 8  |

| 4  | 1  | 14  | 8      | 13 | 6  | 2  | 11 | 15 | 12 | 9  | 7  | 3   | 10 | 5 | 0  |

| 15 | 12 | - 8 | 2      | 4  | 9  | 1  | 7  | 5  | 11 | 3  | 14 | 10  | 0  | 6 | 13 |

Table 2.1: DES S-Box S1

Figure 2.4: DES F-Function

expansion permutation that maps the 32 input bits into 48 bits and P is another permutation over the 32 output bits of the S-Boxes. Tables 2.2 and 2.3 show the outputs of these two operations where the number in a cell represents the bit of the input word that now resides at this location. The tables are read from left to right, top to bottom with the cell (0,0) representing the MSB and cell (8,6) in the E table or (8,4) in the P table representing the LSB of the output. The subkeys  $K_i$ , where

|    | E  |    |    |    |     |  |  |  |  |  |

|----|----|----|----|----|-----|--|--|--|--|--|

| 32 | 1  | 2  | 3  | 4  | 5   |  |  |  |  |  |

| 4  | 5  | 6  | 7  | 8  | . 9 |  |  |  |  |  |

| 8  | 9  | 10 | 11 | 12 | 13  |  |  |  |  |  |

| 12 | 13 | 14 | 15 | 16 | 17  |  |  |  |  |  |

| 16 | 17 | 18 | 19 | 20 | 21  |  |  |  |  |  |

| 20 | 21 | 22 | 23 | 24 | 25  |  |  |  |  |  |

| 24 | 25 | 26 | 27 | 28 | 29  |  |  |  |  |  |

| 28 | 29 | 30 | 31 | 32 | 1   |  |  |  |  |  |

Table 2.2: E Expansion

$1 \le i \le 16$ , are calculated from the original key, K, using a key scheduling algorithm as described in [14]. In the DES algorithm, decryption is accomplished by using the same algorithm with these subkeys in the reverse order.

| P  |    |    |    |  |  |  |  |

|----|----|----|----|--|--|--|--|

| 16 | 7  | 20 | 21 |  |  |  |  |

| 29 | 12 | 28 | 17 |  |  |  |  |

| 1  | 15 | 23 | 26 |  |  |  |  |

| 5  | 18 | 31 | 10 |  |  |  |  |

| 2  | 8  | 24 | 14 |  |  |  |  |

| 32 | 27 | 3  | 9  |  |  |  |  |

| 19 | 13 | 30 | 6  |  |  |  |  |

| 22 | 11 | 4  | 25 |  |  |  |  |

Table 2.3: P Permutation

#### 2.3 Advanced Encryption Standard

After a number of years of controversy and successful attempts at breaking DES [15], the United States National Institute of Standards and Technology decided to seek submissions for a new block cipher, the Advanced Encryption Standard, to replace DES. The Rijndael cipher, designed by Vincent Rijmen and Joan Daemen, was chosen as the AES algorithm on October 2, 2000 by NIST [16].

The Rijndael cipher is an iterated block cipher with a variable block length of 128, 192, or 256 bits and a variable key length of 128, 192 or 256 bits. The block and key length are independent of one another. The number of rounds of iteration depends both on the key and block lengths and can be determined from Table 2.4.

|            | Block Length |     |     |  |  |

|------------|--------------|-----|-----|--|--|

| Key Length | 128          | 192 | 256 |  |  |

| 128        | 10           | 12  | 14  |  |  |

| 192        | 12           | 12  | 14  |  |  |

| 256        | 14           | 14  | 14  |  |  |

Table 2.4: Number of Rounds in Rijndael

A typical round consists of a byte substitution, a column mixing operation, a row shifting operation and a key addition. Each of these steps performs operations on a rectangular array of bytes called the cipher STATE. Each column of the STATE is 32 bits and the number of columns depends on the block length. Initially, the STATE is formed from the input bytes by placing the bytes (from MSB to LSB) into cells  $a_{0.0}$ ,

$a_{1,0}$ ,  $a_{2,0}$ ,  $a_{3,0}$ ,  $a_{0,1}$ ,  $a_{1,1}$ , etc., where cell  $a_{i,j}$  represents the cell of *STATE* a at row i, column j. This arrangement is shown in Figure 2.5. The cipher key is also mapped

| $a_{0,0}$ | $a_{0,1}$ | $a_{0,2}$ | $a_{0,3}$ |

|-----------|-----------|-----------|-----------|

| $a_{1,0}$ | $a_{1,1}$ | $a_{1,2}$ | $a_{1,3}$ |

| $a_{2,0}$ | $a_{2,1}$ | $a_{2,2}$ | $a_{2,3}$ |

| $a_{3,0}$ | $a_{3,1}$ | $a_{3,2}$ | $a_{3,3}$ |

Figure 2.5: Example of STATE for a block size of 128 bits

onto a rectangular array of bytes in the same way. The following sections detail these cipher operations as well as how the produce the overall algorithm.

#### 2.3.1 Byte Substitution

The Rijndael byte substitution operation is a non-linear mapping that is applied to every byte of the cipher *STATE*. The substitution tables, or S-Boxes, operate on 8-bit inputs and produce 8-bit outputs. For the purposes of decryption, the inverse table is used. The S-box mappings can be found in [17].

#### 2.3.2 Row Shift

The row shift operation is a cyclical shift across each of the rows of the cipher *STATE*. The shifts for each row are determined by using Table 2.5 and are a function of the block length. For decryption, the rows are shifted by (# of columns)-(row shift from Table 2.5).

|   | Block Length | Row 0 | Row 1 | Row 2 | Row 3 |

|---|--------------|-------|-------|-------|-------|

| Γ | 128          | 0     | 1     | 2     | 3     |

|   | 192          | 0     | 1     | 2     | 3     |

| Г | 256          | 0     | 1     | 3     | 4     |

Table 2.5: Rijndael Row Shifts

#### 2.3.3 Column Mixing

The column mix operation can be pictured as a  $GF(2^8)$  multiplication of the columns of STATE with a fixed polynomial  $c(x) = 03 \cdot x^3 + 01 \cdot x^2 + 01 \cdot x + 02$ . The inverse is found by multiplying the columns of STATE with a fixed polynomial  $d(x) = 0B \cdot x^3 + 0D \cdot x^2 + 09 \cdot x + 0E$ . Further details of the mathematical principles involved in this operation can be found in the AES specification [17].

#### 2.3.4 Key Addition

At the end of each round, a round subkey is simply bit wise XORed with the STATE. The round subkey is derived from the cipher key through a key-scheduling algorithm. In total, the number of round key bits required is equal to the block length multiplied by (the number of rounds + 1). Since the key-scheduling algorithm was not implemented, it will not be discussed in this document. Further details of the key scheduling algorithm can be found in the AES specification [17].

#### 2.3.5 Rijndael Operation

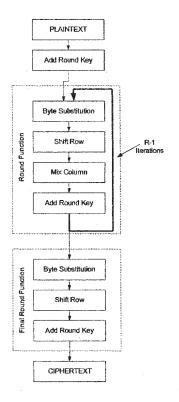

Figure 2.6 illustrates a typical Rijndael encryption cycle. As can be seen, the encryption begins with a key addition operation followed by a number of iterations of the "round function" consisting of the byte substitution, shift row, column mixing, and key addition steps described above. The final round of encryption is slightly different from the regular round in that no "mix column" operation is performed. This final round is included in the total number of rounds of iteration found in Table 2.4.

Figure 2.6: Rijndael Encryption

#### 2.4 Bluetooth Encryption Algorithm - E0

In early 1998 a number of telecommunications companies (including Ericsson, Nokia, Intel, and Toshiba) formed a special interest group to develop a low-cost, short-range wireless technology. Named "Bluetooth", this technology would allow end users to eliminate the cumbersome wires connecting their devices [18]. For example, a Bluetooth enabled cellular phone could transmit wireless information to a Bluetooth enabled headset; a printer could wirelessly send data to a personal computer. In 1999 the Bluetooth SIG announced the Bluetooth 1.0 specification and a host of Bluetooth enabled devices began to enter the marketplace.

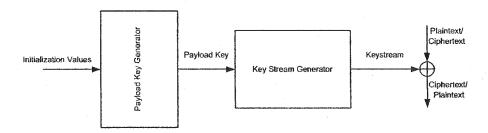

Within a Bluetooth packet the payload can be encrypted with a stream cipher called E0 that is re-synchronized for every payload [19]. A general framework for Bluetooth encryption can be seen in Figure 2.7. The E0 system handles the keystream generator initialization, keystream generation and payload encrytion/decryption. The

Figure 2.7: Bluetooth Stream Cipher

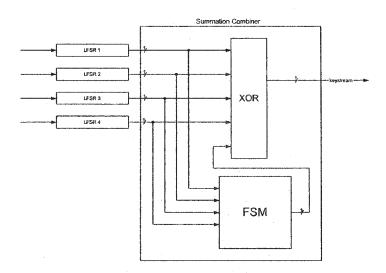

encryption key,  $K_C$  is derived from the current link key, a ciphering offset number and a random number. The payload key is then derived from this encryption key. Key management and generation were not considered in the scope of this research and further details can be found in the Bluetooth Specification [19]. The keystream generator is based on the summation generator proposed by Rueppel. In this system, four Linear Feedback Shift Register (LFSR) outputs are combined by a simple Finite State Machine (FSM) called the "summation combiner". The four LFSRs have lengths of 25, 31, 33, and 39-bits with the feedback polynomials as specified in Table 2.6. Figure 2.8 illustrates the E0 setup. As can be seen, the output of

Figure 2.8: E0

the summation combiner is the key stream sequence that is bitwise added to the plaintext/ciphertext.

| LFSR | Length | Polynomial                              |

|------|--------|-----------------------------------------|

| 1    | 25     | $t^{25} + t^{20} + t^{12} + t^8 + 1$    |

| 2    | 31     | $t^{31} + t^{24} + t^{16} + t^{12} + 1$ |

| 3    | 33     | $t^{33} + t^{28} + t^{24} + t^4 + 1$    |

| 4    | 39     | $t^{39} + t^{36} + t^{28} + t^4 + 1$    |

Table 2.6: LFSR Feedback Polynomials

#### 2.5 KASUMI

The 3rd Generation Partnership Project (3GPP) was formed in 1998 to facilitate the collaboration of a number of telecommunications standards bodies. Their mandate was to facilitate the development of a global standard for the 3rd generation mobile system based on an evolution of the current GSM networks and the radio access technologies that they support [20].

The 3GPP security architecture includes both a confidentiality algorithm, f8, and an integrity algorithm, f9, both of which are based on a block cipher called KA-SUMI [21]. The 3GPP commissioned the Security Algorithms Experts Group (SAGE) to develop a security architecture for 3G networks. SAGE based the KASUMI cipher on the MISTY algorithm that was designed by Mitsubishi Electric Corp. in 1996 [22]. (In fact, 'KASUMI' is the Japanese word for 'MISTY'.)

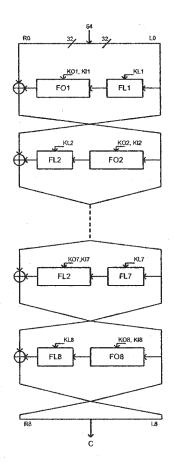

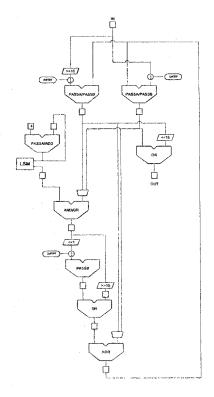

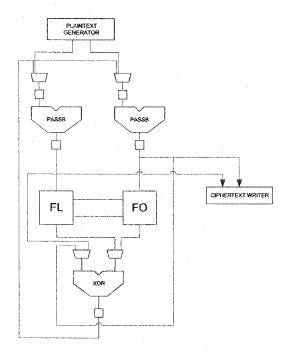

KASUMI operates on 64-bit blocks of data and utilizes a 128-bit key. Like DES, it has a Feistel structure and is composed of 8 rounds. Figure 2.9 illustrates the top level structure of the KASUMI algorithm. The round function,  $f_i$  is composed of a number of subfunctions called FL, FO, and FI that are also associated with round subkeys KL, KO, and KI respectively [23]. The following sections describe these subfunctions in more detail.

Figure 2.9: KASUMI Algorithm

#### 2.5.1 Function FL

The function FL takes 32-bits of data, I, and a 32-bit subkey KL as its inputs. Both I and KL are split into two 16-bit halves  $(R, L, KL_R, KL_L)$  and processed by the following operations where  $\land$  represents a bitwise AND operation:

$$R' = R \oplus ROL(L \wedge KL_L)$$

$$L' = L \oplus ROL(R' \wedge KL_R)$$

The ROL operation is a single bit rotation to the left. The 32-bit output of FL is the concatenation of R' and L' in the same order.

#### 2.5.2 Function FI

The function FI takes a 16-bit data value, I, and a 16-bit subkey, KI, at its input. However, unlike the functions FL and FO, the data and subkey are split unequally into a 7-bit component and a 9-bit component. In the case of I, the left portion, L, is 9-bits and the right portion, R, is 7-bits whereas for the subkey the left portion,  $KI_1$ , is 7-bits and the right,  $KI_2$ , is 9-bits.

Two substitution boxes (or S-boxes), S7 and S9, are used in this function. S7 maps a 7-bit input to a 7-bit output and S9 maps a 9-bit input to a 9-bit output. Their mappings can be found in [23]. The following series of operations define FI's output:

$$L_1=R$$

$R_1=S9[L]\oplus ZE(R)$   $L_2=R_1\oplus KI_2$   $R_2=S7[L_1]\oplus TR(R_1)\oplus KI_1$   $L_3=R_2$   $R_3=S9[L_2]\oplus ZE(R_2)$   $L_4=S7[L_3]\oplus TR[R_3]$   $R_4=R_3$  output is  $L_4|R_4$

The operation ZE(x) pads a 7-bit value to 9-bits by adding two zero bits at the most significant end. TR(x) truncates a 9-bit value to 7-bits by discarding the two most significant bits.

### 2.5.3 Function FO

The function FO takes a 32-bit data input, I, along with two 48-bit subkeys, KO and KI, as its inputs. As in FL, I is split into two 16-bit halves, R and L. The 48-bit subkeys are each split into three 16-bit subkeys where  $KO = KO_1|KO_2|KO_3$  and  $KI = KI_1|KI_2|KI_3$ .

The following operations complete the function's operation:

$$L_0=L$$

$$R_0=R$$

for  $j=1$  to 3

$$R_j=FI(L_{j-1}\oplus KO_j,KI_j)\oplus R_{j-1}$$

$$L_j=R_{j-1}$$

output  $L_3|R_3$

## 2.5.4 Key Scheduling Algorithm

The key scheduling algorithm in KASUMI, although relatively simple, was not considered for implementation in hardware. Hence, we do not describe it here and further details of this algorithm can be found in [23].

## 2.6 RC4

RC4 (which supposedly stands for Ron's Code #4) is a proprietary algorithm created by Ron Rivest of RSA Data Security Inc. It is a keystream generator for use in a stream cipher that produces an arbitrarily long pseudo random sequence using a variable length key. In 1994, an anonymous source claimed to have reverse engineered the algorithm and posted their source code on the Internet [12]. The "alleged RC4" code produces an identical keystream to that of the original, but RSA Data Security Inc. claims that their algorithm is still a secret. Despite RSA's claims, this alleged version is widely assumed to be the RC4 standard.

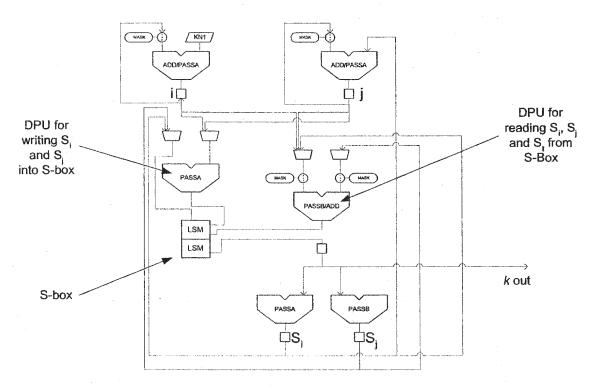

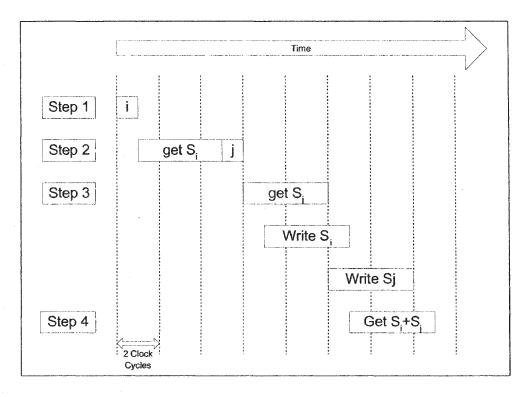

The RC4 algorithm is relatively simple. It operates as a stream cipher where its output is bitwise added to the plaintext to produce ciphertext. The algorithm performs a series of operations utilizing an 8 × 8 S-box (i.e. a table composed of 256 1-byte values) to produce a byte of output. The following pseudocode sequence

describes the operation to produce one byte of output:

$$i = (i+1) \mod 256$$

$j = (j+S_i) \mod 256$

swap  $S_i$  and  $S_j$

$t = (S_i + S_j) \mod 256$

$k = S_t$  where  $k$  is the 8-bit output

where  $S_i$  represents the *i*th byte of the 256 byte S-Box. The S-box is initialized by first filling all entries linearly so that  $S_0 = 0, \ldots, S_{255} = 255$ . With K representing the key array the following operations are performed to complete the initialization:

for

$$(i=0$$

to 255)

$$j=(j+S_i+K_{i \bmod 255}) \bmod 255$$

swap  $S_i$  and  $S_j$

Although the original RC4 description dealt with 8-bit words and  $8 \times 8$  (256 in-put/output) S-boxes, the algorithm can be easily extended to an n-bit form. For example, a 16-bit RC4 version would have a  $16 \times 16$  S-box and 16-bit outputs. Since the core of the algorithm is not affected by the size of n, a larger value of n should yield a faster implementation. However, the keystream outputs for different values of n will not be equivalent [12].

## Chapter 3

# Cryptographic Algorithm Implementation

Traditionally, communication system developers have had three standard implementation options available: ASICs, software running on a general purpose microprocessor, and FPGAs. One of the most common choices is to use a semi-custom or full-custom ASIC. Both of these devices use one of a variety of process technologies, such as CMOS and Gallium Arsenide, to produce analog or digital circuits on chip. Semi-custom ASICs utilize pre-developed blocks that implement complex functions along with custom developed circuits to achieve their final purpose. On the other hand, full-custom ASICs are designed without using any precompiled blocks and can be optimized in terms of both area and performance [24]. Because ASICs are designed to perform a specific set of computations, they can execute them extremely quickly and efficiently. However, after fabrication the circuit cannot be altered. Hence, they must be redesigned and remanufactured if any part of the algorithm is modified or if any part of the circuit is modified. The development cost for an ASIC is typically very high. Therefore, ASICs are only suitable in a high production volume application where high speed is required [8].

The second option is to use a general-purpose microprocessor and implement the algorithm in software. Microprocessors execute a set of instructions to implement an algorithm and by changing these instructions the implementation/algorithm can

be altered without changing the associated hardware. However, with this added flexibility comes an overall lower level of performance and power efficiency when compared to an ASIC implementation. Secondly, since the set of available instructions is fixed when the microprocessor is fabricated, any other operations to be performed must be built from these instructions. This will result in a higher execution overhead for some operations when compared to a direct implementation.

The final option when implementing an algorithm is to use a reconfigurable device such as a FPGA. FPGAs consist of arrays of Configurable Logic Blocks (CLBs) that implement the functions of logical gates. The logical functions performed by the CLBs as well as the interconnections between them can be altered by sending signals to the chip. The FPGAs and their CLBs can be reprogrammed repeatedly and long after fabrication [25]. FPGAs now contain millions of gates per chip and can be used to implement very complex computations on a single device. Dehon in [26] showed that reconfigurable technologies had a raw computational density that was an order of magnitude higher than programmable (microprocessor) technologies when performing the same operations from cycle to cycle. Since configurations are written in a Hardware Design Language (HDL) and then mapped to the FPGA, no manufacturing is required and the development cost is much lower than that of an ASIC. However, FPGAs cannot achieve the computational speed or efficiency of an ASIC implementation and FPGA devices cost more to produce than ASICs in high volume applications.

Recent developments in the area of System On Chip (SoC) devices have given system designers much greater flexibility to implement ASICs. The development of soft instruction processors is one such advancement. Soft instruction processors allow the designer to quickly modify a pre-packaged processor core's instruction architecture. This core, when included in an ASIC design, can speed up development time and reduce costs dramatically [27].

Recently, the advent of reconfigurable processors has added yet another option to designers. Such processors incorporate the advantages of microprocessor and FPGA technologies and have shown significant performance increases in the areas of image processing, compression, computational chemistry [25], object tracking, fuzzy controllers [28], music [29] and cryptography. The following sections outline some recent developments in the areas of reconfigurable computing and its applications in the field of cryptography.

## 3.1 Reconfigurable Processor Architectures

An FPGA can act as a stand alone device in a system just as in ASIC implementations. However, devices that couple a general-purpose microprocessor with a reconfigurable logic device have started to emerge in the marketplace. These devices have the key feature of being able to perform computations in hardware to increase performance, while retaining much of the flexibility of a software solution. More importantly it is possible, in some cases, for the configuration to change at run time.

Wittig in [30] describes three general classes of reconfigurable systems:

- 1. FPGA loosely coupled to a fixed host computer

- 2. FPGA loosely coupled to a fixed, integrated CPU

- 3. FPGA closely coupled to a fixed, integrated CPU

While any reconfigurable system will fall under one of these categories, it is sometimes difficult to differentiate between classes 1 and 2. Instead, a classification system based on both the coupling level and type of interaction between the general-purpose processor and reconfigurable logic can be used as outlined below [31].

#### **Stand Alone Processor**

In this case, the FPGA acts as a stand-alone processor as described in the previous section. Any communication between the FPGA and the CPU must be done through an I/O interface. Since I/O communication is relatively slow, it is only useful when communication between FPGA and CPU is infrequent.

#### Attached Processor

When the FPGA acts as an additional processor in a multi-processor system it is classified as an "attached processor". Typically, in this sort of system, the FPGA communicates with the other processors over a common bus. Hence, this form of system is more closely coupled than the stand-alone case since bus transactions are usually much more efficient than I/O operations.

#### Coprocessor

In some systems, the FPGA may aid the CPU with certain computations and is acting as a coprocessor. Depending on the system, the FPGA can do these computations in parallel with the CPU and this can dramatically improve system performance. As well, in most cases these coprocessors have direct access to the CPU's main memory, further improving system performance.

#### Reconfigurable Functional Unit

As the level of integration for ASICs has increased the idea of placing both the CPU and the reconfigurable logic, or Reconfigurable Functional Unit (RFU), on the same chip has become a reality. In this arrangement, the RFU can be directly added to the processors execution pipeline in parallel with the existing CPU units. This allows new instructions to be created dynamically in the RFU that can be added to the

already existing instruction set. As the amount of logic that can be integrated with the CPU increases, reconfigurable system performance will improve substantially.

It is possible to obtain significant speedups over software implementations by using reconfigurable hardware. However, this is only true when the communication overhead for implementing an algorithm in hardware is small compared to the amount of computation done in the reconfigurable hardware. Wittig in [30] quantified this with the following equations:

$$T_H + T_{OV} < T_S$$

$$\frac{T_H}{T_S} + \frac{T_{OV}}{T_S} < 1$$

where

$T_{OV} = time \ to \ comum municate \ data \ and \ control \ overhead$

$T_H = time to execute function in hardware$

$T_S = time to execute function in software$

This equation is only applicable when it is feasible to implement an algorithm in hardware (i.e., the overall execution time is smaller in hardware than in software). In the fractional form of the above equation, the quantity  $\frac{T_H}{T_S}$  represents the actual hardware computational speedup and the fraction  $\frac{T_{OV}}{T_S}$  represents the granularity of the application implemented in hardware. Hence, an implementation with a small  $\frac{T_{OV}}{T_S}$  ratio indicates that it has a larger grain size since less communication occurred between CPU and reconfigurable hardware. Systems with a small  $\frac{T_{OV}}{T_S}$  ratio need a smaller hardware speedup to have the same overall speedup as systems with a larger  $\frac{T_{OV}}{T_S}$  ratio. Therefore, the communications overhead plays a vital role in high performance applications utilizing reconfigurable devices.

Until relatively recently, the available ASIC manufacturing processes did not support a level of integration necessary for the development of complex RFU systems. However, reconfigurable systems that closely couple a microprocessor with a relatively large reconfigurable core have begun to emerge in the market. Before considering the

implementation of algorithms on one such architecture, it is important to understand some of the architectural features that are common to all reconfigurable microprocessors. The addition of closely coupled reconfigurable logic not only adds new design issues but also complicates decisions that can be made quite easily in a software or ASIC and stand-alone FPGA implementations. The following sections detail some of the architectural options available when developing a system containing such a coupled reconfigurable device.

## 3.1.1 Microprocessor Architecture

There are a number of general requirements for any fixed CPU that is attached to reconfigurable logic, the most basic being speed and interfacing flexibility. The processor must be fast at executing instructions from its own instruction set as well as providing support for the instructions custom built in reconfigurable logic [32]. In particular, the CPU to reconfigurable logic interface must not be slower than the computational delay of the instructions implemented in reconfigurable hardware (i.e. a high  $\frac{T_{OV}}{T_S}$  ratio). Jeschke in [33] has found that the achievable speedup from a reconfigurable system can be severely limited by the CPU-logic interface and suggests that the current state of the art microprocessor should be used in a design. In most cases, a fast Reduced Instruction Set Computer (RISC) CPU is coupled with reconfigurable logic since the RISC CPU's limited instruction set allows designers to implement complex functions in reconfigurable logic on a per application basis.

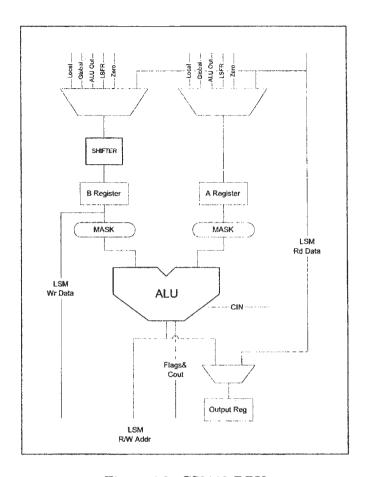

## 3.1.2 Logic Block Granularity

Reconfigurable hardware is typically based on a set of computation structures that are repeated to form an array. These structures, commonly called logic blocks or cells, vary in complexity from a very small and simple block that can calculate a function of only two inputs, to a structure that is essentially a 32-bit Arithmetic Logic

Unit (ALU). Some of these blocks are configurable themselves in that the performed operation is chosen from a configuration set. Other blocks perform fixed operations and their configurability lies in their interconnection. The size and complexity of the basic computing block is referred to as the block's granularity [34].

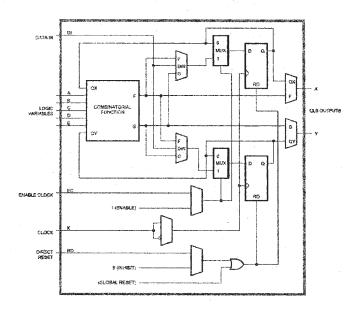

Figure 3.1 [35] shows an example of a fine grained logic block that is found in the Xilinx 3000 series of FPGAs [35]. This type of logic block is useful for fine-

Figure 3.1: Xilinx XC3000 Series Configurable Logic Block

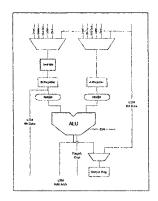

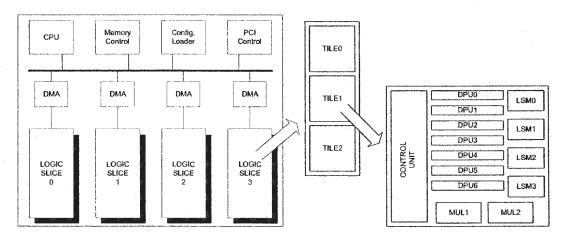

grained bit-level manipulation of data. These kinds of operations are frequently found in encryption and image processing applications. Also, because these cells are fine grained, computation structures of arbitrary bit widths can be created. Figure 3.2 shows an example of a very coarse grained reconfigurable architecture, the Chameleon CS2112 that is discussed further in Chapter 4. The Chameleon CS2112 is not just a coarse grained solution. It is also termed a "heterogeneous" architecture since there are not only data path units, but also multipliers, control logic and data memory residing in the reconfigurable portion of the chip. A "nonheterogeneous" architecture, on the other hand, would be composed of totally identical reconfigurable logic cells. Typically, very coarse grained architectures are intended for the implementation of

Figure 3.2: CS2112 Example

word-width data path circuits and will perform word sized computations much more quickly than a set of smaller CLBs connected to perform the same function. However, they are inefficient at performing operations on bit level data when compared to fine grained architectures.

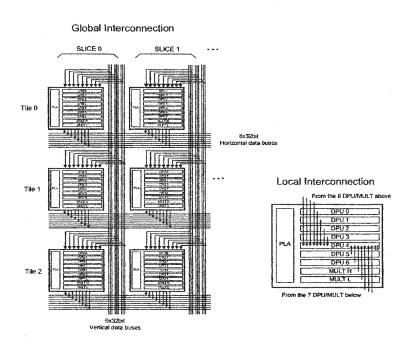

#### 3.1.3 Data Interconnection

Another important component of a reconfigurable architecture are the routing structures used within the reconfigurable portion of the design. One group has argued that the interconnect should constitute a much higher proportion of the area in order to allow for successful routing under high logic utilization conditions [36]. However, routing resources occupy a much larger part of the area of an IC than the logic resources. As a result, the most area efficient designs will be those that optimize their use of routing resources rather than the logic resources.

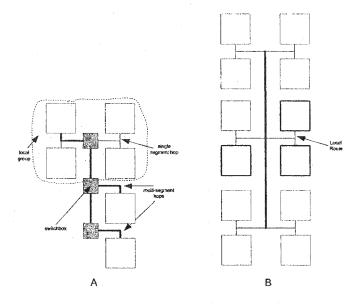

The two primary routing structures used in reconfigurable designs to provide both local and global routing resources are illustrated in Figure 3.3. The first is segmented routing in which short wires accommodate local communications traffic. These short segments can be connected together using switchboxes to emulate longer wires. The second form of routing is hierarchical routing. In this case, routing within a group of logic blocks is at the local level and at the boundaries of these groups longer wires

Figure 3.3: Segmented (A) and Hierarchial Routing (B) Examples

are used to connect the groups together. Provided a good mapping has been made in hardware, the most common communication should be local in a hierarchical scheme. Both of the above schemes are referred to as "island-style" routing architectures. A few alternatives use a one-dimensional routing scheme. One example is a bus-based scheme in which only vertical or horizontal busses connect the configurable elements.

In other systems multiple FPGAs are linked to form a reconfigurable device. These require not only an efficient internal routing scheme, but also an efficient external interconnection architecture. These systems are typically used when an algorithm is too large to fit on a single reconfigurable device.

## 3.1.4 Reconfiguration Models

Traditional FPGA structures have been single-context, allowing only one full-chip configuration to be loaded at a time. However, the designers using reconfigurable systems have found this style of configuration to be too limiting and/or slow to efficiently implement run-time reconfiguration. A number of methods that have been

developed to limit the overhead of changing configurations at run-time are discussed below.

In a single context device, configurations are loaded using a serial stream of configuration information. Because only sequential access is supported, any change to a configuration on this type of device requires a complete reprogramming of the entire chip. This type of access does simplify the reconfiguration hardware but it does create a high reconfiguration overhead when only a small part of the configuration needs to be updated. In order to implement run-time reconfiguration using a single context device the configurations must be grouped into contexts, and each full context swapped into and out of the device as needed. Since swapping the contexts involves reconfiguring the entire device, great care must be taken in designing the configurations [37].

A multi-context device includes multiple memory bits for each programming bit location. These memory bits can be thought of as multiple planes of configuration information. One plane of configuration information can be active at a given moment, but the device can quickly switch between different planes of pre-programmed configurations. This system does allow for the loading of a configuration in the background while the active plane is running. In this case, the grouping of configurations into contexts is less critical because of both the background loading capability and the ability to switch contexts rapidly. However, it is still important to ensure that the configurations used in close proximity in time are loaded into the multi-context device at the same time [26].

In some cases, configurations do not occupy the all of the reconfigurable resources, or only a part of an active configuration requires modification. In these cases partial reconfiguration would be useful. In such reconfigurable devices, the underlying programming layer operates like a RAM device where addresses are used to specify the target location of configuration data. In some cases, the unchanged portion

of the device can remain active while the new data is being loaded, further hiding configuration latency. A further modification of the above strategy is for the partial reconfiguration to occur in stages [38]. This type of reconfigurable hardware is called pipeline reconfigurable or a stripped device. This type of structure also allows for the overlap of configuration and execution time as one pipeline stage is configured while the others are executing.

While multi-context and partially reconfigurable devices reduce the time required to switch configurations, the fact remains that reconfiguration will occur during program execution. A number of different tactics for reducing configuration overhead have been developed. First, the loading of configurations can be timed such that the configuration overlaps as much as possible with the execution of instructions by the host processor. Second, compression techniques can be introduced to decrease the amount of configuration data that must be transferred to the system. Third, the number of reconfigurations can be reduced through hardware optimizations that keep configurations that will be reused from being unnecessarily replaced by incoming configurations. Fourth, the actual process of transferring the data from the host processor to the reconfigurable hardware can be modified to include a configuration cache, which would provide a faster reconfiguration [39]. Finally, Sakr in [37] proposed employing the use of optical channels to allow fast parallel loading of the reconfiguration control word as well as the migration of the configuration cache off-chip.

## 3.1.5 Programming Models

Significant gains in performance can be gained through using reconfigurable hardware. However, application programmers will tend to ignore this potential unless they are able to easily incorporate its use into their systems. This requires a software design environment that aids in the creation of configurations for the reconfigurable hardware. This can range from a set of libraries to assist in the manual creation of circuits to a complectly automated circuit design system. While the manual creation of circuits requires a great deal of background knowledge of the system being used, it allows for the creation of designs that are usually more efficient than automatic compilation systems. However, automatic compilation systems provide a simple means for creating an application and, as such, make the use of reconfigurable hardware more accessible.

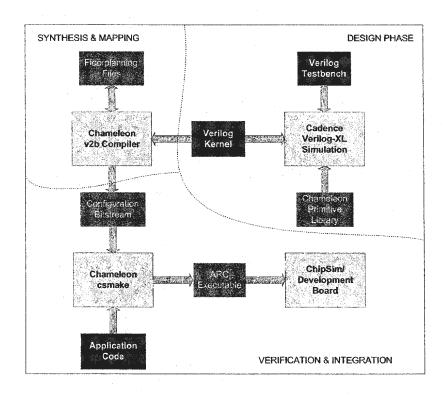

Another complication in the development of an application for a reconfigurable system is that the program must first be partitioned into sections to be executed on the reconfigurable hardware and in software by the microprocessor. Wittig in [8] described a software environment that any "user-friendly" reconfigurable system should include. This tool would automatically provide the user with the most efficient system configuration; the user would only have to program the system in a high level language. Figure 3.4 illustrates the operation of this system. In the first stage, the

Figure 3.4: Ideal Software Development Environment for Coupled Reconfigurable Devices

preprocessor is used to identify sections of code that are candidates for execution in hardware. Essentially, the preprocessor attempts to perform the hardware/software partitioning. It should be noted that the preprocessor does not necessarily produce an optimal set of hardware functions. Next, the hardware is synthesized and mapped to the reconfigurable logic and the software is compiled. These hardware and software images are then given to the operating system (OS). In this scheme, the OS is responsible for deciding what portions of the software code are to be executed in hardware and schedules operations so as to give the best overall performance. Hence, using this type of software environment, users could run their standard high level language applications on a reconfigurable system just like on a standard, fixed microprocessor, while benefitting from an optimal use of the reconfigurable hardware resources [8].

Existing reconfigurable system software environments do not typically provide the level of automation described above. In systems where the function identification and extraction process is automated, the user is still usually required to select the most desired candidates from a complete list of synthesized functions. In the majority of commercially available systems, the user is required to complete the entire processes of selecting candidate functions, writing the configurations and, in some cases, mapping them to reconfigurable hardware.

# 3.2 Reconfigurable Computing and Cryptographic Hardware

As stated before, the explosive growth in the Internet and mobile communication has led to increased research and development in the area of cryptography. This research can be categorized into three broad areas based on cryptographic capabilities. In the most specific category are the designs which implement only a single algorithm. Typically, such implementations are developed on either ASICs, FPGAs or in software

and are used to evaluate and optimize the performance of a particular algorithm in the chosen medium. At the next level of capability is the cryptographic accelerator. These hardware devices implement multiple cryptographic algorithms and also accelerate processing at the communications protocol level. Finally, in the most general category, are the hardware devices which aim to accelerate cryptographic primitives but not specific algorithms.

When a new cryptographic algorithm is developed and during its useful lifetime, it is scrutinized not only from a security perspective but also from an implementation point of view. The algorithm may be mapped to software, hardware or both, depending on its target application. For example, DES was designed as a general cryptographic standard and, as such, numerous hardware and software implementations have been developed since its release in 1977. Although developed for hardware implementation, DES has been successfully implemented in software with speeds of greater than 500 Kbps [40][41][42]. However, a much larger effort has been devoted to developing high speed hardware implementations of DES. Wilcox et al. in [43] describe an ASIC design that can achieve up to 10 Gbps throughput. As well, Leitold in [44] describes a single chip Triple-DES - a form of the algorithm in which data is encrypted three times - solution that can operate at speeds of up to 155 Mbps. Also, a number of reconfigurable system implementations have been developed over the last 26 years. Trimberger in [45] details the development of a DES FPGA core which has a throughput of up to 12 Gbps. Table 3.1 summarizes some of the results obtained with the other ciphers discussed in Chapter 2.

The most recent development in the communications security marketplace has been the development of devices that accelerate a number of algorithms on a single chip. These devices are usually found in systems as an encryption coprocessor which is handed data to be encrypted/decrypted, an inline processor which views all packets and performs security duties when necessary, or as a portion of the network system

| Cipher                  | Implementation                   | Throughput       |

|-------------------------|----------------------------------|------------------|

| AES with 128-bit blocks | Xilinx Virtex-E FPGA [46]        | 7000 Mbps        |

|                         | Xilinx Virtex FPGA [47]          | 353 Mbps         |

|                         | ASIC [48]                        | 1820 Mbps        |

|                         | Altera FPD [49]                  | 900 Mbps         |

|                         | APEX FPD [49]                    | 570 Mbps         |

|                         | ASIC [50]                        | 2360 Mbps        |

|                         | Software (Pentium IV 2 GHz) [51] | approx. 700 Mbps |

| KASUMI                  | ASIC [52]                        | 1100 Mbps        |

| E0                      | ASIC [53]                        | 320 Mbps         |

|                         | Software [53]                    | 33 Mbps          |

| RC4                     | Software (DEC 3000/400) [54]     | 15.4 Mbps        |

Table 3.1: Cipher Performance Figures

processor itself [55]. Companies such as Broadcom [56], Cavium Networks [57] and Corrent [58] all produce boards aimed at accelerating IPsec and SSL/TLS protocol transactions. These protocols, which are widely used in packet data communications, contain a variety of public and private key algorithms, such as DES and AES, that are used to provide authentication, authenticity and privacy. Although these devices are typically implemented as ASICs, Andoni in [59] presents an FPGA based IPsec accelerator with impressive throughput capability.

Since many of the primitive operations, such as bit permutations, XORs and table lookups, are repeatedly used in most private key cryptographic algorithms, it is very appealing to try to develop an architecture that is optimized for this subset of operations. As well, such architectures usually couple a microprocessor with a reconfigurable core to allow splitting the algorithm across hardware and software in an optimum manner. Since some operations can be more efficiently implemented in software and vice versa this is an important attribute. Also, these architectures allow the developer to add new algorithms as specifications change and give the designer much more flexibility than an ASIC solution. One such example is the CryptoBooster coprocessor developed by Mosanya et al. in [60]. It is a modular architecture that

allows a user to load in various cryptographic modules needed to accelerate their application. Another example is the PipeRench architecture developed by Taylor [61]. This architecture is a pipelined reconfigurable fabric that is optimized for many of the operations commonly used in private key cryptography. PipeRench also utilizes a virtual hardware scheme so that large hardware configurations can be supported on limited physical hardware. A third example is CYPRIS, a reconfigurable microprocessor developed by Lockheed Martin Corp [62]. The CYPRIS architecture contains a high speed RISC processor and a reconfigurable logic block on the same die. Its primary goal was to provide security in hand held radio and other radio communication devices. In all cases, a number of ciphers were implemented and significant performance gains were achieved over purely software implementations. However, the algorithms from Chapter 2 were not discussed so performance comparisons could not be made.

# Chapter 4

# The Chameleon CS2112 Reconfigurable Communications Processor