# Power Analysis of Stream Ciphers Based on Feedback Shift Registers

by

© Abdulah A. Zadeh, M.Sc., B.Eng.

A thesis submitted to the School of Graduate Studies in partial fulfilment of the requirements for the degree of Doctor of Philosophy

Faculty of Engineering and Applied Science Memorial University of Newfoundland May 2014

## Acknowledgements

I would like to sincerely thank my supervisor Dr. Howard M. Heys.

Also, I should thank my friends and other professors: Cheng Wang, for many good times we had in lab and working towards our PhD degrees, Dennis Peters, Cheng Li, Lihong Zhang, Paul Gillard, Theodore Norvell, Amr Youssef, Gabriel Lau, and Nolan White.

#### **Abstract**

In recent days, many cryptographic devices, such as smart-cards and cell phones, are widely accessible to many people. However, wide access to cryptographic devices makes them vulnerable to side channel analysis (SCA) attack. As such, there is a high demand for research in the field of side channel analysis. Although SCA attacks have been extensively applied to block ciphers, only a limited amount of research is available on the effectiveness of side channel analysis on stream ciphers. In this dissertation, we study SCA attacks on stream ciphers and develop some cryptanalysis methods for applying the attacks effectively on practical realization of stream ciphers.

The proposed power analysis attacks were first theoretically applied to stream ciphers with a linear feedback shift register (LFSR) and nonlinear filtering function, a structure referred to as a filter generator. Since typical stream ciphers include multiple LFSRs and/or nonlinear feedback shift registers (NLFSRs), we first consider the extension of the typical power analysis attack to stream ciphers with multiple LFSRs and a nonlinear combining function, known as a combination generator. Then, the attack is extended to stream ciphers based on nonlinear feedback shift registers (NLFSRs) and stream ciphers with multiple NLFSRs and LFSRs.

In most papers related to applying side channel analysis attacks to stream ciphers, the authors ignore the effect of noise and inaccurate measurements. This limits the applicability of their methods for real applications. This dissertation has developed side channel analysis attacks on feedback shift register (FSR) based stream

ciphers with consideration of inaccurate measurement effects. At first, we have developed the attack for stream ciphers based on an individual LFSR and/or NLFSR, while the power measurements are inaccurate and they do not exactly match the theoretical values. Later, considering inaccurate measurements, we have developed power analysis of stream ciphers with multiple LFSRs and NLFSRs.

Finally, we consider combining SCA with some classical attacks on stream ciphers based on mathematical and statistical approaches to recover key or state bits of the stream ciphers. Hence, we have extended the correlation attack, fast correlation attack and algebraic attack, which are mathematical (or classical) attacks, such that they are applicable with side channel analysis. The proposed methods are validated through implementation on a practical cryptographic algorithm, the Grain stream cipher.

The practical investigations in this dissertation are done using simulated ASIC circuits. To simulate the behavior of ASIC circuits, we have implemented them using Cadence Virtuoso Spectre Circuit Simulator version 5.10.41. All the circuits including LFSR, NLFSR and Grain, are prototyped in TSMC 180 nm standard cell CMOS technology. The simulated power consumptions are used to investigate the practical application of the proposed attacks.

This dissertation shows power analysis is a powerful technique to attack stream ciphers and recover state bits and/or the key of the stream ciphers. Furthermore, combining classical methods and measured power data can significantly reduce the complexity of an attack of a stream cipher and countermeasure methods should be considered in hardware implementation of stream ciphers, to make them resistant to side channel analysis.

# Contents

| A | Acknowledgements |                         |                |            |  |   | iii  |

|---|------------------|-------------------------|----------------|------------|--|---|------|

| A | Abstract         |                         |                |            |  |   | iv   |

| 1 | Introduction     |                         |                |            |  | 5 |      |

| 2 | Bac              | Background              |                |            |  |   | 10   |

|   | 2.1              | Linear and Nonlinear    | Feedback Shift | Registers  |  |   | . 10 |

|   | 2.2              | Grain                   |                |            |  |   | . 12 |

|   | 2.3              | Е0                      |                |            |  |   | . 17 |

|   | 2.4              | LILI-128                |                |            |  |   | . 18 |

|   | 2.5              | 5 Side Channel Analysis |                |            |  |   | . 19 |

|   |                  | 2.5.1 Timing Attack     |                |            |  |   | . 20 |

|   |                  | 2.5.2 Template Atta     | ck             |            |  |   | . 20 |

|   |                  | 2.5.3 Power Analysis    | s Attack       |            |  |   | . 21 |

|   |                  | 2.5.3.1 Simpl           | le Power Analy | rsis       |  |   | . 22 |

|   |                  | 2.5.3.2 Differ          | ential Power A | analysis . |  |   | . 26 |

|   | 2.6              | Classical Attack of Sti | ream Ciphers   |            |  |   | . 27 |

|   |                                                     | 2.6.1                                                              | Time-Memory Trade off Attack                                 | 27 |  |  |

|---|-----------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------|----|--|--|

|   |                                                     | 2.6.2                                                              | Algebraic Attack                                             | 28 |  |  |

|   |                                                     | 2.6.3                                                              | Correlation and Fast Correlation Attack                      | 29 |  |  |

|   | 2.7                                                 | Summ                                                               | ary                                                          | 30 |  |  |

| 3 | Арр                                                 | olicabil                                                           | ity of Simple Power Analysis to Stream Ciphers Con-          |    |  |  |

|   | structed Using Multiple LFSRs                       |                                                                    |                                                              | 31 |  |  |

|   | 3.1                                                 | Extens                                                             | sion of Simple Power Analysis to Ciphers with Multiple LFSRs | 32 |  |  |

|   | 3.2                                                 | Application of the Attack to the E0 Stream Cipher                  |                                                              |    |  |  |

|   | 3.3                                                 | eation of the Attack to Irregular Clocking Stream Cipher, LILI-128 | 39                                                           |    |  |  |

|   | 3.4                                                 | Summ                                                               | ary                                                          | 41 |  |  |

| 4 | Side Channel Analysis of NLFSR Based Stream Ciphers |                                                                    |                                                              |    |  |  |

|   | 4.1                                                 | Idealiz                                                            | zed SPA Applied to NLFSRs                                    | 43 |  |  |

|   | 4.2                                                 | Complexity vs Available Power Samples                              |                                                              |    |  |  |

|   | 4.3                                                 | Applying SPA to Grain                                              |                                                              |    |  |  |

|   | 4.4                                                 | Summ                                                               | ary                                                          | 49 |  |  |

| 5 | Pra                                                 | ctical A                                                           | Application of SPA                                           | 51 |  |  |

|   | 5.1                                                 | Power                                                              | Consumption of a Single D Flip-Flop                          | 51 |  |  |

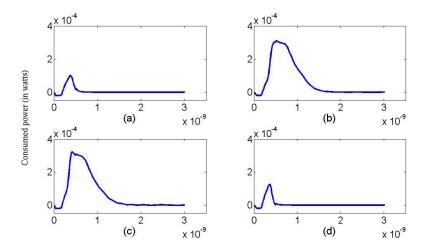

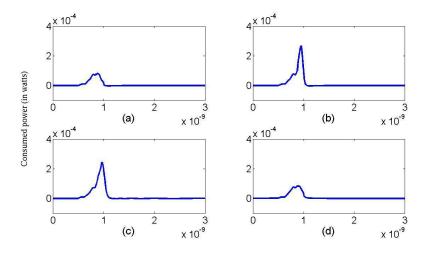

|   |                                                     | 5.1.1                                                              | Power Consumption of the D Flip-flop at the Rising Edge of   |    |  |  |

|   |                                                     |                                                                    | the Clock                                                    | 52 |  |  |

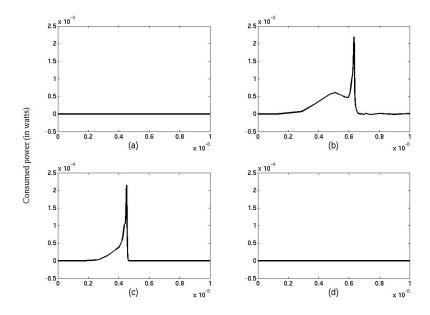

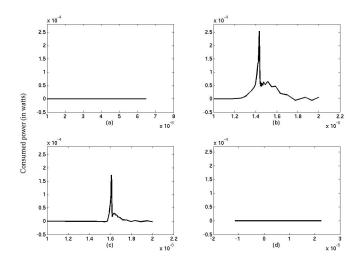

|   |                                                     | 5.1.2                                                              | Power Consumption of the D Flip-flop at the Falling Edge of  |    |  |  |

|   |                                                     |                                                                    | the Clock                                                    | 56 |  |  |

|   | 5.2                                                 | Develo                                                             | oping Falling Edge SPA of LFSR/NLFSR                         | 60 |  |  |

|   | 5.3  | Categorization of Power Measurements                                           |                                      |     |  |

|---|------|--------------------------------------------------------------------------------|--------------------------------------|-----|--|

|   |      | 5.3.1                                                                          | Categorizing $MPD$                   | 64  |  |

|   | 5.4  | Basic Methods to Determine Correctly Categorized $PD$                          |                                      |     |  |

|   |      | 5.4.1                                                                          | Rising Edge/Falling Edge Equivalence | 67  |  |

|   |      | 5.4.2                                                                          | Robust Threshold                     | 68  |  |

|   |      | 5.4.3                                                                          | Sequence Consistency                 | 68  |  |

|   | 5.5  | Advanced Categorization Methods                                                |                                      |     |  |

|   | 5.6  | Analyzing an NLFSR                                                             |                                      |     |  |

|   | 5.7  | An Improved Approach to SPA of LFSR Based Stream Ciphers                       |                                      |     |  |

|   | 5.8  | Analy                                                                          | zing an LFSR                         | 85  |  |

|   | 5.9  | Summary                                                                        |                                      |     |  |

| 6 | Usiı | ing Simple Power Analysis for Correlation Attack                               |                                      |     |  |

|   | 6.1  | Preliminaries: Correlation Attack                                              |                                      |     |  |

|   | 6.2  | Categorization of Measured Power Difference Values                             |                                      |     |  |

|   | 6.3  | Practical Categorization for Grain                                             |                                      |     |  |

|   | 6.4  | Divide-and-Conquer Method                                                      |                                      |     |  |

|   |      | 6.4.1 Using Power Measurements in a Brute Force Attack                         |                                      | 98  |  |

|   |      | 6.4.2 SPA Attack Using Divide-and-Conquer on Stream Ciphers w<br>Multiple FSRs |                                      |     |  |

|   |      |                                                                                |                                      | 101 |  |

|   |      |                                                                                | 6.4.2.1 General Attack               | 101 |  |

|   |      |                                                                                | 6.4.2.2 Applying the Attack to Grain | 104 |  |

|   |      |                                                                                | 6.4.2.3 Analysis of Attack on Grain  | 107 |  |

|   |      | 6.4.3 General Applicability of the Attack to Multiple FSR Ciphers              |                                      |     |  |

|                                       | 6.5                                                     | Summ                                   | ary                      |                                           | 112 |

|---------------------------------------|---------------------------------------------------------|----------------------------------------|--------------------------|-------------------------------------------|-----|

| 7                                     | Using Fast Correlation Attack for Simple Power Analysis |                                        |                          |                                           | 113 |

|                                       | 7.1                                                     | Preliminaries: Fast Correlation Attack |                          |                                           | 114 |

|                                       | 7.2                                                     | Using                                  | Fast Corn                | relation Attack in Simple Power Analysis  | 119 |

|                                       | 7.3                                                     | Applic                                 | cation of l              | Fast Correlation Attack to Grain          | 123 |

| 7.3.1 Categorizing the $MPD$ of Grain |                                                         |                                        | izing the $MPD$ of Grain | 124                                       |     |

|                                       |                                                         | 7.3.2                                  | Deriving                 | g the LFSR State Bits of Grain            | 128 |

|                                       |                                                         | 7.3.3                                  | Deriving                 | g the NLFSR State Bits of Grain           | 129 |

|                                       |                                                         |                                        | 7.3.3.1                  | Deriving the NLFSR State Bits of Grain-v0 | 129 |

|                                       |                                                         |                                        | 7.3.3.2                  | Deriving the NLFSR State Bits of Grain-v1 | 131 |

|                                       | 7.4                                                     | Summ                                   | ary                      |                                           | 135 |

| 8 Conclusion                          |                                                         |                                        |                          |                                           | 137 |

| 8.1 Summary of Research               |                                                         |                                        | search                   | 137                                       |     |

|                                       | 8.2                                                     | Future                                 | e Work .                 |                                           | 139 |

| Bi                                    | bliog                                                   | graphy                                 |                          |                                           | 141 |

| $\mathbf{A}$                          |                                                         |                                        |                          |                                           | 157 |

| В                                     |                                                         |                                        |                          |                                           | 160 |

|                                       | B.1                                                     | Linear                                 | rization                 |                                           | 160 |

|                                       | B.2                                                     | XL .                                   |                          |                                           | 161 |

# Chapter 1

## Introduction

Increasing the application of complex systems increases the necessity of security and data obscurity. Many companies require their information and data to be housed securely and transmitted privately on the Internet. *Cryptology* is the science of hiding data [1]. Hence, many new ranges of application in cryptology have been opened in recent years. The demands of transferring these data over different networks such as Internet, mobile systems and wireless networks underscores the necessity of studying modern cryptology.

Nowadays, cryptology's objective is not summarized merely in confidentiality or encryption or hiding data from unauthorized persons. It also includes authenticity (incoming data originating from authorized source), data integrity (data is not changed or maliciously modified before it is received) and digital signature (verification of the authenticity of the message) [2].

Cryptology is divided into two dependent fields, *cryptography* and *cryptanalysis* [2, 3]. The aim of cryptography is to design secure systems and/or protocols of

transferring data. It includes offering algorithms and methods of obscuring data called cryptographic algorithms or ciphers. However, cryptanalysis is the study of methods for obtaining the meaning of encrypted information without access to the secret information. Typically, in cryptanalysis, scientists try to find the key. Applying a cryptanalysis method is called an *attack*.

Cryptographic algorithms are divided into two classes, public key and private key. In private key (also known as symmetric key), both parties involved share the same key. This key is kept secret. Anybody who obtains it, can decrypt the ciphertext and recover the original data (plaintext). Thus, a secure channel should be established to transfer the private key to the other party. In public key cryptography, each party has its own unique key and access to a shared public key. Since, each party uses its own key to encrypt or decrypt, a secure channel is not necessary [4].

In comparison public key cryptography requires more computations. Hence, the main application of public key cryptography is key exchanging. In order to avoid high computational process of public key cryptography, applications usually also make use of private key cryptography. Public key cryptography are used to generate a shared key for both parties of the communications. Then, private key cryptography, with lower computational process is used to encrypt and decrypt the data.

Private key cryptography is also divided into two categories, block ciphers and stream ciphers. In block ciphers, the input is divided into blocks of fixed size and encryption and/or decryption is performed on the whole block. In a stream cipher, input is a continuous stream of bits. At each step (or clock), a random bit is generated by the stream cipher. A bit wise Xor of the input and the generated bit makes the output of the encryption or decryption.

Among different kinds of cryptographic methods, stream ciphers typically consume less power and occupy smaller area on the chip. Due to this fact, stream ciphers are attractive in many low power designs. Notable examples of low power circuits are used in RFID-tags, smart-cards, and wireless sensor networks. Because of these characteristics of stream ciphers, the improvement of security in stream ciphers has been intensively researched in recent years.

A prominent example for a stream cipher is the A5/1 cipher, which is part of the GSM mobile phone standard and is used for voice encryption [5]. Another notable application of stream ciphers is the E0 cipher used in bluetooth data transferring [6]. Although, stream ciphers are sometimes also used for encrypting Internet traffic, especially the stream cipher RC4, in practice, block ciphers are used more than stream ciphers for Internet communications [7].

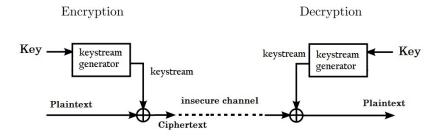

Stream ciphers are basically random bit generator state machines. The output of the state machine is called the *keystream*. At each clock, encryption or decryption is achieved by adding (Xoring) a bit from a keystream to a plaintext bit. Hence, both parties of the communication should be synchronized. The process is shown in Figure 1.1.

In order to generate random bit values, linear feedback shift registers (LFSRs) are widely used in stream ciphers. LFSRs as a building block of many stream ciphers, can generate a good pseudo-random sequence. The other advantage of using LFSRs in stream ciphers is straightforward implementation in hardware. One general architecture to generate keystream in stream ciphers is called a combination generator and uses multiple LFSRs or nonlinear feedback shift registers (NLFSRs) combining their output bit values to generate the stream cipher's keystream. Notable examples

Figure 1.1: General architecture of stream ciphers

of this architecture are A5/1, A5/2 [5], E0 [6], Grain [8] and Trivium [9].

Cryptanalysis is divided into two classes. The first class is referred to as mathematical attack (or classical cryptanalysis) and is based on a combination of algebraic, statistical and numerical techniques. Well-known examples of mathematical attacks on stream ciphers are the algebraic attack, correlation attack, fast correlation attack and distinguishing attack. The second class is called *side channel analysis* (SCA) which is based on gaining information from physical implementation of cryptosystem, such as power consumption, timing information and electromagnetic leaks.

For an SCA attack, the attacker should have physical access to the hardware implementation of the cryptographic circuit and the ability to measure the physical characteristics of the hardware. Wide access to hardware systems such as wireless sensor nodes, RFID-tags and smart-cards make many applications vulnerable to side channel analysis attack. Also, advancements in technology provides many measuring devices with high accuracy at low cost for small labs and personal purpose. The physical access to the target devices and accurate measuring devices increase the necessity of studying side channel analysis.

In this dissertation, we will investigate the application of side channel analysis, in particular power analysis, to stream ciphers constructed using feedback shift registers.

## Chapter 2

# Background

This chapter presents some basic concepts of stream ciphers and side channel analysis attacks. As well, it introduces the notion of the linear feedback shift register (LFSR) and the nonlinear feedback shift register (NLFSR) as basic components of many stream ciphers. Grain, as a test bench for our cryptanalysis techniques, is described and some preliminaries of classical attacks applied to stream ciphers and side channel analysis are presented.

## 2.1 Linear and Nonlinear Feedback Shift Registers

Linear feedback shift registers are widely used as a basic component of a keystream generator in many proposed stream ciphers [2], due to their simple hardware structure and the good pseudo-random properties of the generated sequence. A right-shifting LFSR of size L consists of L bits and the output of each step (i.e., as the result of a triggering clock edge in synchronous sequential digital logic hardware) is the rightmost bit. The bit values are shifted to the right at each step and a new bit is injected into

the leftmost bit of the register after being produced as a linear combination of bits currently stored in the register. It is well known that if the feedback is chosen as a primitive polynomial, the LFSR makes a sequence of bits with a maximal period of  $2^L - 1$  [10, 11, 12]. Using the feedback coefficients, we can give a compact description of an LFSR through its feedback polynomial.

The value of the *i*-th register bit at time t is represented as  $s_t(i)$ . The content of the register at time t is  $S_t = (s_t(L-1), s_t(L-2), s_t(L-3), ..., s_t(0))$ . This is called the *state* of the LFSR at time t. The first L bit values of the LFSR,  $S_0 = (s_0(L-1), s_0(L-2), s_0(L-3), ..., s_0(0))$ , are loaded into the register at the start, and is denoted as the *initial state* of the LFSR.

LFSRs are used as a building block in many applications. Although they are designed for hardware, they can be efficiently implemented in software. In software, a finite field corresponding with the word size can be used efficiently to implement LFSRs. For instance, a 64-bit LFSR can be implemented easily on a 64 bit processor.

Since the register bit values and resulting outputs are generated from the linear combination of the previous L bit values, the register value of the LFSR at a particular point in time can easily be derived from any previous or following sequence of L consecutive bits of output. Hence, in order to increase the security, some stream ciphers use nonlinear feedback shift registers, NLFSRs. In an NLFSR, the feedback is a nonlinear combination of bit values. Although the nonlinear feedback makes the analysis of the output stream more difficult, it also reduces the output sequence period below the maximal value of  $2^L - 1$  [11, 12].

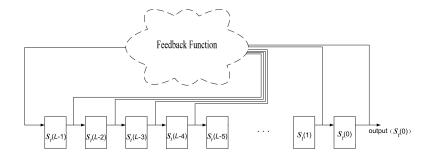

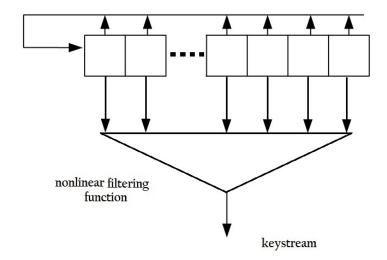

The general structure of an LFSR or NLFSR is shown in Figure 2.1, where each square represents a register bit or D flip-flop.

Figure 2.1: Overall architecture of LFSR or NLFSR

#### 2.2 Grain

In 2004, the European Network of Excellence in Cryptology, ECRYPT, launched a call for stream cipher proposals named eSTREAM [13]. The candidate stream ciphers were submitted in May 2005. The candidates were divided into software oriented and hardware oriented stream ciphers.

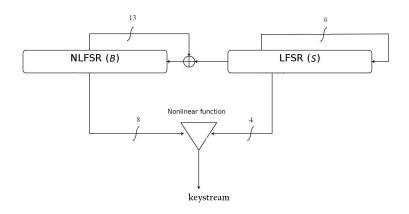

Grain is a light-weight stream cipher, first proposed by M. Hell, T. Johansson and W. Meier to eSTREAM. The original Grain [14] (now referred to as Grain version 0 or Grain-v0) uses an 80-bit key and a 64-bit *initialization vector* (IV). The IV is a publicly known value and used along with the secret key, to fill the internal state or register bits of the stream cipher. Grain has 160 bits of internal state including an 80 bit LFSR and an 80 bit NLFSR. The generated keystream bit at each clock pulse is a nonlinear combination of some LFSR and NLFSR bits. A slightly modified version (with small changes to the output function and the nonlinear feedback function), referred to as Grain version 1 or Grain-v1 [8] has been selected for the hardware portfolio by the eSTREAM project. In addition to Grain-v0 and Grain-v1, a version of Grain with 128 bit key proposed in [15] is called Grain-128. It includes a 128

Figure 2.2: Architecture of Grain stream cipher

bit LFSR and a 128 bit NLFSR and nonlinear combination function to generate keystream bits. In this dissertation, we only study Grain-v0 and Grain-v1, however the proposed methods are applicable to Grain-128. The overall architecture of Grain-v1 is shown in Figure 2.2. Let  $S_t$  and  $B_t$  denote the 80-bit LFSR and NLFSR states, respectively, and  $s_t(i)$  and  $b_t(i)$ ,  $0 \le i < 80$ , represents the value of bit i of  $S_t$  and  $B_t$  at time t.

The primitive polynomial of the LFSR for both Grain-v0 and Grain-v1 is

$$x^{80} + x^{67} + x^{57} + x^{42} + x^{29} + x^{18} + 1 = 0 (2.1)$$

and the update function or feedback of the LFSR is

$$s_t(80) = s_t(62) \oplus s_t(51) \oplus s_t(38) \oplus s_t(23) \oplus s_t(13) \oplus s_t(0)$$

(2.2)

where  $\oplus$  represents Xor operation. The expression of the feedback function for the

NLFSR of Grain-v0 is given by

$$b_{t}(80) = s_{t}(0) \oplus b_{t}(62) \oplus b_{t}(60) \oplus b_{t}(52) \oplus b_{t}(45) \oplus b_{t}(37) \oplus b_{t}(33) \oplus b_{t}(28)$$

$$\oplus b_{t}(21) \oplus b_{t}(15) \oplus b_{t}(9) \oplus b_{t}(0) \oplus b_{t}(60) \cdot b_{t}(63) \oplus b_{t}(37)$$

$$\cdot b_{t}(33) \oplus b_{t}(9) \cdot b_{t}(15) \oplus b_{t}(45) \cdot b_{t}(52) \cdot b_{t}(60) \oplus b_{t}(33) \cdot b_{t}(28)$$

$$\cdot b_{t}(21) \oplus b_{t}(9) \cdot b_{t}(28) \cdot b_{t}(45) \cdot b_{t}(63) \oplus b_{t}(60) \cdot b_{t}(52) \cdot b_{t}(37) \cdot b_{t}(33)$$

$$\oplus b_{t}(63) \cdot b_{t}(60) \cdot b_{t}(21) \cdot b_{t}(15) \oplus b_{t}(63) \cdot b_{t}(60) \cdot b_{t}(52) \cdot b_{t}(45) \cdot b_{t}(37)$$

$$\oplus b_{t}(9) \cdot b_{t}(15) \cdot b_{t}(21) \cdot b_{t}(28) \cdot b_{t}(33) \oplus b_{t}(21) \cdot b_{t}(28) \cdot b_{t}(37)$$

$$\cdot b_{t}(45) \cdot b_{t}(52). \tag{2.3}$$

Note that the generation of  $b_t(80)$  involves a bit from the LFSR in addition to the NLFSR feedback. The keystream output bit of Grain-v0 at time t, denoted as  $z_t$ , is derived from the current LFSR and NFSR states bits as follows:

$$z_{t} = b_{t}(0) \oplus s_{t}(25) \oplus b_{t}(63) \oplus s_{t}(64) \cdot s_{t}(3) \oplus s_{t}(64) \cdot s_{t}(46)$$

$$\oplus s_{t}(46) \cdot s_{t}(25) \cdot s_{t}(3) \oplus s_{t}(64) \cdot s_{t}(46) \cdot s_{t}(3) \oplus b_{t}(63)$$

$$\cdot s_{t}(46) \cdot s_{t}(3) \oplus b_{t}(63) \cdot s_{t}(64) \cdot s_{t}(46)$$

$$(2.4)$$

Due to the weak design of Grain-v0, it was cryptanalyzed in [16, 17, 18]. Subsequently,

in Grain-v1 the feedback function of the NLFSR and output function changed to

$$b_{t}(80) = s_{t}(0) \oplus b_{t}(62) \oplus b_{t}(60) \oplus b_{t}(52) \oplus b_{t}(45) \oplus b_{t}(37) \oplus b_{t}(33) \oplus b_{t}(28)$$

$$\oplus b_{t}(21) \oplus b_{t}(14) \oplus b_{t}(9) \oplus b_{t}(0) \oplus b_{t}(60) \cdot b_{t}(63) \oplus b_{t}(37)$$

$$\cdot b_{t}(33) \oplus b_{t}(9) \cdot b_{t}(15) \oplus b_{t}(45) \cdot b_{t}(52) \cdot b_{t}(60) \oplus b_{t}(33) \cdot b_{t}(28)$$

$$\cdot b_{t}(21) \oplus b_{t}(9) \cdot b_{t}(28) \cdot b_{t}(45) \cdot b_{t}(63) \oplus b_{t}(60) \cdot b_{t}(52) \cdot b_{t}(37) \cdot b_{t}(33)$$

$$\oplus b_{t}(63) \cdot b_{t}(60) \cdot b_{t}(21) \cdot b_{t}(15) \oplus b_{t}(63) \cdot b_{t}(60) \cdot b_{t}(52) \cdot b_{t}(45) \cdot b_{t}(37)$$

$$\oplus b_{t}(9) \cdot b_{t}(15) \cdot b_{t}(21) \cdot b_{t}(28) \cdot b_{t}(33) \oplus b_{t}(21) \cdot b_{t}(28) \cdot b_{t}(37)$$

$$\cdot b_{t}(45) \cdot b_{t}(52) \tag{2.5}$$

and

$$z_{t} = b_{t}(1) \oplus b_{t}(2) \oplus b_{t}(4) \oplus b_{t}(10) \oplus b_{t}(31) \oplus b_{t}(43) \oplus b_{t}(56)$$

$$s_{t}(25) \oplus b_{t}(63) \oplus s_{t}(64) \cdot s_{t}(3) \oplus s_{t}(64) \cdot s_{t}(46) \oplus s_{t}(46)$$

$$\cdot s_{t}(25) \cdot s_{t}(3) \oplus s_{t}(64) \cdot s_{t}(46) \cdot s_{t}(3) \oplus b_{t}(63) \cdot s_{t}(46)$$

$$\cdot s_{t}(3) \oplus b_{t}(63) \cdot s_{t}(64) \cdot s_{t}(46). \tag{2.6}$$

The LFSR feedback remained unchanged.

Before any keystream is generated, the cipher must be initialized with a key and an IV. Let the bits of the key, K, be denoted  $k_i$ ,  $0 \le i < 80$ , and the bits of the IV be denoted  $IV_i$ ,  $0 \le i < 64$ . The initialization of the key is done as follows:

$$b_0(i) = k_i, \quad 0 \le i < 80$$

$s_0(i) = IV_i, \quad 0 \le i < 64$

$s_0(i) = 1, \quad 64 \le i < 80$

The cipher is clocked 160 times without producing any keystream. The output function is fed back and Xored with the input of both the LFSR and NLFSR.

The most successful documented attack on Grain is reported in [17]. It is applicable on Grain-v0. The attackers use second order fast correlation attack to calculate the LFSR state bits and using a simple technique they obtain the NLFSR state bits. The complexity of the proposed attack is  $2^{43}$  operations and requires  $2^{38}$  known keystream bits. As described above, due to the changes in the output function and the NLFSR feedback, this attack is not applicable to Grain-v1.

Another proposed attack on Grain is the time-memory trade-off attack. In [19], a time/memory/data trade off attack on stream ciphers has been analyzed and, using this approach, it is shown in [20] that for 160 state bits of Grain-v1, as an example of the trade offs, an attack can be mounted with a preprocessing complexity of 2<sup>103</sup>, a time complexity of 2<sup>78</sup> and the required memory and keystream data of 2<sup>64</sup> and 2<sup>57</sup>. Further, in [20], a guess-and-determine method is used so that the complexities are improved to 2<sup>71</sup> for time complexity and required memory, 2<sup>106.5</sup> for preprocessing complexity, and 2<sup>53.5</sup> for required keystream. Since the key size for Grain-v1 is 80 bits, the total time complexity (considering both preprocessing time and runtime) of the proposed time-memory trade off attacks on Grain-v1 is worse than exhaustive key search. Currently the most efficient known attack on Grain-v1 and Grain-128 are still exhaustive key search [21].

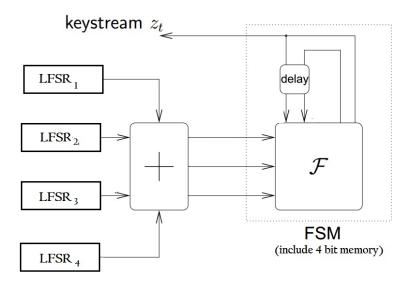

Figure 2.3: Architecture of E0 stream cipher

#### 2.3 E0

E0 is another type of stream cipher. It is used in Bluetooth for wireless communication [6]. E0 has four LFSRs and four bit registers as memory. Figure 2.3 illustrates the cipher. The four-bit memory,  $c_t$ , causes the output of the cipher to depend on the current and the former state of the LFSRs. The lengths of the LFSRs are  $L_1 = 25$ ,  $L_2 = 31$ ,  $L_3 = 33$  and  $L_4 = 39$ . The key size is  $L_1 + L_2 + L_3 + L_4 = 128$ . At each step the LFSRs are clocked once. The output of the LFSRs and the current values of the memories are combined to make the keystream (using a nonlinear function F). Then new value of memory is updated using current value of the memory and the summation of the four LFSR outputs.

Using an algebraic attack on E0, generates  $2^{54.51}$  monomials. The number of required known keystream bits for algebraic attack is  $2^{23}$  [22]. However the best cryptanalysis result belongs to a conditional correlation attack. In [23], it has been

Figure 2.4: General architecture of LILI-128

shown that knowing the first 24 bits of  $2^{23.5}$  frames, we can break E0 with the complexity of  $2^{38}$ .

## 2.4 LILI-128

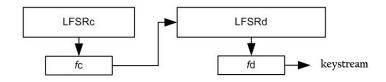

LILI-128 [24] consists of two LFSRs ( $LFSR_c$  and  $LFSR_d$ ).  $LFSR_c$  is 39 bits in length and controls the clock of  $LFSR_d$  which is 89 bits in length. The bit values of  $c_{12}$  and  $c_{20}$  in  $LFSR_c$  are passed through a function with two bits output, to determine whether  $LFSR_d$  should be clocked once, twice, thrice or four times to produce keystream bits. The number of clocks,  $f_c$ , for  $LFSR_d$ , is calculated by

$$f_c = 2 \times c_{20} + c_{12} + 1. (2.7)$$

The designers of LILI-128 publicized all the structure of the clock control subsystem and structure of the data generation subsystem. In Figure 2.4, the general structure of LILI-128 has been shown. LILI-128 was broken using Matlab software [25], on a personal laptop, given 2<sup>12</sup> bits in about 1.7 hours by reconstructing its nonlinear filter function [26].

## 2.5 Side Channel Analysis

The low complexity of stream ciphers allows a straightforward approach to implementation in comparison to block ciphers. However, their straightforward design makes them vulnerable to side channel analysis attacks [27]. In reality, cryptographic algorithms are implemented in software or hardware on a physical device. Regardless of the robustness of resistance of a cipher to mathematical attacks, any implementation of a cipher can lead to new vulnerabilities called side channel analysis attacks. Side channel analysis has been an active area since 1996, when Paul Kocher published his paper on using timing information to attack the RSA, DSS and Diffie-Hellman public key cryptography algorithms [28].

In these attacks, a number of physical measurements of the cryptographic unit are made, for example power consumption, computing time or EMF radiation. These measurements are made over a large number of encryptions and then, using statistical techniques, the secret key embedded inside the cryptographic core is uncovered. These attacks work because there is a correlation between the physical measurements of consumed power taken at different points during the computation and the internal state of the processing device, which is itself related to the secret key. For example, in a smart-card when data is loaded from a memory, the memory bus has to carry the value of the data, taking an amount of power that depends on the data value [29, 30]. Since, the load instruction always happens at the same point within the computation, one can produce correlations between various runs of the application, eventually giving away the secret key of the smart-card.

Typically, in cryptanalysis, attackers try to find the key, or in the case of stream

ciphers, the state bits. Many different methods have been used to cryptanalyze cryptographic algorithms. Using side channel information, the most well known attacks on cryptographic hardware are timing attack, template attack, power analysis and electromagnetic leakage attack.

#### 2.5.1 Timing Attack

Timing attacks enable an attacker to extract secret information in a security system by observing the time it takes the system to respond to various queries or perform the cryptographic algorithm. The notable example of timing attack is timing attack of ECC [31] and RSA [28, 32]. The main operation in ECC is the double-and-add algorithm. The double-and-add algorithm is a series of point addition and point doubling over the curve. Point addition and point doubling include a series of multiplications, squaring, additions and divisions (or inversions) over the finite field. Execution of point doubling takes less time than point addition. For example, the ECC core implemented in [33] executes a point addition in 103  $\mu$ s and a point doubling in 76  $\mu$ s over GF(P). Measuring the execution time of ECC, the attacker can guess the number of executed point addition and point doubling and calculate the key [31, 34].

## 2.5.2 Template Attack

A template attack is a strong probabilistic method for side channel analysis attack. It works by building up a set of templates for an intermediate value using a large number of acquired traces, where a trace is a recording of side channel information such as power consumption of the device being attacked while it is executing an

algorithm. The classification stage then matches traces to a particular template using a probability distribution. The correct key value should be returned with a higher probability than the incorrect values. The computationally intensive and time consuming template building stage need only be completed once for a particular device. The same templates can then be used to mount multiple attacks on identical devices [35, 36].

#### 2.5.3 Power Analysis Attack

A power analysis attack is a type of side channel analysis attack which assumes that the use of different keys implies differences in the power consumption. In this dissertation, we focus on side channel analysis attack based on gaining information from consumed power of the circuit. However, an electromagnetic leakage attack, is very similar in nature to power analysis attacks. In an electromagnetic leakage attack, the attacker measures the electromagnetic radiation of the chip to infer the internal data of the registers.

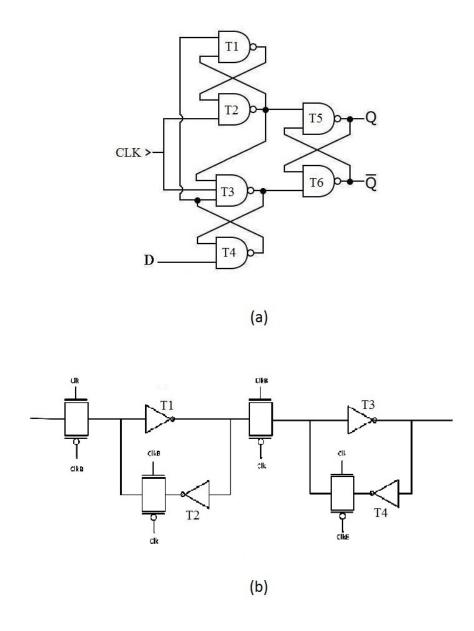

CMOS (Complementary Metal Oxide Semiconductor) is the dominant technology for ASIC (Application Specific Integrated Circuit) purposes. Minimal power consumption at steady state conditions determines the success of the technology in many present day consumer electronics. Unfortunately, the power consumption of this technology has a dependency on the data. This makes the implemented cryptographic algorithm in CMOS technology vulnerable to the side channel analysis attack based on power consumption.

As described in [37, 38, 39, 40], the major power consumption of transistors in a

CMOS circuit is dynamic power consumption. Dynamic power dissipation happens every time the state of a transistor changes (i.e. switches from zero to one or one to zero) causing the charge or discharge of the load capacitance. At the gate level, when the output of a gate changes, the state of its transistors changes. In other words, changing the output of a logic gate causes power dissipation in the circuit. In sequential circuits, the state of the circuit changes at the clock edges. Hence, the main dynamic power dissipation in sequential circuits happens at the triggering edges of the clock.

In power analysis, the attackers use the dynamic power consumption of the circuit to guess the number of changing gates and state bits of the circuit. There are two major methods that consider dynamic power dissipation of the circuit to recover the state bits or secret key of the cryptographic circuits, simple power analysis (SPA) and differential power analysis (DPA). While SPA directly uses the power consumption measurements to identify relevant power fluctuations related to cipher data, DPA uses statistical analysis and error correction techniques to extract information correlated to the state bits of the circuit. In the following sections, we review these two methods.

#### 2.5.3.1 Simple Power Analysis

Previously proposed simple power analysis cryptanalysis of stream ciphers suggest using the dynamic power consumption measurements at the triggering edge of the clock (which we shall assume is the rising edge) to analyze the stream cipher. In the following, we will review the proposed analysis in [41] which is applicable to filter generator stream ciphers based on one LFSR and a nonlinear filtering function (Figure 2.5). Practical stream ciphers with this structure include Crypt-1 [42] and

Figure 2.5: Architecture of filter generator stream cipher

Toyocrypt [43]. In such ciphers, the cipher key is typically used to initialize the bits of the LFSR. It should be noted that the attack of [41] is an idealized attack, assuming perfect mapping between power consumption information and cipher data.

During each clock cycle, assume each bit value in the LFSR is shifted to the right and the leftmost bit of the LFSR is updated with a linear combination of current register bit values (the feedback function in Figure 2.1). Changing the value of each bit in the register is due to change in gate outputs and transistor states and causes dynamic power consumption. At clock cycle t, the current state is represented as  $S_t$  and the state for the next clock cycle is given as  $S_{t+1}$ . The Hamming distance between  $S_t$  and  $S_{t-1}$  is given as  $HD_t$  where  $HD_t$  is calculated from

$$HD_t = \sum_{i=0}^{L-1} (s_t(i) \oplus s_{t-1}(i)), \tag{2.8}$$

where  $s_t(i)$  represents the value of bit i of  $S_t$  with  $s_t(0)$  being the rightmost bit of the

LFSR,  $s_t(L-1)$  being the leftmost bit, and  $\oplus$  representing Xor.

According to the Hamming distance power model used in the analysis [41], the dynamic power consumption of the cipher at clock cycle t is proportional to  $HD_t$ . Between two successive clock cycles, the difference between the Hamming distances must be one of three values:  $HD_{t+1} - HD_t \in \{-1, 0, +1\}$ . Defining the theoretical power difference to be  $PD_t$  given by

$$PD_t = HD_{t+1} - HD_t, \tag{2.9}$$

it can be seen that  $PD_t$  is proportional to the difference of the measured dynamic power consumption at two consecutive clock cycles at times t and t + 1, which is an analog variable in watts and referred to as  $MPD_t$ . Simply,  $PD_t \propto MPD_t$ .

Substituting equation (2.8) into (2.9) results in (after simplifications)

$$PD_t = [s_{t+1}(L-1) \oplus s_t(L-1)] - [s_t(0) \oplus s_{t-1}(0)], \tag{2.10}$$

where the new bit value for state t+1,  $s_{t+1}(L-1)$ , will be the new value of bit L-1 based on the values of  $S_t$ . Considering operations over GF(2), we can write

$$|PD_t| = s_t(L) \oplus s_{t-1}(L) \oplus s_t(0) \oplus s_{t-1}(0),$$

(2.11)

where we now denote  $s_{t+1}(L-1)$  as  $s_t(L)$  and  $s_t(L-1)$  as  $s_{t-1}(L)^{-1}$ . If the measured dynamic power consumption of the LFSR at clock cycle t is equal to the measured dynamic power consumption at clock cycle t+1 (that is,  $MPD_t \approx 0$ ), then we can conclude  $PD_t = 0$  and write  $s_t(L) \oplus s_{t-1}(L) \oplus s_t(0) \oplus s_{t-1}(0) = 0$  and, if the measured 1 In general, we can write  $s_{t+j}(i) = s_t(i+j)$  with  $s_t(i+j)$  representing the (i+j)-th bit following bit  $s_t(0)$  in the LFSR/NLFSR sequence.

dynamic power consumption at time t and t+1 are not equal (that is,  $MPD_t \neq 0$ ), we can conclude  $PD_t \neq 0$  and write  $s_t(L) \oplus s_{t-1}(L) \oplus s_t(0) \oplus s_{t-1}(0) = 1$ .

It is known that, for any t, the bit values of  $S_t$  can be written as a linear function of the initial register state  $S_0$  bits, that is, bits  $\{s_0(i)\}$ , where  $0 \le i < L$ . Hence, for a stream cipher constructed as a nonlinear filter generator using one LFSR and a nonlinear filtering function [2], analyzing L power difference values, it is straightforward to find the initial L bit values of the LFSR and thereby determine the complete keystream sequence [41]. For this purpose, we can collect enough power samples to derive L power difference values and write L equations similar to equation (2.11), relating  $S_t$  through the linear expressions of the LFSR to the bits of  $S_0$ . Then we have a linear system of equations with L unknown variables and L equations, which is easily solved to determine the initial state of the LFSR,  $S_0$ , effectively finding the cipher key which is used to initialize  $S_0$  in a typical stream cipher. Equivalently, finding the L bit values of the LFSR at any time t is sufficient to have broken the cipher, as all subsequent keystream bits are easily determined.

It is important to note that the described SPA method assumes that the analysis is capable of exactly determining theoretical power difference values (such that  $|PD| \in \{1,0\}$ ) from real power consumption measurements (which are analog values in units of watts). The theoretical PD values are then used directly to determine the register bit values. In practice, this is somewhat challenging and methods to overcome this challenge are discussed later in this dissertation.

#### 2.5.3.2 Differential Power Analysis

Another approach to recover the state bits of a cryptosystem is called differential power analysis. It was proposed at first in 1999 [44]. Extensive research on DPA attacks shows its effectiveness even if the recorded power traces are inaccurate. DPA is more applicable to block ciphers and little research has investigated the application of DPA on stream ciphers. Notable reports of applying DPA on stream ciphers are [42], [45] and [46]. In [45], a theoretical DPA attack on A5/5 and E0 is offered. In [46], a known IV attack to Grain is proposed and [42] has offered a DPA attack of LFSR based stream ciphers, such as Crypto-1. In the proposed DPA attacks, it is necessary for the attacker to be able to perform encryption with different initialization vectors. That is, the cipher needs to be resynchronized many times. This limits the applicability of DPA in stream ciphers.

A precondition for a differential power analysis attack is that adversary knows the plaintext and the ciphertext to obtain the key. Let's assume an internal state bit of the cipher, is computed by  $F(p_i, K)$ , where F is a Boolean function,  $p_i$  is the i-th plaintext and K is the key. In DPA we divide the key to subkeys, k, and guess an initial value for each subkey. Then we check whether our guess was right or wrong. To check the correctness of the guess, for random input plaintext,  $p_i$ , we compute  $F(p_i, k)$  (for the guessed value of the subkey) and we divide the results into two parts,  $S_0$  and  $S_1$ .  $S_0$  is the consumed power corresponds of set of computed values where  $F(p_i, k) = 0$  and  $S_1$  is for  $F(p_i, k) = 1$ . For all  $p_i$ , the difference between the mean values of two sets can be calculated

$$\delta_k = \sum_{i \in S_1} \frac{t_i}{|S_1|} - \sum_{i \in S_0} \frac{t_i}{|S_0|} \tag{2.12}$$

where  $t_i$  is the measured value of the cipher power for  $p_i$ . Every wrong guessed bit of subkey, k, reduces the absolute mean value ( $|\delta_k|$ ) while the correct bit guess increases  $|\delta_k|$ , in the above equation. To find the correct subkey, we have to test all possible values for k and the greatest mean value of (2.12) shows the right guess of the subkey. Increasing the number of plaintexts helps the attacker to obtain more accurate results and decreases the effect of noise or inaccurate measurements. For example, in AES, F is defined as a function of 8 bits of subkey and using the above process we can recover the eight bits of AES at one time [47, 48].

## 2.6 Classical Attack of Stream Ciphers

The proposed classic mathematical attacks of stream ciphers are classified as known-plaintext attacks. In this section, we briefly review the basic concepts of the time-memory trade off attack, the algebraic attack, the correlation attack and the fast correlation attack.

#### 2.6.1 Time-Memory Trade off Attack

The time-memory trade off attack is a known plaintext attack proposed in [49] and includes two phases. In the precomputation step, the attacker explores the general structure of the stream cipher and makes a table which consists of m bits of input and n bits of output. In other words, the attacker lists all possible values of m bits as input and calculates their corresponding outputs. In the second phase, the attacker, divides his output keystream to n-bit blocks and finds the corresponding m bit inputs in the table.

To make the attack more efficient, the attacker should make the table as big as possible and use some proposed techniques to sort them (in the precomputation phase). Increasing the table size causes increase in the required memory while reducing the required time to attack. Efficient implementation techniques have been offered in several papers, such as [19, 50], to make this attack practical for stream ciphers. A practical analysis of time-memory trade off attack of stream ciphers is proposed in [20] on Grain. It has been shown that recovering the state bits of Grain-v1 is possible with the memory and time complexity of  $2^{71}$  and  $2^{53.5}$  known keystream bits. The precomputation step needs  $2^{106.5}$  steps.

#### 2.6.2 Algebraic Attack

The algebraic attack is a powerful tool to cryptanalyze many stream ciphers previously believed very secure. The main idea behind this method is finding and solving a system of multivariate polynomial equations over a finite field. In other words, the algebraic attack reduces the cryptanalysis of the cipher into the problem of finding and solving a system of polynomial equations.

Solving a system of nonlinear polynomial equations over a finite field in general is an NP hard problem. But not all instances of NP hard problems are hard to solve. It might be possible to express a cipher in such a way that it is easier to solve than in exponential time. Solving such a system is called an algebraic attack. These attacks are motivated by the fact that the equation systems derived from the cipher are both sparse and overdefined [51]. The typical approach in an algebraic attack is converting the system of nonlinear equations to a system of linear equations. This process

is called linearization. It causes a significant increase in the number of unknown variables. In Appendix A, we have provided a brief review to the proposed algebraic attacks called the relinearization and XL methods.

The applicability of the algebraic attack investigated in many stream ciphers such as HFE [52], Toyocrypt [53], Sfinks <sup>1</sup> [54], LILI-128 [55] and E0 [56]. Application of the algebraic attack is not limited to stream ciphers. Some research has been done to extend it to block ciphers and even public key cryptosystems as well. For example, in [57], the applicability of algebraic attack to Advanced Encryption Standard (AES) is studied. An example of applying algebraic attack to a public key cryptosystem is [58] in which they use algebraic attack to break MQQ public key cryptosystem.

#### 2.6.3 Correlation and Fast Correlation Attack

Another powerful method of cryptanalyzing stream ciphers constructed of multiple FSRs is called the correlation attack. It is based on a divide-and-conquer approach. It has been shown that, for many LFSR based stream ciphers, there exists a measure of correlation between the keystream sequence and the outputs of the LFSRs, making it possible to determine the initial state of each of the LFSRs, independently [59]. Further it is possible to define higher order correlation attacks [60]. If there is a correlation between the keystream sequence and the addition of some LFSR state bits over the LFSR, still the attacker can use correlation attack. This is called a second order correlation attack.

The fast correlation attack is a more developed correlation attack, proposed for LFSR based stream ciphers. In the fast correlation attack, the attacker considers the

<sup>&</sup>lt;sup>1</sup>an LFSR based stream cipher

linear relation between LFSR bits. Using the linear relation between LFSR bits, the attacker can reduce the timing complexity of the correlation attack. In Chapters 6 and 7, we have provided a more detailed review for correlation and fast correlation attacks.

## 2.7 Summary

In this chapter, we have reviewed the preliminaries for stream ciphers and side channel cryptanalysis. The main target of side channel cryptanalysis in our research is feedback shift register (FSR) based stream ciphers. We have studied the LFSR and NLFSR as a main building block of modern stream ciphers and Grain as an example of that. Also, we have studied the proposed simple power analysis for an LFSR based stream cipher, which has limited applicability on recent stream ciphers but is an important foundation for the work in this thesis. In the next chapters, we will discuss the development of the simple power analysis and propose new techniques which are applicable to practical implementations of modern stream ciphers.

# Chapter 3

# Applicability of Simple Power

# Analysis to Stream Ciphers

# Constructed Using Multiple LFSRs

As described in Section 2.5 the applicability of a simple power analysis, SPA, on stream ciphers has been identified in [41]. The proposed method is applicable to stream ciphers with just one linear feedback shift register. Since a number of modern stream ciphers use more than one LFSR, the direct methodology in [41] has limited applicability. In this chapter, we propose a method based on simple power analysis to attack stream ciphers with multiple LFSRs such as E0 [6]. Further, we consider the applicability of the attack to irregular clocking stream ciphers by examining LILI-128 [24]. It should be noted the proposed approach in this chapter is applicable in ideal environment, where the measured power of the circuit can be mapped to the theoretical state values of the circuit. In other words, there is no inaccuracy between power

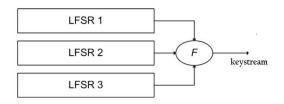

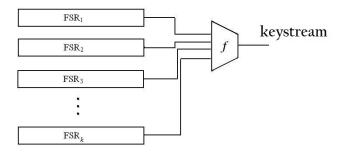

Figure 3.1: A stream cipher keystream generator with three LFSR measurements and theoretical power differences. This work was initially presented in [61].

# 3.1 Extension of Simple Power Analysis to Ciphers with Multiple LFSRs

Consider now stream ciphers constructed from multiple LFSRs and a nonlinear combining function, referred to as a combination generator. An early example of such stream ciphers is the Geffe generator, which is constructed with three LFSRs and a nonlinear combining function [62]. We now consider the novel extension of the attack in [41] to such ciphers. A system with three LFSRs is illustrated in Figure 3.1, where F represents a nonlinear combining function.

As described before, in classical simple power analysis it is assumed the power consumption of the circuit at the rising edge of the clock is for D-flip flops. The power consumption of the other components has been ignored at the rising edge of the clock.

For simplicity in the discussion, let us assume a stream cipher with two LFSRs,  $LFSR_S$  and  $LFSR_R$ , and bit values  $s_t(i)$  and  $r_t(j)$  where  $0 \le i < N$  and  $0 \le j < M$

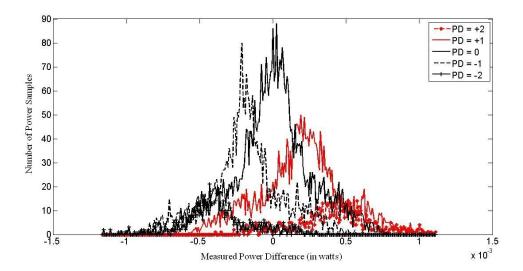

where N and M are the sizes of the LFSRs <sup>1</sup>. The overall power difference of two LFSRs,  $PD_t = HD_{t+1} - HD_t$ , at each clock can now be from  $\{-2, -1, 0, +1, +2\}$ . Since each LFSR could have a power difference of -1, 0 or +1, if the power difference for both LFSRs is the same and equal to -1 or +1, then the overall  $PD_t$  is -2 or +2, respectively.

Although values of  $PD_t = +2$  or -2 indicate that both LFSRs must have non-zero power differences, other values of overall  $PD_t$  will not get us any useful information about the individual LFSRs. For example, if the overall  $PD_t = 0$ , we cannot conclude whether both LFSR power differences are equal to zero or the power difference for one LFSR is equal to -1 and for the other one is equal to +1. Also, if the overall  $PD_t = +1$  or  $PD_t = -1$ , we cannot distinguish for which LFSR the power difference is zero and for which LFSR the power difference is nonzero. However, for each clock cycle where overall  $PD_t = +2$  or  $PD_t = -2$ , based on equation (2.11), we can conclude:

$$s_{t-1}(0) \oplus s_t(0) \oplus s_{t-1}(M) \oplus s_t(M) = 1$$

$r_{t-1}(0) \oplus r_t(0) \oplus r_{t-1}(N) \oplus r_t(N) = 1$  (3.1)

where  $s_t(i)$  and  $r_t(i)$  represent the *i*-th bits of LFSR states at clock cycle t.

for E0 stream cipher, has four LFSRs

To break the stream cipher, we need to determine the M+N bits of the LFSRs at a particular point in time. Hence, we require enough power difference values with  $PD_t = +2$  or  $PD_t = -2$  to obtain linear equations using (3.1) to solve for M+N unknown variables. The minimum number of power difference values to set up the  $\overline{\phantom{a}}$  This method can be used for stream ciphers constructed more than two LFSRs. We will use it

M+N equations is M (if M>N) or N (if N>M). However, the minimum is unlikely to be achieved since usable power difference values must satisfy  $PD_t=+2$  or  $PD_t=-2$ .

When we measure the consumed power of the circuit we should observe roughly five levels of power difference. The largest negative level should be assigned to  $PD_t = -2$  and the largest positive level should be assigned to  $PD_t = +2$ .

The probability of a particular overall  $PD_t = +2$  or  $PD_t = -2$  is equal to  $\frac{1}{8}$ , since this occurs when the individual shift registers both have power differences of +1 or -1, each of which occurs with a probability of  $\frac{1}{4}$ . Hence, on average, we require  $8 \times \max\{M, N\}$  power difference values to derive M + N equations. Letting  $T = \max\{M, N\}$ , given n power difference values, it can be shown that the probability that there are enough usable power differences to form T equations is given by

$$Q_T(n) = \sum_{i=T}^n \binom{n}{i} (\frac{7}{8})^{n-i} (\frac{1}{8})^i.$$

(3.2)

Hence, for T=80 and n=800 power difference values, the probability that 80 equations can be derived is  $Q_{80}(800)=.9877$ . Assuming that all equations derived from the power differences are linearly independent, we can solve the system for the M+N initial state bits of the two LFSRs by using two systems of equations. The systems of equations are linear and can be solved using appropriate mathematical computation tools such as Sage [63] or algebraic algorithms such as Gaussian elimination. However, the equations derived from the power difference values and the feedbacks are not necessarily all linearly independent. In fact, for an L-bit LFSR, given k randomly generated linear equations of the LFSR initial state bit values, from

[64] the probability that all k equations are linearly independent is

$$P_L(k) = \frac{\prod_{i=0}^{L-1} (2^L - 2^i)}{k! \times {2^{L-1} \choose k}}$$

(3.3)

for  $k \leq L$ .

If k = L, then  $P_L(k)$  gives the probability that L randomly selected equations is enough to solve for the LFSR initial state bits. For example, for k = L = 80,  $P_{80}(80) = .289$ , implying that with 80 equations there is a 28.9% chance of being able to solve uniquely for the 80 state bits of the LFSR. Hence, in general, to ensure that we have a high probability of solving for M + N bits when attacking the cipher based on two LFSRs, we should obtain somewhat more than  $\max\{M, N\}$  equations from the power differences.

Consider now, the estimate of a lower bound on the probability, given k randomly generated linear equations with k > L, of being able to fully solve the system.  $P_L(i, k)$  is defined as the representation of the probability which, given k bits randomly selected from a sequence generated by an L-bit LFSR, it is possible to generate a set of i linearly independent equations. From [64], for  $k \leq L$ ,  $P_L(k, k)$  can be generated:

$$P_L(k,k) = \frac{\prod_{i=0}^{L-1} (2^L - 2^i)}{k! \times {2^{L-1} \choose k}}$$

(3.4)

We are interested in situations where k > L and i = L. Although we will not compute the probability directly in this case, we will derive a lower bound on  $P_L(L, k)$  for k > L.

Consider a set of k-1 linear equations, k > L, formed from bits randomly selected from the sequence of an L-bit LFSR with the unknown variables being the initial Lbits of the LFSR. Assume within the set of k-1 linear equations, there is a subset of i-1 equations,  $i \leq L$ , that are linearly independent. Following the arguments presented in [64], the probability of randomly selecting a k-th linear equation that is linearly independent of all equations in the subset so that a subset of i linearly independent equations is formed is given by:

$$\Gamma_L(i,k) = \frac{\left(2^L - 2^{i-1}\right)}{\left(2^L - k - 2\right)} \tag{3.5}$$

The denominator represents the total number of equations left from which the k-th equation is drawn and the numerator represents the number of equations left which are linearly independent of the equations in the subset. The denominator and numerator are formed by considering that there are a total of  $2^{L-1}$  linear equations of L variables and there are  $2^{i-1} - 1$  equations that are not linearly independent of the subset of i-1 equations. We are specifically interested in cases where  $k \ll 2^{L-1}$  and, hence, since  $i \leq L$ , it is easy to see that  $\Gamma_L(i,k) \geq .5$  and  $\Gamma_L(i,k) \cong .5$  occurs for i = L.

In order to calculate the lower bound on  $P_L(L,k)$  for k > L, we can use

$$P_L(L,k) \ge \max\{P_L(j,j) \times \beta_L(j,k)\} \{0 < j \le L\}$$

(3.6)

where  $P_L(j,j)$  is given by (3.4) and  $\beta_L(j,k)$  is the probability of adding L-j more linear equations to the set of linearly independent equations given k-j more randomly selected equations. Since  $\Gamma_L(i,k) \geq .5$ , we can compute a lower bound on  $\beta_L$  using the binomial distribution:

$$\beta_L(j,k) \ge \sum_{i=L-j}^{k-j} {k-j \choose i} \times 5^{k-j} \tag{3.7}$$

Using two equations (3.7) and (3.6), we can estimate the lower bound on  $P_L(L, k)$  for k > L.

For example, if L=80, it can be shown that obtaining 120 random equations will give a probability of over 99.99% of being able to solve for the 80 unknowns. Hence, for the cipher based on two LFSRs, if  $\max\{M, N\} = 80$  bits, then, from equation (3.2), 1200 power difference values will give a 98.99% probability of obtaining 120 equations, which according to the equations (3.7) and (3.6), will give a probability of 99.99% of being solvable for the LFSR initial state bit values. Hence, for ciphers based on two LFSRs of sizes 80 bits and less, 1200 power samples will give a very high probability of being able to successfully apply SPA.

## 3.2 Application of the Attack to the E0 Stream Cipher

The E0 stream cipher [6] is a well-known stream cipher, used in Bluetooth which is used in short range, high speed communications such as mobile cell phones, PCs, and computer accessories. It is based on four LFSRs ( $LFSR_a$ ,  $LFSR_b$ ,  $LFSR_c$ ,  $LFSR_d$ ) with lengths of 25, 31, 33 and 39 bits [6]. In addition to four LFSRs, four bit registers save the state of the cipher as part of the nonlinear combining function. Hence, the equations used in the simple power analysis should be expanded to these four register bits. The output bit is a combination derived from the current bit values of LFSRs and the former state or register values.

Since at each clock, four LFSRs and four register bits could be changed, the overall  $PD_t$  can be from  $\{\pm 8, \pm 7, \pm 6, \pm 5, \pm 4, \pm 3, \pm 2, \pm 1, 0\}$ . The useful power differences are  $PD_t = +8$  and  $PD_t = -8$ . When  $PD_t = +8$  or  $PD_t = -8$  we can

conclude:

$$a_{t-1}(0) \oplus a_t(0) \oplus a_{t-1}(25) \oplus a_t(25) = 1$$

$$b_{t-1}(0) \oplus b_t(0) \oplus b_{t-1}(31) \oplus b_t(31) = 1$$

$$c_{t-1}(0) \oplus c_t(0) \oplus c_{t-1}(33) \oplus c_t(33) = 1$$

$$d_{t-1}(0) \oplus d_t(0) \oplus d_{t-1}(39) \oplus d_t(39) = 1$$

$$(3.8)$$

where a, b, c and d represent LFSR state bits. In addition, four equations can be written for the four register bits of the combiner.

Noting that the largest LFSR size is 39 bits based on the discussions in former section, using 60 useful power difference values (i.e.,  $PD_t = +8$  or  $PD_t = -8$ ), with the probability of more than 99.2%, we can find 39 linearly independent equations to solve  $LFSR_d$ . To find 60 useful power differences, equations (3.2) should be modified for E0 to (3.9).

$$Q_T(n) = \sum_{i=T}^n \binom{n}{i} (\frac{254}{256})^{n-i} (\frac{2}{256})^i$$

(3.9)

From Equation (3.9) and (3.3) we can estimate 16000 power difference values results in a probability of 98.0%. Hence, with very high probability, 16000 power samples are enough to attack E0. Once the LFSR bit values are known, the four combining function state bits can be determined by exhaustively testing each possible value.

We can reduce the number of required power samples by determining the smallest LFSR at the first. When we collect enough  $PD_t = +8$  or  $PD_t = -8$  to find 25 linearly independent equations to solve  $LFSR_a$ , we can calculate its PD values and deduct from total PD of the circuit. Then, to obtain the state bits of the other LFSRs we look for  $PD'_t = +7$  and  $PD'_t = -7$ , where  $PD'_t$  is the  $PD_t$  of circuit subtracting the

$PD_t$  of  $LFSR_a$ . With 45 useful power difference values (i.e.,  $PD_t = +8$  or  $PD_t = -8$ ) with the probability of more than 99.5% we have 25 linearly independent equations and we can calculate  $LFSR_a$  state bits. Using equations (3.9) and (3.3) shows 12000 is enough to calculate the state bits of  $LFSR_a$  and then, other LFSR state bits of E0 with a probability higher than 99%.

# 3.3 Application of the Attack to Irregular Clocking Stream Cipher, LILI-128

So far we have described an SPA attack on stream ciphers with regular clocks. In this section, we use SPA to attack a non-regular clocking LFSR stream cipher, LILI-128 [24]. In LILI-128, two LFSRs are employed ( $LFSR_c$  and  $LFSR_d$ ) to generate a random sequence.  $LFSR_c$  is 39 bits in length and controls the clock of  $LFSR_d$  which is 89 bits in length. The bit values of  $c_t(12)$  and  $c_t(20)$  in  $LFSR_c$  are passed through a function with two bits output, to determine whether  $LFSR_d$  should be clocked one, two, three or four times to produce key stream bits [24]. Since it is not known how many bits  $LFSR_d$  is being clocked to produce each output bit, we cannot directly approach the equations for  $LFSR_d$ . Hence, at first we should find the bit values of  $LFSR_c$ .

Two different architectures have been offered for LILI-128 [24]. In the first architecture, two clocks are employed with different speeds. The first clock is used for  $LFSR_c$  and the second one is for  $LFSR_d$  which is four times faster. If  $c_t(12) = 1$  and  $c_t(20) = 1$ , then  $LFSR_d$  is clocked four times. To use simple power analysis and

set up the equations, we should wait until  $PD_t = +2$  or  $PD_t = -2$  at the triggering edge of the first clock (i.e. the clock driving  $LFSR_c$ ). When  $PD_t = +2$  or  $PD_t = -2$ , we can write:

$$c_{t-1}(0) \oplus c_t(0) \oplus c_{t-1}(39) \oplus c_t(39) = 1.$$

(3.10)

No useful information can be obtained for  $LFSR_d$ , because t is not known for  $LFSR_d$ . Hence, at this point we cannot find any equation for  $LFSR_d$ . More information could be obtained by considering power consumption correlated to the  $LFSR_d$  clock. If power consumption could be observed for  $LFSR_d$  between two consecutive clocks of  $LFSR_c$ , indicating four shifts of  $LFSR_d$  we can conclude:

$$c_t(12) = 1$$

(3.11)

$c_t(20) = 1$

Using equation (3.10) and (3.11), we can set up a system of linear equations to find the bit values of  $LFSR_c$ . Finding the bit values of  $LFSR_c$ , we can use the former power difference values to find the equations for bit values of  $LFSR_d$ .

In the second offered architecture for LILI-128 [24], just one clock has been used for both LFSRs.  $LFSR_d$  is implemented using four copies of the feedback function and the irregular clocking is performed in one clock cycle. For this architecture, equation (3.11) can not be used; hence just equation (3.10) could be employed to realize  $LFSR_c$  bit values.

Since the size of  $LFSR_c$  is 39 bits, 60 equations with the probability of more than 99.2% can provide 39 linearly independent equations. In the second architecture, 600 power samples can provide 60 usable power difference values, with the probability of 97.5%. Hence, the second architecture is susceptible to SPA with 600 power samples

with high probability. In the first architecture with the probability of  $\frac{1}{8}$ , equation (3.10) can be obtained and with the probability of  $(\frac{1}{8})(\frac{1}{2})$  equation (3.11) can be employed in the system. After collecting 300 power samples, with the probability of more than 98.2%, 60 equations can be obtained to solve state bits of  $LFSR_c$ .

When bit registers of  $LFSR_c$  are known, finding bits of  $LFSR_d$  is similar to using SPA to attack one LFSR, proposed in [41]. To break  $LFSR_d$ , if we collect 110 equations, with the probability of more than 99% we will have 89 linearly independent equations.

### 3.4 Summary

In this chapter, we have extended the former method of simple power analysis attack proposed for one LFSR-based stream ciphers to ciphers based on multiple LFSRs. Also, we extend the proposed method to stream ciphers with irregular clocking LFSRs.

In order to illustrate the proposed methods, we applied them to well known stream ciphers E0 which includes four LFSRs and four bit registers and LILI-128 which includes two LFSRs, one with irregular clocking. We have shown that E0 could be broken using a few thousand power samples and LILI-128 is susceptible to simple power analysis with few hundred power samples. However, it should be noted that these results are based on the assumption that the Hamming distance model holds. That is, the theoretical power difference, which is related directly to the Hamming distance of the register values between clock cycles, is accurately determined from the analysis of power traces.

## Chapter 4

## Side Channel Analysis of NLFSR

## **Based Stream Ciphers**

An NLFSR has a similar structure to an LFSR as shown in Figure 2.1, except the feedback function is nonlinear. In order to make stream ciphers more secure, particularly against algebraic attack, NLFSRs are widely used in stream ciphers. For example, the Grain stream cipher [8] combines the outputs of an LFSR and NLFSR to produce the keystream. Since in an NLFSR, the feedback is nonlinear, using the described method in Section 2.5 and [41] results in a system of nonlinear equations which are difficult to solve. In a secure NLFSR, the order of equations relating output bits to the initial state bits increases very quickly and makes it difficult to solve the system. Hence, the formerly proposed methods of using simple power analysis for LFSRs are not applicable to NLFSR based stream ciphers. In this chapter we propose a new method to use simple power analysis against NLFSR based stream ciphers. The proposed method is applicable in ideal environments in which the measured power

difference of the circuit matches the theoretical power difference values of the circuit. Then, we apply the proposed method to the Grain stream cipher to get the state bits from power consumption measurements. The results in this chapter were initially presented in [65].

#### 4.1 Idealized SPA Applied to NLFSRs

Since, in a typical stream cipher, the key bits are used to initialize the NLFSR state, finding the state of the NLFSR (i.e., the L bits of the register) at any time is sufficient to break the system and determine the subsequent keystream bits. As in the previous section, we assume that the measured power consumption resulting in the measured power difference at time t,  $MPD_t$ , can be accurately converted to the theoretical power difference,  $PD_t$ . (In subsequent sections, we will discuss practical issues such as the inaccurate determination of  $PD_t$  values.)

Consider a consecutive series of  $PD_t$  values for an NLFSR with the length of L bits and denote the i-th bit of the NLFSR at time t as  $b_t(i)$ . In order to calculate NLFSR bit values, we should modify the former equations proposed in Section 2.5 to analyze an LFSR. Similar to equation (2.10), we can write:

$$PD_t = [b_t(L) \oplus b_{t-1}(L)] - [b_t(0) \oplus b_{t-1}(0)]. \tag{4.1}$$

Then, when  $PD_t = +1$ , we conclude

$$b_t(L) \oplus b_{t-1}(L) = 1$$

$b_t(0) \oplus b_{t-1}(0) = 0$  (4.2)

and, when  $PD_t = -1$ , we can write

$$b_t(L) \oplus b_{t-1}(L) = 0$$

$b_t(0) \oplus b_{t-1}(0) = 1.$  (4.3)

To apply simple power analysis to an LFSR we only used the absolute value of  $PD_t$ . However to apply SPA to an NLFSR, the attacker should consider whether  $PD_t$  is greater or less than zero. When  $PD_t = 0$ , the two bracketed Xor results of equation (4.1) are both equal to either 0 or 1 and we can write

$$b_t(L) \oplus b_{t-1}(L) = b_t(0) \oplus b_{t-1}(0).$$

(4.4)

As long as  $PD_t \neq 0$ , we can find a relation between two consecutive values of the NLFSR bits, using equations (4.2) or (4.3).

To analyze the NLFSR, we must obtain L consecutive bits of the NLFSR. Equations (4.2) and (4.3) could determine the relation between two bits of the NLFSR when  $PD_t = +1$  or  $PD_t = -1$ . However, when  $PD_t = 0$ , we cannot use equations (4.2) and (4.3) directly. Instead, we make use of equation (2.11) for  $PD_t$  and  $PD_{t+L}$  to obtain

$$|PD_{t}| \oplus |PD_{t+L}| = b_{t}(L) \oplus b_{t-1}(L) \oplus b_{t}(0) \oplus b_{t-1}(0) \oplus b_{t+L}(L)$$

$$\oplus b_{t+L-1}(L) \oplus b_{t+L}(0) \oplus b_{t+L-1}(0)$$

$$= b_{t}(0) \oplus b_{t-1}(0) \oplus b_{t}(2L) \oplus b_{t-1}(2L)$$

(4.5)

where we have made use of  $b_{t+j}(i) = b_t(i+j)$ . Also, it can be shown that

$$PD_t + PD_{t+L} = [b_t(2L) \oplus b_{t-1}(2L)] - [b_t(0) \oplus b_{t-1}(0)]. \tag{4.6}$$

The value of  $PD_{t+i}$  must be +1, 0 or -1 implying  $|PD_{t+i}| \in \{0,1\}$ . Since  $|PD_t| \oplus |PD_{t+L}|$  will be either 1 or 0, if  $PD_t = 0$ , then we can write equation (4.2)

or (4.3) for  $PD_{t+L}$  if  $|PD_{t+L}|$  is 1 and using equation (4.5) find the relation between  $b_t(0)$  and  $b_{t-1}(0)$ . For example, let us assume  $PD_t = 0$ . If  $PD_{t+L} = +1$  or -1, then  $b_t(2L) \oplus b_{t-1}(2L)$  and  $b_t(L) \oplus b_{t-1}(L)$  are known from either equation (4.2) or (4.3) (with t replaced with t + L) and since the left side of equation (4.5) is known from power measurements then  $b_t(0) \oplus b_{t-1}(0)$  can be inferred. If  $PD_{t+L} = 0$ , then power differences from cycle t + 2L must be considered.