# SIMULATION OF CURRENT MODE CONTROL SCHEMES FOR POWER FACTOR CORRECTION CIRCUITS

CENTRE FOR NEWFOUNDLAND STUDIES

# TOTAL OF 10 PAGES ONLY MAY BE XEROXED

(Without Author's Permission)

SUBARNA PAL

# SIMULATION OF CURRENT MODE CONTROL SCHEMES FOR POWER FACTOR CORRECTION CIRCUITS

by

© Subarna Pal, B. ENG.

A thesis submitted to the School of Graduate

Studies in partial fulfillment of the

requirements for the degree of

Master of Engineering

Faculty of Engineering and Applied Science

Memorial University of Newfoundland

May 1998

St. John's Newfoundland Canada

National Library of Canada

Acquisitions and Bibliographic Services 395 Wellington Street Ottawa ON K1A 0N4 Caneda Bibliothèque nationale du Canada

Acquisitions et services bibliographiques 395, rue Wellington Ottawa ON K1A 0N4

Your Sie Votre rétérance

Our Sie Notre référence

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

0-612-36162-4

Canadä

### Abstract

This thesis deals with a comparative study of the features of constant frequency and variable frequency current control schemes for power factor correction in AC-DC converter circuits.

Various current control schemes for achieving nearly unity power factor at the input and to minimize the total harmonic distortion (THD) are in use in various applications such as television, radio receivers, AC-motor drives, DC-motor drives and uninterruptible power supplies (UPS).

Analytical models of Constant Frequency Continuous Current (CFCC), Constant Frequency Discontinuous Current (CFDC), Zero-Current Zero-Voltage Switching (ZCS-ZVS) and Variable Current Hysteresis Control (VCHC) are developed and used to evaluate the performance of the power factor correction circuit. The main features of these control schemes are highlighted and the performance characteristics are obtained through computer simulation for the same circuit conditions. Design examples of each control scheme, and power loss calculation associated with the active switching device are also provided. It is shown that active current waveshaping through constant and variable frequency control schemes posseses many attractive features.

## Acknowledgements

I would like to thank and express my indebtedness and heartiest gratitude to Dr. J. E.

Quaicoe for his constant advice, encouragement and guidance throughout the preparation

of this thesis.

I take this chance to express my profound gratitude to my family, especially my youngest sister 'Dola' for their constant encouragement and help during my study in Canada

Thanks are due to the staff at CCAE, faculty and friends for all the useful discussions and suggestions.

Finally, I would like to express my thanks to Memorial University of Newfoundland for the financial support which made this research possible.

# Contents

| Abs  | tract   |         |              |                                                | ii   |

|------|---------|---------|--------------|------------------------------------------------|------|

| Ack  | nowled  | gements |              |                                                | ш    |

| List | of Figu | res     |              |                                                | viii |

| List | of Tabl | es      |              |                                                | xiv  |

| 1    | INT     | RODUC   | TION         |                                                | I    |

|      | 1.1     | Harm    | onic Stand   | ards and Recommended Practices                 | 3    |

|      | 1.2     | Harm    | onic Minir   | nization using Passive Techniques              | 6    |

|      | 1.3     | Curre   | nt Injection | n Method                                       | 7    |

|      | 1.4     | Harm    | onic Minir   | nization using Active Techniques               | 10   |

|      |         | 1.4.1   | Pulse Wi     | dth Modulation Switching of the Converter      |      |

|      |         |         | Devices      |                                                | 10   |

|      |         |         | 1.4.1.1      | Adaptive Phase Control                         | 11   |

|      |         |         | 1.4.1.2      | Predicted Current Control                      | 13   |

|      |         | 1.4.2   | Pulse Wi     | dth Modulation Switching of Auxilliary Devices | 14   |

|      |         |         | 1.4.2.1      | Active Power Factor Correction Circuit         | 15   |

|      |         |         | 1.4.2.2      | Control Schemes for the Single Phase AC-DC     |      |

|      |         |         |              | Converter                                      | 19   |

|   | 1.5 | Thesi | is Objectives                                            | 2  |

|---|-----|-------|----------------------------------------------------------|----|

|   | 1.6 | Thesi | s Outline                                                | 2  |

| 2 | CON | STANT | FREQUENCY CONTROL SCHEMES                                | 2  |

|   | 2.1 |       | tant Frequency Continuous Current Control                | 2  |

|   |     | 2.1.1 | Modelling and Analysis of the Power Circuit              | 2  |

|   |     |       | 2.1.1.1 The ON State                                     | 2  |

|   |     |       | 2.1.1.2 The OFF State                                    | 3  |

|   |     | 2.1.2 | Modelling and Analysis of the Control Circuit            | 3  |

|   |     | 2.1.3 | Determination of the Duty Ratio, D                       | 3  |

|   |     | 2.1.4 | Design Example                                           | 3  |

|   |     | 2.1.5 | Power Loss Calculation of the Boost Switch               | 4  |

|   |     | 2.1.6 | Simulation of the PFC Circuit for the Continuous Current |    |

|   |     |       | Mode Control                                             | 4  |

|   |     |       | 2.1.6.1 Simulation Procedure                             | 4  |

|   |     |       | 2.1.6.2 Simulation Results                               | 49 |

|   | 2.2 | Const | ant Frequency Discontinuous Current Control              | 59 |

|   |     | 2.2.1 | Modelling and Analysis of the Control Scheme             | 6  |

|   |     |       | 2.2.1.1 The ON State                                     | 6  |

|   |     |       | 2.2.1.2 The OFF State                                    | 63 |

|   |     | 2.2.2 | Design Example                                           | 66 |

|   |     | 2.2.3 | Simulation of the PFC Circuit for Discontinuous Current  |    |

|   |     |       | Mode Co      | ntrol                                           | 68  |

|---|-----|-------|--------------|-------------------------------------------------|-----|

|   |     |       | 2.2.3.1      | Simulation Procedure                            | 69  |

|   |     |       | 2.2.3.2      | Simulation Results                              | 70  |

|   | 2.3 | Summ  | nary         |                                                 | 78  |

| 3 | VAR | IABLE | FREQUE       | NCY CONTROL SCHEME                              | 80  |

|   | 3.1 | The V | ariable Cur  | rrent Hysteresis Control Scheme for PFC Circuit | 81  |

|   | 3.2 | Mode  | lling and A  | nalysis of the PFC circuit under VCHC Control   | 82  |

|   |     | 3.2.1 | The ON S     | State                                           | 83  |

|   |     | 3.2.2 | The OFF      | State                                           | 85  |

|   | 3.3 | Desig | n Example    |                                                 | 87  |

|   | 3.4 | Simul | ation of the | PFC Circuit for the Variable Current            |     |

|   |     | Hyste | resis Contro | bl                                              | 89  |

|   |     | 3.4.1 | Simulatio    | n Procedure.                                    | 90  |

|   |     | 3.4.2 | Simulatio    | n Results                                       | 91  |

|   | 3.5 | Summ  | nary         |                                                 | 101 |

|   |     |       |              |                                                 |     |

| 1 | ZER | O-CUR | RENT ZEI     | RO-VOLTAGE SWITCHING SCHEME                     | 102 |

|   | 4.1 | The Z | ero-Current  | , Zero-Voltage Control Scheme                   | 103 |

|   | 4.2 | Model | lling and Ar | nalysis of the PFC Circuit under                |     |

|   |     | ZCS-Z | VS Contro    | I                                               | 104 |

|   |     | 4.2.1 | ON State     | of $S_1$ and $S_2$                              | 104 |

|   |      | 4.2.2 OFF State of $S_1$ and $S_2$               | 107     |

|---|------|--------------------------------------------------|---------|

|   | 4.3  | Design Example                                   | 112     |

|   | 4.4  | Simulation of the PFC Circuit for ZCS-ZVS Scheme | e 113   |

|   |      | 4.4.1 Simulation Procedure                       | 114     |

|   |      | 4.4.2 Simulation Results                         | 115     |

|   | 4.5  | Summary                                          | 125     |

| 5 | COM  | MPARATIVE STUDY OF THE CONTROL SCHE              | MES 126 |

|   | 5.1  | Comparative Study                                | 126     |

| 6 | CON  | CLUSIONS                                         | 135     |

|   | 6.1  | Suggestions for future work                      | 138     |

|   | REF  | ERENCES                                          | 140     |

|   | APPI | ENDIX – A                                        | 144     |

# List of Figures

| 1.1    | Single-Phase AC-DC Converter Circuit with Input Low Pass Filter        | 1   |

|--------|------------------------------------------------------------------------|-----|

| 1.2    | Current Injection Method in Three-Phase AC-DC Converter                | 8   |

| 1.3    | Block Diagram of Adaptive Phase Control Method                         | 12  |

| 1.4    | Block Diagram of PCFF Control Scheme                                   | 14  |

| 1.5    | The Single-Phase PFC Circuit                                           | 16  |

| 1.6(a) | Equivalent Circuit (ON State)                                          | 17  |

| 1.6(b) | Equivalent Circuit (OFF State)                                         | 17  |

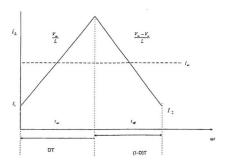

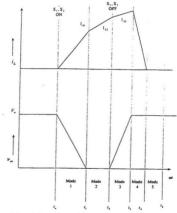

| 1.7    | Ideal Operating Waveform of Boost Converter                            | 18  |

| 2.1    | Control Circuit of the CFCC Scheme                                     | 24  |

| 2.2    | ON State Equivalent Circuit                                            | 26  |

| 2.3    | OFF State Equivalent Circuit                                           | 31  |

| 2.4    | Theoretical Input Current Waveform of the CFCC Control Scheme          | 33  |

| 2.5    | The Error Amplifier used in the Voltage Feedback Loop                  | 35  |

| 2.6    | Inductor Current Waveform in the Continuous Mode of Operation          | 37  |

| 2.7    | Boost Switch Waveforms and Instantaneous Boost Switch Power Loss       | 44  |

| 2.8    | Flow Chart of the CFCC Control Scheme showing the Simulation Procedure | 48  |

| 2.9    | Per-Unit Source Current and Source Voltage Waveforms ( $L = 1.5 mH$ ,  | C = |

|        | 470 uF F = 100kHz)                                                     | 40  |

| 2.10    | Per-Unit Source Current and Source Voltage Waveforms ( L = 5.5mH, C                   | =   |

|---------|---------------------------------------------------------------------------------------|-----|

|         | $1000  \mu F$ , $F_s = 5 \text{kHz}$ )                                                | 50  |

| 2.11    | Per Unit Source Current and Source Voltage Waveforms ( L = 5mH, C = 470 $\mu$         | F   |

|         | $F_s = 100 \text{kHz}$                                                                | 51  |

| 2.12    | Per Unit Source Current and Source Voltage Waveforms ( L = 10mH, C                    | =   |

|         | $1000  \mu F \cdot F_r = 5 \text{kHz}$                                                | 52  |

| 2.13    | Per-Unit Output Voltage Waveform ( L = 1.5mH, C = 470 $\mu$ F, $F_r$ = 100kHz)        | 53  |

| 2.14    | THD of the Source Current versus varying Boost Inductor ( $C = 470 \mu$ c             | F   |

|         | F,=100kHz)                                                                            | 54  |

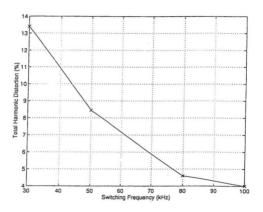

| 2.15    | THD of the Source Current versus varying Switching Frequency ( $L = 1.5 \text{ mH}$ , | C   |

|         | = 470 µF)                                                                             | 55  |

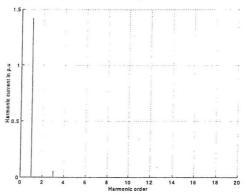

| 2.16    | Per-Unit Harmonic Component of the Source Current versus Harmonic ord                 | iei |

| 9       | ( L = 1.5mH, C = $470 \mu F$ , $F_{\tau} = 100 \text{kHz}$ )                          | 56  |

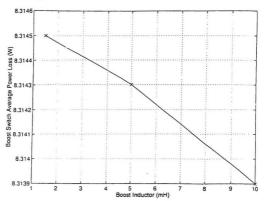

| 2.17    | Power Loss across the Boost Switch versus varying Boost Inductor ( $C = 470 \mu F$    |     |

|         | F,=100kHz)                                                                            | 57  |

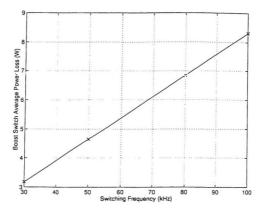

| 2.18    | Power Loss across the Boost Switch versus varying Switching Frequency (L              | =   |

|         | 1.5mH, $C = 470 \mu\text{F}$ )                                                        | 58  |

| 2.19    | Control Circuit of the CFDC Control Scheme                                            | 60  |

| 2.20(a) | Equivalent Circuit during the ON State                                                | 52  |

| 2.20(b) | Equivalent Circuit showing $\nu_{\epsilon}$ during the OFF State                      | 54  |

| 2.21 | Theoretical Input Current Waveform of the CFDC Control Scheme                      | 66   |

|------|------------------------------------------------------------------------------------|------|

| 2.22 | Flow Chart of the CFDC Control Scheme showing the Simulation Procedure             | 69   |

| 2.23 | Per-unit Source Current and Source Voltage Waveforms ( $L = 0.1 mH$ ,              | C =  |

|      | $470  \mu F$ , $F_s = 100 \text{kHz}$ )                                            | 70   |

| 2.24 | Per-Unit Source Current and Source Voltage Waveforms ( $L$ = 2.2mH,                | C =  |

|      | $1000  \mu F$ , $F_s = 5 \text{kHz}$ )                                             | 71   |

| 2.25 | Per-Unit Output Voltage Waveform ( L = 0.1mH, C = 470 $\mu$ F , $F_s$ = 100kHz)    | 72   |

| 2.26 | THD of the Input Current versus varying Boost Inductor (C = 470 $\mu F$ ,          | F, = |

|      | 100kHz)                                                                            | 73   |

| 2.27 | THD of the Input Current versus varying Switching Frequency (L = $0.1 \text{mH}$ , | C =  |

|      | 470 μF )                                                                           | 74   |

| 2.28 | Per-Unit Harmonic Component of the Input Current versus Harmonic order             | L =  |

|      | 0.1mH, C = 470 $\mu F$ , $F_s = 100 \mathrm{kHz}$ )                                | 75   |

| 2.29 | Power Loss across the Boost Switch versus varying Boost Inductor (                 | C =  |

|      | 470 μF , F <sub>z</sub> = 100kHz)                                                  | 76   |

| 2.30 | Power Loss across the Boost Switch versus varying Switching Frequency              | (L = |

|      | $0.1 \mathrm{mH}, \mathrm{C} = 470 \mu\mathrm{F}$ )                                | 77   |

| 3.1  | Control circuit of the VCHC Scheme                                                 | 82   |

| 3.2  | ON State Equivalent Circuit                                                        | 83   |

| 3.3  | OFF State Equivalent Circuit                                                       | 85   |

| 3.4  | Theoretical Input Current Waveform of the VCHC Control Scheme                      | 86   |

3.5 Flow Chart of the VCHC Control Scheme showing the Simulation Procedure 90

36

- Per-Unit Source Current and Source Voltage waveforms (L = 1.5mH, C =  $470 \, \mu F \cdot \delta = 1.4 A)$ 91

- Per-Unit Source Current and Source Voltage Waveforms (L = 5.5mH, C = 3.7  $1000 \,\mu\text{F}$ ,  $\delta = 3\text{A}$ ) 92

- 3.8 Per-Unit Output Voltage Waveform (L = 1.5mH, C = 470  $\mu$ F,  $\delta$  = 1.4A) 93

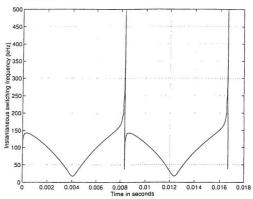

- 3.9 Instantaneous Switching Frequency over one Cycle of Operation (L = 1.5mH, C =  $470 \, \mu F \, \delta = 1.4 \, A)$ 94

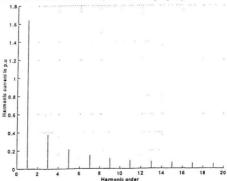

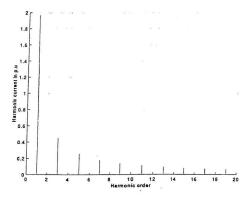

- 3.10 Per-Unit Harmonic Component of the Input Current versus Harmonic order (L =  $1.5 \text{mH. C} = 470 \,\mu\text{F}$ .  $\delta = 1.4 \text{A}$ 95

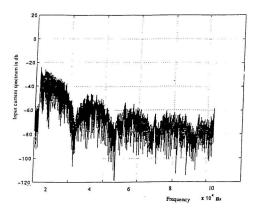

- 3.11 Frequency Spectrum of the Input Current (L = 1.5mH, C = 470  $\mu$ F,  $\delta$  = 1.4A) 96

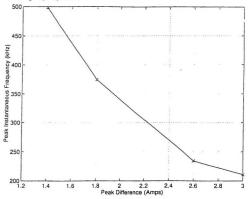

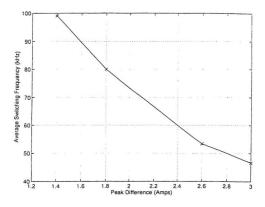

- 3.12 Peak Instantaneous Switching Frequency of the Boost Switch versus  $\delta$  (L =  $1.5 \text{mH}, C = 470 \,\mu\text{F}$ 97

- 3.13 Average Switching Frequency of the Boost Switch versus  $\delta$  (L = 1.5mH, C = 470 µF) 98

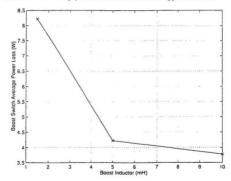

- Power Loss across the Boost Switch versus varying Boost Inductor ( $C = 470 \,\mu F$ ).  $\delta = 1.4A$ 99

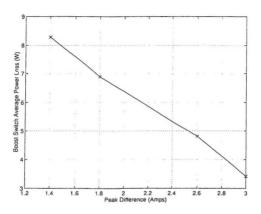

- Power Loss across the Boost Switch versus varying Peak Difference (L = 1.5mH.  $C = 470 \, \mu F$ ) 100

- 4.1 Power Factor Correction Circuit with Zero Voltage Switching Scheme 103

- 4.2 Equivalent Circuits of the ZCS-ZVS PFC Circuit ON State (Mode 1 and 2) 105

| 4.3  | Equivalent Circuits of the ZCS-ZVS PFC Circuit OFF State (Mode 3, 4 $\&$ 5)      | 108    |

|------|----------------------------------------------------------------------------------|--------|

| 4.4  | Theoretical Waveforms of Input Current and Voltage across Commu                  | tating |

|      | Capacitor of ZCS-ZVS Control Scheme                                              | 111    |

| 4.5  | Flow Chart of the ZCS-ZVS Control Scheme showing the Simulation                  | ation  |

|      | Procedure                                                                        | 114    |

| 4.6  | Per-Unit Source Current and Source Voltage Waveforms ( $L = 0.1 mH$ .            | C =    |

|      | $470 \mu F$ , $C_r = 0.001 \mu F$ , $F_z = 100 \text{kHz}$ )                     | 115    |

| 4.7  | Per-Unit Source Current and Source Voltage Waveforms ( $L = 2.2 mH$ ,            | C =    |

|      | $1000  \mu F$ , $C_r = 0.001  \mu F$ , $F_s = 5 \mathrm{kHz}$ )                  | 116    |

| 4.8  | Per-Unit Voltage across the Boost Switch and Input Current Waveforms             | L=     |

|      | 0.1 mH, C = 470 $\mu F$ , $C_r$ = 0.001 $\mu F$ , $F_r$ = 100kHz)                | 117    |

| 4.9  | Frequency Spectrum of the Input Current ( L = 0.1mH, C = $470\mu F$ ,            | C,=    |

|      | $0.001  \mu F$ , $F_s = 100  \text{kHz}$ )                                       | 118    |

| 4.10 | Per-Unit Harmonic Component of the Input Current versus Harmonic order           | ( L =  |

|      | 0.1mH, C = 470 $\mu$ F, $C_s$ = 0.001 $\mu$ F, $F_s$ = 100kHz)                   | 119    |

| 4.11 | THD of the Input Current versus Boost Inductor value (C = 470 $\mu F$            | , C,=  |

|      | 0.001 $\mu F$ , $F_s = 100 \mathrm{kHz}$ )                                       | 120    |

| 4.12 | THD of the Input Current versus varying Switching Frequency (L = $0.1 \text{mH}$ | , C,=  |

|      | $0.001 \mu F$ , $C = 470 \mu F$ )                                                | 121    |

| 4.13 | Power Loss across the Boost Switch versus varying Boost Inductor ( $C = 470 \mu$ | υF,    |

|      | $C_r = 0.001  \mu F$ , $F_s = 100 \text{kHz}$ )                                  | 122    |

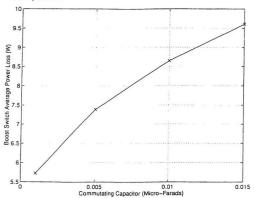

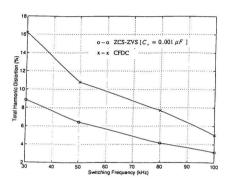

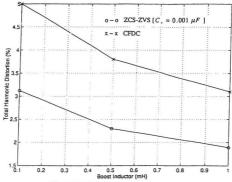

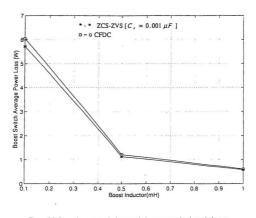

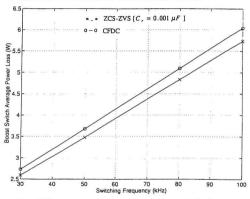

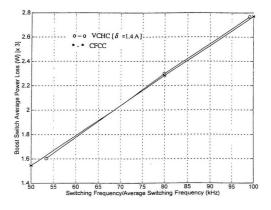

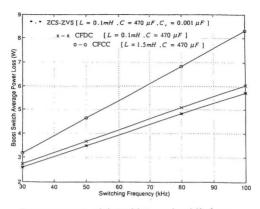

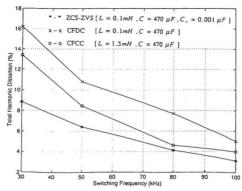

Power Loss across the Boost Switch versus varying Switching Frequency (L = 4.14  $0.1 \text{mH}, C = 470 \,\mu\text{F}, C = 0.001 \,\mu\text{F}$ 123 4.15 Power Loss across the Boost Switch versus varying Commutating Capacitor (L = 0.1 mH,  $C = 470 \,\mu\text{F}$ ,  $F_{e} = 100 \text{kHz}$ ) 124 5.1 THD versus varying Switching Frequency (L = 0.1 mH, C = 470 uF) 127 THD versus varying Boost Inductor value (C = 470  $\mu$ F, F, = 100kHz) 5.2 128 5.3 Power Loss across the Boost Switch versus varying Boost Inductor (C =  $470 \, \mu F$  ,  $F_r = 100 \text{kHz}$ ) 129 5.4 Power Loss across the Boost Switch versus varying Switching Frequency (L =  $0.1 \text{mH}, C = 470 \,\mu\text{F}$ ) 130 5.5 Power Loss across the Boost Switch versus varying Switching Frequency (L =  $1.5 \text{mH}, C = 470 \,\mu\text{F}$ ) 132 5.6 Power Loss across the Boost Switch versus varying Switching Frequency (V = 240V (rms),  $V_a = 380V(dc)$ ,  $P_a = 400W$ ) THD versus varying Switching Frequency ( $V_c = 240 \text{V} \text{ (rms)}, V_a = 380 \text{V(dc)}, P_a$ 5.7

134

=400W)

# List of Tables

| .1 | Typical Harmonics in a Single-Phase Input Current with no Line Filtering | 4   |

|----|--------------------------------------------------------------------------|-----|

| .2 | Permitted Harmonic Currents for any Consumer at PCC                      | 4   |

| .3 | Harmonic Voltage Distortion Limits at any Point on the Utility System    | 5   |

| .1 | Qualitative comparison of CFCC, CFDC, VCHC&ZVS-ZCS Control               |     |

|    | Schemes                                                                  | 13- |

# Chapter 1

### INTRODUCTION

Power electronics is gaining widespread popularity and is playing a key role in several residential, commercial and industrial applications. Almost invariably in such systems like television, radio receivers, light dimmers, AC-motor drives, DC-servo drives, uninterruptible power supplies (UPS), magnet power supplies and high power induction heating equipment, the 60 Hz input voltage is first rectified into a DC voltage. The DC voltage is subsequently converted into the voltages and currents of appropriate magnitude, frequency and phase to meet the load requirements. In all cases, the source voltage is obtained from the utility supply.

Electric utility supply quality issues, including harmonics and quasi static waveform excursions are now top priority issues for equipment manufacturers, users and electric utility personnel. Harmonics, super and sub-harmonics, and interharmonics, can cause system equipment malfunctioning, increased losses in the utility lines, increased distortion of the supply voltage, interference with other electrical equipment, personnel safety problems, over-burdened neutral wires, ground potential rise, light flickering, computer data loss and memory malfunctioning, erratic process control and other associated problems. The most serious problem associated with harmonics is the loss of efficient energy utilization due to lower distortion power factor.

The DC output voltage of an AC-DC converter should be as ripple-free as possible. For this reason, a large capacitor is connected as a filter on the DC side. Since this capacitor is charged to a value close to the peak AC magnitude the rectifier then draws a highly distorted current from the utility which leads to current harmonic generation.

One approach to minimize this impact is to filter the harmonic currents and the electromagnetic interference (EMI) produced by the power electronic loads. A better alternative, in spite of a small increase in the initial cost, may be to design the power electronic equipment such that the harmonic current generation and the EMI are prevented or minimized in the first place. With the potential for proliferation of power electronics equipment and enforcement of harmonic standards such as IEEE 519, IEC 555, there is an increasing need for active current waveshaping through appropriate control schemes.

# 1.1 HARMONIC STANDARDS AND RECOMMENDED PRACTICES

In view of the proliferation of power electronic equipment connected to the utility system, many national and international agencies have been considering limits on harmonic current injection to maintain good power quality. Various standards and guidelines have been established that specify limits on the magnitudes of harmonic currents and total harmonic distortion (THD). Some of these are:

- 1) EN 50 006, "The Limitation of Disturbances in Electric Supply Networks caused by Domestic and Similar Appliances Equipped with Electronic Devices", European Standard prepared by Comit é Européen de Normalisation Electrotechnique, CENELEC.

- 2) IEC Norm 555-3, prepared by the International Electrical Commission.

- West German Standards VDE 0838 for household appliances, VDE 0160 for converters and VDE 0712 for fluorescent lamp ballasts.

- IEEE Guide for Harmonic Control and Reactive Compensation of Static Power Converters, ANSI/IEEE Std. 519-1981.

Some of the standards of harmonic current and voltage are shown in Table 1.1 to Table 1.3 [2.3]. Table 1.1 shows typical harmonics in a single phase input current waveform with no line filtering. The harmonic currents  $(I_4)$  are expressed as the ratio of the fundamental current  $(I_1)$ . From Table 1.1 it can be seen that without the use of input

filter, the input current waveform consists of large harmonic magnitudes.

Table 1.1: Typical Harmonics in a single-phase input current with no line filtering

| h                                | 3    | 5    | 7   | 9   | 11  | 13  | 15  | 17  |

|----------------------------------|------|------|-----|-----|-----|-----|-----|-----|

| $\left(\frac{I_k}{I_1}\right)\%$ | 73.2 | 36.6 | 8.1 | 5.7 | 4.1 | 2.9 | 0.8 | 0.4 |

Table 1.2 shows the permitted harmonic currents for any consumer at the point of common coupling (PCC). A tolerance of + 10% or 0.5A (whichever is the greater) is permissible, provided it applies to no more than two harmonics. Table 1.3 shows the harmonic voltage distortion at any point on the utility system.

Table 1. 2: Permitted harmonic currents for any consumer at PCC

| Utility input voltage<br>at PCC ( kV ) | На | rmor | nic n | umb | er a | nd c | urre | ent p | er pl | hase | at PC | C ( A | rms | . ) |

|----------------------------------------|----|------|-------|-----|------|------|------|-------|-------|------|-------|-------|-----|-----|

|                                        | 2  | 3    | 4     | 5   | 6    | 7    | 8    | 9     | 10    | 11   | 12    | 13    | 14  | 15  |

| 0.415                                  | 48 | 34   | 22    | 56  | 11   | 40   | 9    | 8     | 7     | 19   | 6     | 16    | 5   | 5   |

| 6.6 and 11                             | 13 | 8    | 5     | 10  | 4    | 8    | 3    | 3     | 3     | 7    | 2     | 6     | 2   | 2   |

| 33                                     | 11 | 7    | 5     | 9   | 4    | 6    | 3    | 2     | 2     | 6    | 2     | 5     | 2   | 1   |

| 132                                    | 5  | 4    | 3     | 4   | 2    | 3    | I    | 1     | 1     | 3    | 1     | 3     | 1   | 1   |

Table 1.3: Harmonic voltage distortion limits at any point on the utility system

| Total Harmonic voltage | Individual harmonic voltag |                                      |  |  |  |

|------------------------|----------------------------|--------------------------------------|--|--|--|

| Distortion (%)         | Distortion (%)             |                                      |  |  |  |

|                        | Odd                        | Even                                 |  |  |  |

| 5                      | 4                          | 2                                    |  |  |  |

| 4                      | 3                          | 1.75                                 |  |  |  |

| 3                      | 2                          | ı                                    |  |  |  |

| 1.5                    | 1                          | 0.5                                  |  |  |  |

|                        | Distortion (%)  5  4  3    | Distortion (%) Dis  Odd  5 4 4 3 3 2 |  |  |  |

In order to meet the various harmonic standards several techniques have been proposed to minimize the harmonics in the AC-DC converter. In general, there are three approaches that can be used to shape the line current. The first approach uses energy storage and magnetic components to minimize the harmonics. This approach is referred to as the passive technique. The second approach, known as current injection technique, attempts to reduce or minimize the current harmonics by injecting a third harmonic current into the input. The third approach, referred to as the active technique, employs switching techniques to shape the current waveform. The subsequent section explains the details and principles of the different techniques.

# 1.2 HARMONIC MINIMIZATION USING PASSIVE TECHNIQUES

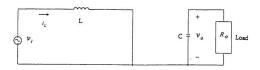

This technique uses mainly passive devices, capacitors and inductors to minimize the current harmonics. A single phase implementation of the Power Factor Correction (PFC) circuit employs a low pass filter method.

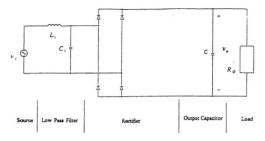

Using a low pass filter at the input side for harmonic minimization is one of the basic passive control methods. As the harmonic component of the input current has frequencies which are multiples of the base frequency, most of the high frequency harmonics can be eliminated or reduced using a low pass filter. The cut off frequency of the low pass filter can be designed so that any frequency above the designed cut off frequency will be attenuated. The result is a reduction in the harmonics fed back into the utility supply. The exact design of the cut off frequency of a low pass filter is the major disadvantage of this scheme. To attenuate the designed higher frequencies, the cut off frequency should remain constant throughout the operation of AC-DC converter. Moreover, the ideal low pass frequency response, i.e. sharp passband and stop band, is hard to implement in any practical circuit. Figure 1.1 shows a single-phase AC-DC rectifier with an input low pass filter network.

Figure 1.1: Single-phase AC-DC converter circuit with an input low-pass filter

### 1.3 CURRENT INJECTION METHOD

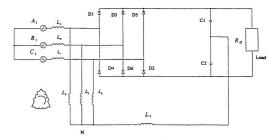

Figure 1.2 shows one type of the current injection method in a three-phase AC-DC converter system. This approach involves an interconnection of a three-phase limb core star/delta transformer between the AC and DC sides of the diode rectifier topology. The capacitors on the DC side provide the mid-point for the DC output voltage. The secondary of the transformer is connected in delta and is unloaded. It has been shown that due to the 120 degree conduction intervals of each diode, the voltage drop between the transformer neutral and the output capacitor midpoint is essentially a third harmonic component [4, 5]. The resultant third harmonic current circulates between the AC and DC side of the rectifier bridge. Recently, variations of the basic current injection method have

been proposed [6]. It has been shown that the third harmonic current drastically reduces the input current harmonics and improves the input power factor.

Figure 1.2: Current injection method in three-phase AC-DC converter

The main advantages of this method are as follows.

- The scheme is passive and does not interfere with the AC-DC rectification process of the diode rectifier topology.

- The transformer draws negligible fundamental current from the input source (equal to the excitation current) since the delta connected secondary is unloaded.

- The circulating third harmonic current is automatically generated by the midpoint arrangement of the output capacitors.

- The delta connected secondary permits a path for zero sequence third harmonic currents to circulate, thereby automatically balancing the flux in the transformer core.

The passive harmonic elimination/minimization approach require bulky, expensive filters or magnetic components at the input side of the AC-DC converters. For most residential, commercial applications and some industrial applications, the current injection method is too expensive. Hence, different control schemes are being developed for both three-phase and single-phase rectifier systems, which eliminate the usage of any expensive devices but still maintain the nearly unity input power factor with minimum allowable input current harmonics.

### 1.4 HARMONIC MINIMIZATION USING ACTIVE TECHNIQUES

Harmonic minimization using active techniques can be classified into two categories, namely, Pulse Width Modulation switching of the converter devices and Pulse Width Modulation switching of auxiliary devices.

### 1.4.1 PULSE WIDTH MODULATION SWITCHING OF THE CONVERTER DEVICES

Pulse Width Modulation (PWM) technique is widely used in AC-DC converters to minimize the input current harmonics. In this scheme, the ON/OFF time of the rectifier switches, are controlled by the width of the PWM pulses. The PWM pulses are generated by comparing a carrier waveform with a modulating waveform. Many different methods of obtaining the modulating signal have been proposed in the literature [7-17].

The advantage of PWM schemes is that the size of the overall system is small. However, the major limitation of PWM schemes is that it requires a complex synchronization logic circuit. This is because the switches in the rectifier network are required to switch ON/OFF in synchronism with the supply voltage. The dominant PWM fixed switching frequency techniques are the Adaptive Phase Control (APC) technique and the Predicted Current Control with Fixed Frequency (PCFF) technique.

#### 1411 ADAPTIVE PHASE CONTROL

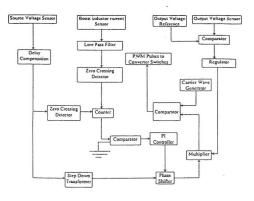

The adaptive phase control (APC) scheme is one of the traditional fixed switching frequency PWM methods used to improve the input power factor and minimize the total harmonic distortion for three-phase AC-DC converters. A block diagram of the control scheme is shown in fig 1.3. In this scheme, the phase of the line current with respect to the phase voltage is continuously detected and used as a control input to generate the necessary PWM switching patterns. Because of its adaptability, the control logic is independent of any circuit parameter. In general the PWM controller generates the switching pattern of the six switches in the three-phase rectifier by comparing the threephase modulating voltages and a carrier triangular wave. The frequency of the triangular wave determines the switching frequency of the rectifier switches. The scheme uses separate regulation loops for phase regulation and amplitude regulation of the line current. By using proper modulation technique for the switching pattern of the switches. PWM AC-DC converters have been demonstrated to have attractive features in terms of reduced line harmonics distortion, nearly unity power factor, small filter components on both the ac and dc side of the converter [18 19].

The drawback of the APC scheme is its complex synchronization logic. Zerocrossing detectors which are used in this scheme to detect the zero crossings of the phase voltage and the fundamental component of the line current become difficult to measure for high frequency applications.

Figure 1.3: Block diagram of Adaptive Phase Control method [18]

### 1412 PREDICTED CURRENT CONTROL

The predicted current control with fixed switching frequency (PCFF) is another PWM method used to improve the input power factor and minimize the total harmonic distortion for three-phase AC-DC converters. Figure 1.4 shows the block diagram of a PCFF control scheme. In this technique, the modulating voltage required to control the line current is calculated based on the parameters of the power circuit and the switching frequency. This voltage is then compared to a carrier wave to generate quasi-optimal switching pattern to regulate the line current [20]. This scheme is favourable for high power applications because of its well-defined switching pattern which results in predictable stress on the switching devices.

However, the major shortcoming of the PCFF control scheme is that its control principle is parameter dependent. Exact knowledge of the power circuit parameters is required to implement the control logic. In practice, however, these parameters vary due to variation in temperature, nonlinearity and saturation of the magnetic core. Parasitic components, such as equivalent series resistance associated with output capacitor, contribute to the circuit considerably when the switching frequency is high. These variations are unpredictable and hence difficult to compensate.

Figure 1.4: Block diagram of PCFF control scheme [19]

# 1.4.2 PULSE WIDTH MODULATION SWITCHING OF AUXILIARY DEVICES

In this scheme, the PWM pulses are applied to auxiliary devices usually connected at the output side of the rectifier circuit. The auxiliary switches are pulse-width modulated according to a control algorithm so as to achieve harmonic reduction in the input current waveform. The advantage of this scheme is that no complex synchronization logic circuit is required.

### 1.4.2.1 ACTIVE POWER FACTOR CORRECTION CIRCUIT

With the maturing of static power converter technology and the remarkable progress in the development of power semiconductor devices, several converter topologies for active power factor correction circuits have been successfully implemented [21,23,24].

The choice of the power electronic converter is based on the following

- In general, the electrical isolation between the utility input and the output of the

power electronic system is either not needed (like in AC and DC-motor drives), or it

can be provided in the second converter stage as in switch-mode DC power

supplies

- In most applications it is acceptable and in many cases it is desirable to regulate the DC output voltage.

- The input current drawn should ideally be at a unity power factor so that the power

electronic interface emulates a resistor supplied by the utility source. This also

implies that the power flow should be always unidirectional, from the utility source to

the power electronic equipment.

- The cost, power losses and size of the current shaping circuit should be as small as possible.

Among the converter topologies published [21,23,24], the most popular schemes employ the boost converter concept to shape the input current so as to improve the input power factor to near unity. This is because in the boost converter topology, the auxiliary switch is now controlled alone and controlled switches are not required in the rectifier circuit.

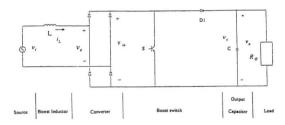

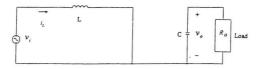

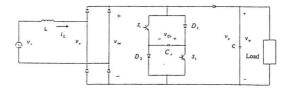

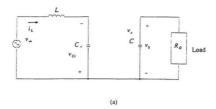

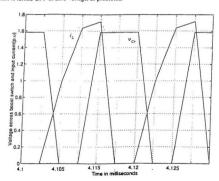

The prevalent single-phase active power factor correction (PFC) circuit is shown in fig 1.5. It consists of a boost inductor, standard diode bridge rectifier followed by a switch and an output capacitor. Figures 1.6(a) and 1.6(b) show the topological changes of the boost converter during ON and OFF conditions of the switch respectively. The ON and OFF times of the boost switch (S) are controlled by the PWM signal generated from the various current control schemes.

Figure 1.5: The single-phase PFC circuit

Figure 1.6(a): Equivalent circuit - ON state

Figure 1.6(b): Equivalent circuit - OFF state

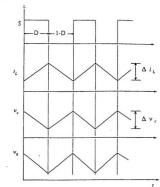

During the ON state the boost switch (S) provides a short circuit path through the AC source, the pair of diagonal diodes and the inductor (L). Consequently, the current in the inductor increases at a rate proportional to the instantaneous value of the input voltage. The output capacitor (C) meanwhile discharges through the load and provides the regulated power to it. During the OFF state the current in the boost inductor decreases since the output voltage is much higher than the instantaneous input voltage. At the end of this stage the output capacitor (C) is charged to its maximum value. The ideal operating waveforms of the converter are shown in fig 1.7.

Figure 1.7: Ideal operating waveform of boost converter

# 1.4.2.2 CONTROL SCHEMES FOR THE SINGLE PHASE AC-DC CONVERTER

It has been shown that the current-mode controllers are superior to the PWM duty-ratio controllers used for APC and PCFF techniques [22]. The major advantages of the current-mode controllers are:

- Essentially no phase lag from the control to inductor current, practically eliminating the possibility of low-frequency oscillation of the closed loop

- Inherent pulse-by-pulse current limiting, making the power converter nearly immune to damage from overloads

- Ease of paralleling power stages, to provide increased output-current capability, with equal current-sharing among the paralleled stages

- Ease of applying output-current feedforward, to obtain super-fast correction for load transients and minimization of the deviations of output voltage

- Inherent insensitivity to static and dynamic variations of input voltage

Current control schemes can be classified broadly into three groups, namely

- a) Constant Frequency Control Schemes

- b) Variable Frequency Control Schemes

- c) Zero-current, Zero-voltage Switching Control Schemes

#### 1.5 THESIS OBJECTIVES

The various current control schemes for achieving nearly unity power factor and to minimize the total harmonic distortion (THD) of the input current have been proposed and their feasibility have been demonstrated [25-34]. However, to the best of the author's knowledge, a comparative study of their features is lacking in the literature. The objective of this thesis is, therefore, to examine and compare the performance characteristics of the various current control methods for power factor correction. The performance characteristics are obtained through the modelling and simulation of the different methods for the same circuit conditions.

#### 1.6 THESIS OUTLINE

Chapter 2 focuses on the description, mathematical models and analysis of the different types of constant frequency current control methods. Operational and performance characteristics, namely total harmonic distortion, frequency spectrum and power losses have been presented for two values of switching frequency. MATLAB [36] has been used to simulate the system equations. The advantages and disadvantages of the different types of constant frequency control schemes are highlighted in the chapter.

Chapter 3 discusses the description, mathematical models and analysis of the variable frequency current control scheme and the performance for the same circuit conditions. Computer simulations of the control scheme are also provided to show the various characteristics of the scheme. The advantages and disadvantages are also discussed

Chapter 4 is devoted to the modelling, analysis and simulation of a zero currentzero voltage switching (ZCS-ZVS) scheme. Simulation results have been provided to show the operational features of the control scheme. The different performance characteristics such as total harmonic distortion, frequency spectrum and power loss are presented.

Finally, in Chapter 5, a summary of the thesis highlighting the contribution of the research and suggestions for further work is outlined.

## Chapter 2

## CONSTANT FREQUENCY CONTROL SCHEMES

## INTRODUCTION

The most important feature of constant frequency control schemes is that the frequency of operation of the boost switch (S) remains constant throughout the cycle of operation. Constant frequency is desirable since it allows for the easy design of an input filter and the total harmonic distortion can be readily predicted. This chapter focuses on the description, modelling, analysis and simulation of constant frequency control schemes used in AC-DC converter systems. The modelling and analysis has been done using equivalent circuit representation of the various states of the boost switch. The analytical expressions corresponding to the equivalent circuits that describe the boost inductor current and output voltage in steady state operation are then formulated. These equations are then simulated using MATLAB to obtain the performance characteristics of the different constant frequency control methods.

Among the many control methods, the most popular constant frequency control methods which are described in this chapter are

- a) Constant Frequency Continuous Current Control (CFCC)

- b) Constant Frequency Discontinuous Current Control (CFDC)

# 2.1 CONSTANT FREQUENCY CONTINUOUS CURRENT CONTROL SCHEME

This control scheme gives a continuous non-zero boost inductor current at a fixed switching frequency. Through the action of the control scheme, the inductor current is constrained to follow the rectified waveshape of the input voltage, resulting in a nearly sinusoidal input current waveform.

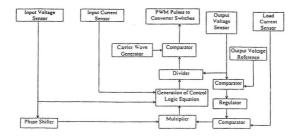

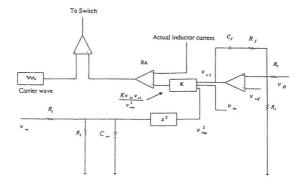

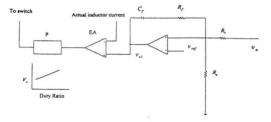

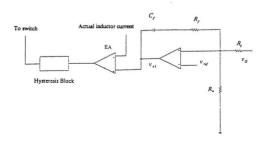

In order to achieve a nearly unity power factor at the input and a constant DC output voltage, the two important circuit variables which are to be controlled are the boost inductor current and the output voltage. These variables can be used in a feedback control circuit which in turn will control the duty cycle of the boost switch. Figure 2.1 shows the control circuit diagram of the constant frequency continuous current (CFCC) control scheme [26]. The scheme uses the average value of the inductor current as an inner loop control variable to determine the ON/OFF switching of the boost switch (S). A signal proportional to the actual instantaneous inductor current is compared with a signal from the block K through the comparator (EA). The prime importance of the block K is to establish the desired average inductor current.

Figure 2.1: Control circuit of the CFCC scheme [26]

An outer voltage feedback loop, comprising the filtered output voltage  $(v_n)$ , the rectified input voltage  $(v_m)$  and the square of the feedforward signal  $(v_{nn})$ , provides the regulation of the output voltage.

The average current is directly proportional to the rectified input voltage, error amplifier output voltage ( $\nu_{el}$ ) and inversely proportional to the square of the feedforward voltage. From fig 2.1 the desired average inductor current  $i_{er}$  is obtained as

$$i_{av} = \frac{Kv_{av}v_{el}}{v_{ing}^2}$$

(2.1)

where

v, is the instantaneous voltage of the rectified sine wave from the line

v, is the instantaneous output voltage of the error amplifier

v<sub>m</sub> is a signal proportional to the rms value of the line voltage which is introduced to normalize the rectified sine wave and provide feedforward.

K is the multiplying factor to achieve a desired average inductor current

For one switching interval the input voltage, error amplifier voltage and the feedforward voltage are assumed to be constant and equation 2.1 can be written as

$$I_{uv} = \frac{KV_{uv}V_{el}}{V_{uv}^2}$$

(2.2)

The output of the comparator EA is compared with a fixed frequency triangular waveform to produce a PWM signal for the ON/OF control of the boost switch. The error amplifier (EA) is designed with a very slow frequency response. This prevents the error signal from following the ripple changes in the output voltage.

### 2.1.1 MODELLING AND ANALYSIS OF THE POWER CIRCUIT

This section presents the modelling and analysis of the power factor correction circuit taking into account the effect of the control scheme. The converter operates in two distinct states, namely the ON and OFF states.

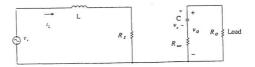

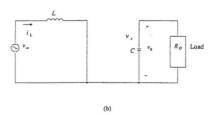

#### 2.1.1.1 THE ON STATE

The equivalent circuit for the ON state of the boost switch is shown in fig 2.2. The model includes the series resistance ( $R_{ij}$ ) associated with the boost inductor, and the equivalent series resistance ( $R_{ij}$ ) of the output capacitor.

Figure 2.2: ON state equivalent circuit

The following equations can be derived from the equivalent circuit.

$$L\frac{di_{L}}{dt} = v_{i} - i_{L}R_{s} \qquad (2.3)$$

$$C\frac{dv_c}{dt} = -\frac{v_c}{R + R_0}$$

(2.4)

where

i, is the instantaneous inductor current

v, is the instantaneous supply voltage

v, is the instantaneous capacitor voltage

R<sub>ev</sub> is the series resistance associated with the output capacitor C

R is the series resistance associated with the boost inductor L

Ro is the load resistance

For a small time increment  $\Delta t$ , the inductor current  $i_L$ , capacitor voltage  $v_e$  and the supply voltage,  $v_e$  may be assumed constant and may be represented as  $I_L$ ,  $V_e$  and  $V_e$  respectively. Over the time interval  $\Delta t$ , equations 2.3 and 2.4 may be written as

$$L\frac{\Delta i_L}{\Delta I} = V_i - R_r I_L \qquad (2.5)$$

$$C\frac{\Delta v_c}{\Delta t} = -\frac{V_c}{R_{er} + R_o} \tag{2.6}$$

Equations (2.5) and (2.6) can be used to calculate the state variables  $\Delta i_{\epsilon}$  and  $\Delta \nu_{\epsilon}$  at the end of the time interval  $\Delta t$ . The values obtained at the end of the time interval can be used as the initial values of the next interval. This procedure, repeated for subsequent

intervals gives continuous values of  $i_L$  and  $v_e$  during the ON state of the switch. This method is only accurate if the time interval is small.

In equation (2.5) and (2.6), the inductor current  $I_L$  and capacitor voltage  $V_e$  are approximated as the average of the values at the start  $(i_L, v_\alpha)$  and end  $(i_L, v_\alpha)$  of the time interval  $N_L$  and are expressed as

$$I_L = 0.5(i_{Lr} + i_{Lr})$$

(2.7)

$$V_e = 0.5(v_c + v_{ee}) \qquad (2.8)$$

$$\Delta i_L = i_{Le} - i_{Le} \qquad (2.9)$$

$$\Delta v_c = v_{cs} - v_{cs} \qquad (2.10)$$

Substituting these values into equations (2.5) and (2.6) gives

$$i_{Lr} = \frac{V_r + i_{Lr}(\frac{L}{\Delta t} - \frac{R_r}{2})}{\frac{L}{\Delta t} + \frac{R_r}{2}}$$

(2.11)

$$v_{ee} = \frac{\frac{C}{\Delta t} - \frac{1}{2(R_{ee} + R_g)}}{\frac{1}{\Delta t} \frac{1}{2(R_{ee} + R_g)}} v_{ee} \qquad (2.12)$$

The output voltage is given by

$$v_{re} = v_{ce} \frac{R_o}{R_{re} + R_o}$$

(2.13)

where  $v_{ce}$  is the output voltage at the end of the interval  $\Delta t$ . By applying these relationships to the successive time intervals the values of  $i_t$  and  $v_e$  at the end of the ON interval can be found if the duty ratio D is known. These values are used as the starting values of the OFF state. A procedure for determining the duty ratio D is described in section 2.1.3.

Neglecting the resistances,  $R_{nr}$  and  $R_s$  in equation 2.11 to 2.13, simplified results are obtained for the inductor current and capacitor voltage, which are given as

$$i_{L} = \frac{V_i + i_L \left(\frac{L}{\Delta t}\right)}{\frac{L}{2\tau}}$$

(2.14)

$$v_{ce} = \frac{\frac{C}{\Delta t} - \frac{1}{2(R_g)}}{\frac{C}{\Delta t} + \frac{1}{2(R_g)}} v_{ce}$$

(2.15)

During the ON state the energy is drawn from the output capacitor to the load and during the OFF state energy is supplied by the source to the load. The change in capacitor voltage (neglecting the inductor and capacitor resistances) is given by

$$\Delta V_{01} = \frac{1}{C} I_{\sigma} I_{\infty} = \frac{I_{\sigma}}{C} .D I_{S} = \frac{V_{O} .D I_{S}}{C .R_{O}}$$

(2.16)

where T is the ON time period

$T_s$  is the total time period of one switching cycle

$I_{\star}$  is the discharging current through the output capacitor

D is the duty ratio

The power output of the converter circuit is given by

$$P_{o} = \frac{V_{ref}^{2}}{R_{o}}$$

(2.17)

where

P is the total power output of the circuit

V is the reference output voltage

Substituting equation 2.17 into equation 2.16 gives

$$\Delta V_{01} = -\frac{P_a \cdot V_a \cdot D}{V_{rof}^2 \cdot C \cdot F_t}$$

(2.18)

The minus sign denotes the capacitor is discharging during the ON period and there will be a drop in the output voltage.

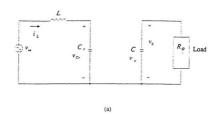

#### 2.1.1.2 THE OFF STATE

The equivalent circuit for the OFF state is shown in fig 2.3. The governing equations of the inductor current and capacitor voltage are obtained as

$$L\frac{di_{L}}{dt} = v_{i} - i_{L}(R_{s} + \frac{R_{ev} \cdot R_{o}}{R_{ev} + R_{o}}) - v_{\varepsilon} \frac{R_{o}}{R_{ev} + R_{o}}$$

(2.19)

$$C\frac{dv_{\epsilon}}{dt} = \frac{i_{L}R_{o}}{R_{esr} + R_{o}} - \frac{v_{\epsilon}}{R_{esr} + R_{o}}$$

(2.20)

and the output voltage is given by

$$v_o = (v_e + i_L R_{er}) \frac{R_o}{R_o + R_{er}}$$

(2.21)

Figure 2.3 : OFF state equivalent circuit

Using the approximations introduced for the ON state (equations 2.7 to 2.10), the values of  $i_{\nu}$ ,  $v_{\alpha}$  and  $v_{\omega}$  at the end of the OFF interval are derived from equations 2.19 to 2.21. Using MAPLE [37] to solve 2.19 and 2.20, the values of  $i_{\nu}$ ,  $v_{\alpha}$  and  $v_{\omega}$  can be determined. The general results are given in Appendix A.

Neglecting the resistances,  $R_{nr}$  and R, in equation A.1 and A.2, simplified results can be obtained for the inductor current and capacitor voltage, which are given as

(2.23)

$$i_{\mathcal{U}} = \left\{ \frac{-2 F_{i} C_{i} + 2 F_{i}^{3} F_{i} - \sqrt{A_{i}} V_{i} F_{i}^{3} - 4 C_{i} V_{i} L - \sqrt{A_{i}} C_{i} V_{i} + \sqrt{A_{i}} L i_{\mathcal{U}} F_{i} + 4 F_{i}^{3} V_{i} L}}{\left( L \left[ \sqrt{A_{i}} F_{i}^{2} - 4 F_{i}^{3} . L - \sqrt{A_{i}} C_{i} + 4 C_{i} . L - \sqrt{A_{i}} F_{i} \right] \right)} \right\}$$

$$v_{\alpha'} = \left\{ \frac{-\sqrt{A_{i}} v_{\alpha'} B_{i} + 2 C_{i} . i_{\mathcal{U}} . R_{0} . L + 2 C_{i} V_{i} . R_{0} - 2 B_{i}^{2} . i_{\mathcal{U}} . R_{0} . L - 2 B_{i}^{2} V_{i} . R_{0}}{\sqrt{A_{i}} B_{i}^{3} + 2 C_{i} . L + \sqrt{A_{i}} . C_{i} - \sqrt{A_{i}} . B_{i} - 2 B_{i}^{2} . L} \right\}$$

where

$$A_{i} = L^{2} + 4 \cdot L \cdot C \cdot R_{o}^{2} \qquad F_{i} = L \cdot v_{cc} \cdot R_{o} \cdot C$$

$$B_{i} = e^{\left(0.5 + \frac{\left(-\sqrt{A_{i} - 2 \cdot L}\right)^{i}}{\left(R_{o}\right) \cdot L \cdot C}\right)} \qquad C_{i} = e^{\left(2 \cdot \frac{r}{\left(R_{o}\right) \cdot C}\right)}$$

The values at the end of the OFF state are used as the starting values for the next ON state. Since the switching frequency  $(F_g)$  is known, the OFF time period can be calculated as

$$t_{\text{eff}} = (1 - D) / F_s$$

(2.24)

This process is repeated for the full cycle of the input voltage. During the OFF state, the output voltage is determined by the discharging current from the inductor and the supply voltage as

$$\Delta V_{o2} = \frac{(I_{pk} + I_2)(1 - D)}{2C.F_s} \tag{2.25}$$

where

I,k is the inductor current value at the end of the ON period

12 is the inductor current value at the end of OFF period

Combining the equations 2.24 and 2.25, a linearised equation for the output voltage is obtained as

$$V_{O(n)} = V_{O(n-1)} + (\Delta V_{O1} + \Delta V_{O2})$$

(2.26)

$$V_{o(n)} = V_{o(n-1)} + \left( -\frac{P_0 V_0 D}{V_{oq}^2 \cdot C.F_n} + \frac{(I_{pt} + I_2)(1 - D)}{2C.F_n} \right)$$

(2.27)

The resulting theoretical input current waveform of the CFCC scheme for a half-cycle is shown in fig 2.4. The waveform shows that the input current is continuous, i.e. non zero except at the zero crossings of the input voltage.

Figure 2.4: Theoretical input current waveform of the CFCC control scheme

### 2.1.2 MODELLING AND ANALYSIS OF THE CONTROL CIRCUIT

Referring to fig 2.1, a sample of the rectified line waveform  $(v_{\omega})$  is supplied to the block K. The second input signal to the block 'K' is a DC voltage proportional to the rms value of the line voltage. This signal is used to provide low output distortion and good transient response. A passive low-pass filter  $(R_1 - R_2 - C_{\omega})$  is used to generate this signal. The output of the filter at the start of a switching evel is

$$V_{stat(n)} = V_{stat(n-1)} + \frac{\left(\frac{V_{st} - V_{stat(n-1)}}{R_1}\right) - \frac{V_{stat(n-1)}}{R_2}}{C_{cr}F_s}$$

(2.28)

where:

$R_1$ ,  $R_2$  and  $C_{av}$  are the resistances and capacitor of the low pass filter respectively n is the number of the switching cycle

In the CFCC circuit [fig 2.1], the error amplifier which is used in the voltage feedback loop, is designed with a very slow frequency response. To achieve this slow frequency response, the corner frequency is chosen to be in the range 15-30Hz. The governing equation of the error amplifier is

$$V_{e(n)} = V_{e(n-1)} - \frac{(V_o - V_{ref})}{R_1} + \frac{(V_{e(n-1)} - V_{ref})}{R_f}$$

$$C_f \cdot F_r$$

(2.29)

In the control circuit, an error amplifier is used in the outer voltage feedback loop.

Figure 2.5 shows the error amplifier which is assumed to be a single order integrator.

Assuming an ideal op-amp the feedback current can be expressed as

$$i_{FB} = \frac{v_O - v_{ref}}{R_1} - \frac{v_{ref}}{R_k}$$

(2.30)

$$v_{el} = v_{ref} - v_{ef} - i_{FB}R_f$$

(2.31)

where

$i_{FB}$  is the instantaneous value of the feedback current

$R_3$  and  $R_2$  are the resistances at the input of the error amplifier circuit

$v_{nf}$  is the instantaneous value of the reference output voltage

vel is the instantaneous value of the error amplifier output

Figure 2.5: The error amplifier used in the voltage feedback loop

For a small interval,  $\Delta t$ , the voltage across  $C_f$  is given by

$$\frac{\Delta v_{cf}}{\Delta t} = \frac{I_{RB}}{C_f}$$

(2.32)

Equations 2.30 to 2.32 can be applied during the ON or OFF interval to determine the error amplifier voltage  $\nu_{et}$  in each switching period. With  $\nu_{et}$  determined, equation 2.2 can be used to obtain the desired average current ( $I_{ee}$ ).

### 2.1.3 DETERMINATION OF THE DUTY RATIO, D

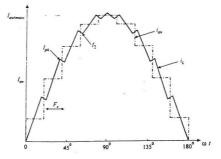

The duty ratio, D can be determined using an iterative procedure that continuously calculates the ON/OFF times. The computation method results in an exhausting program looping run time in finding the correct duty ratio, D. In order to improve the computer run time for the simulation program, the duty ratio is calculated within each switching cycle. Fig 2.6 shows the inductor current waveform in the continuous mode of operation.

It is assumed that the switch is turned OFF so that the inductor current at the end of the OFF state cycle  $(I_2)$  is such that the required average inductor current is obtained during the next switching cycle. This is an approximation since the response of the circuit is not so precise and the desired average inductor current does not remain constant.

Figure 2.6: Inductor current waveform in the continuous mode of operation

In steady-state operation the duty ratio, D, taking into consideration the resistances of the boost inductor, output capacitor and the load, is given by [35]

$$\frac{V_o}{V_m} = \frac{1}{D} \left[ \frac{\left(D'\right)^2 R_o}{R'} \right]$$

(2.33)

where

$$R' = R_s + \left(\frac{R_o * R_{esr}}{R_o + R_{esr}}\right) * D' + \frac{R_o^2 * (D')^2}{R_o + R_{esr}}$$

Vo is the output voltage

Vin is the average rectified input voltage

Neglecting the equivalent series resistance of the output capacitor and the boost inductor equation (2.33) reduces to

$$\frac{V_o}{V_{ss}} = \frac{1}{1 - D} \tag{2.34}$$

The average inductor current over one switching cycle is given by

$$I_{uv} = I_2 + \frac{V_{us}D}{2LF_e}$$

(2.35)

From equations 2.34 and 2.35 the current  $I_2$  is obtained as

$$I_{2} = I_{ur} - \frac{V_{ur}(V_{Q} - V_{ur})}{2LF_{vQ}}$$

(2.36)

From Fig 2.6 12 is obtained as

$$I_2 = I_1 + \frac{V_{in}D}{F_rL} - \frac{(V_o - V_{in})(1 - D)}{F_rL}$$

(2.37)

where,  $I_1$  is the inductor current at the start of one switching cycle. The duty ratio

D is obtained from equation 2.37 as

$$D = \frac{F_{r}L(I_{2} - I_{1}) + V_{o} - V_{os}}{V_{o}}$$

(2.38)

Equation 2.38 gives the estimated duty ratio of an ON/OFF switching cycle.  $V_a$  and  $V_a$  are the respective average values of the output voltage and rectified input voltage

during the ON/OFF switching cycle. In a practical circuit the duty ratio D varies between 0.05 and 0.95. The duty ratio calculated from equation 2.38 is maintained within these limits

#### 2.1.4 DESIGN EXAMPLE

A design example is given to illustrate the procedure for determining the control circuit constants and the power circuit parameters for the following conditions

To determine the exact value of K (eqn 2.2), the desired maximum average input current ( $I_{avinus}$ ) is first calculated. Assuming that the stepped waveform,  $i_{av}$  (fig 2.4) follows a sinusoidal waveform, in phase with the input voltage, the desired peak average input current  $I_{avinus}$  at the minimum line voltage of 90V(rms), is obtained from

$$P_s = I_{sc}(rms) * V_{sc}(rms) = \frac{I_{sc}(rms)}{\sqrt{2}} * V_{in}(rms)$$

(2.39)

$$I_{av(max)} = \frac{P_a}{V_a(rms)} \cdot \sqrt{2} = \frac{400}{90} \cdot \sqrt{2} = 6.28A$$

(2.40)

Similarly the desired peak average input current  $I_{ev(max)}$  at the line voltage of 240V(rms) is obtained as

$$I_{av(max)} = \frac{400}{240} \cdot \sqrt{2} = 2.36A \tag{2.41}$$

At an input voltage of 240 V(rms) and  $I_{corea}$  of 2.36 A, the voltage  $V_{oe}$  is obtained from fig 2.1 as

$$V_{inst}(appr.) = \frac{2}{\pi}.V_{in}(pk).\frac{R_2}{R_2 + R_1} = \frac{2}{\pi}.240.\sqrt{2}.\frac{5.1}{5.1 + 270} = 4.01V$$

Assuming an error amplifier gain of 5 and a maximum error signal of 10, the maximum error voltage  $V_{s}$  (max) is

$$V_{..}(\text{max}) = 5*10 = 50V$$

Using these values the value of the block 'K' is obtained from equation 2.2 as

$$K = \frac{I_{\text{or}(max)}V_{\text{max}}}{V_{\text{max}}(pk)V_{\text{max}}} = 2.23x10^{-3}$$

(2.42)

If the average peak-to-peak ripple current ( $\Delta i$ ) of the boost inductor for each switching cycle is assumed to be 0.3 amp and the supply voltage  $v_i$  is assumed to be constant over one switching cycle, the ON time ( $t_{int}$ ) and OFF time ( $t_{int}$ ) are obtained from fig 2.6 as

$$t_{on} = \frac{L \Delta i}{V_{on}}$$

(2.43)

$$t_{nf} = \frac{L \Delta i}{V_n - V_{in}} \qquad (2.44)$$

The switching period  $(T_r)$  is given by

$$T_s = \frac{1}{F_s} = t_{on} + t_{off} \qquad (2.45)$$

Substituting the ON and OFF time in equation (2.45) gives

$$L = \frac{V_i \cdot (V_0 - V_i)}{F_i \cdot \Delta i \cdot V_a}$$

(2.46)

For an input voltage of 240 V(rms), output voltage at 380 V(dc), switching frequency of 100KHz and a ripple current of 0.3 amp, equation 2.46 gives

$$L = \frac{240\sqrt{2} * (380 - 240\sqrt{2})}{100 * 10^3 * 0.3 * 380} = 1.2 \text{ mH}$$

(2.47)

From the above design procedure the value of the boost inductor is chosen to be 1.5 mH.

The value of the output capacitor is determined by assuming that the peak-to-peak ripple voltage of the capacitor is 1.2%, i.e. a voltage of magnitude 4.56V is expected over the steady DC output voltage of 380V. To achieve the above mentioned peak-to-peak ripple voltage, the change in voltage across the capacitor in one switching cycle  $(\Delta V_{\sigma t})$  is first calculated. As both the supply and switching frequencies are known parameters, the number of switching sections for one cycle of supply frequency can be obtained as

$$S_s = \frac{T_p}{T_s} = \frac{16.667 \text{msec}}{10 \mu \text{sec}} \cong 1667$$

(2.48)

where

$T_{\rho}$  is the time period of the supply voltage

$T_s$  is the switching time of the boost switch

$S_s$  is the number of switching sections

Assuming equal change in capacitor voltage ( $\Delta V_{01}$ ) during each switching interval,  $\Delta V_{01}$  is calculated as

$$\Delta V_{01} = \frac{4.56}{1667} = 2.74 mV \tag{2.49}$$

When the switch is ON, the output capacitor supplies the load current, and the change in capacitor voltage is given by

$$\Delta V_{0i} = v_c - v_c(t = 0) = \frac{1}{C} \int_0^t I_c dt = \frac{I_c * t_{col}}{C}$$

(2.50)

Equation (2.50) may be written as

$$\Delta V_{\sigma i} = \frac{I_c * D * T_c}{C} = \frac{I_c * D}{C * F_c}$$

(2.51)

Substituting for D (from equation 2.34) in equation 2.51, gives

$$\Delta V_{qi} = \frac{I_c * (V_u - V_{in})}{V_u * C * F_i}$$

(2.52)

The discharging current of the capacitor during the ON time period is also the load current ( $I_{load}$ ) and can be written as

$$I_c = I_{Lood} = \frac{P_o}{V_o}$$

(2.53)

Substituting equation (2.53) in equation (2.52) gives

$$\Delta V_{oi} = \frac{P_a * (V_a - V_{ia})}{V_a^2 * C * F_s}$$

(2.54)

From equation (2.54) the value of the output capacitor is obtained as

$$C = \frac{P_o * (V_o - V_m)}{V_o^{1/2} * \Delta V_{OI} * F_i} = \frac{400 * (380 - 240\sqrt{2})}{380^2 * 100 * 10^3 * 2.74 * 10^{-3}} = 410 \mu F$$

(2.55)

A conservative value of  $470\,\mu F$  for the output capacitor is chosen for the simulation of the circuit.

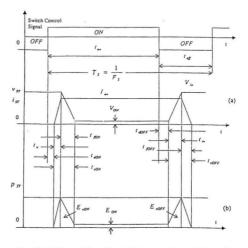

#### 2.1.5 POWER LOSS CALCULATION OF THE ROOST SWITCH

Power dissipation in semiconductor power devices is fairly generic in nature; that is, the same basic factors governing power dissipation apply to all devices in the same manner. The power converter under consideration represents the commonly encountered situation; the current flowing through a switch  $(i_{3T})$  also must flow through a series inductance. The design calculation therefore assumes an inductive load switching. Referring to fig 1.5 when the switch is ON,  $I_{se}$  flows through the switch while a voltage equal to the rectified input voltage  $(V_{se})$  appears across the switch for a small interval  $(I_{se})$ . During the OFF time  $I_{se}$  flows through the diode while a voltage equal to the rectified input voltage  $(V_{se})$  appears across the switch, assuming a zero voltage drop across the diode. Figure 2.7(a) shows the waveform for the current through the switch  $(I_{3T})$  and the voltage across the switch  $(V_{sT})$  when it is being operated at a repetition rate or switching frequency.

Figure 2.7: (a) Boost switch waveforms, (b) Instantaneous boost switch power loss

The switching waveforms are represented by linear approximation to the actual waveforms in order to simplify the discussion. As seen from fig 2.7(a), during the turn-ON transition of the boost switch, the current buildup consists of a short delay time

$t_{dON}$  followed by the current rise time  $t_n$ . The boost switch voltage ( $v_{eff}$ ) then falls to a small ON-state value of  $V_{ON}$  with a fall time of  $t_{fON}$ . The turn-ON crossover interval  $t_{cON}$  is given by

$$t_{cON} = t_n + t_{fON} \tag{2.56}$$

The energy dissipated in the device during this turn-ON transition can be approximated from fig 2.7(b) as

$$E_{con} = \frac{1}{2} * V_{in} * I_{iv} * t_{con}$$

(2.57)

The energy dissipation ( $E_{ov}$ ) in the switch during this ON-state interval can be approximated as

$$E_{on} = V_{on} * I_{ev} * t_{on}$$

(2.58)

where tox >> tcox . tcoff

During the turn-OFF transition period, the voltage buildup consists of a turn-OFF delay time  $t_{aoFF}$  and a voltage rise time  $t_n$ . Once the voltage reaches its final value of  $v_{xF}$ , then the current in the switch falls to zero with a fall time  $t_{poFF}$ . The turn-OFF crossover interval is given by

$$t_{cOFF} = t_{rr} + t_{fOFF} \tag{2.59}$$

The energy dissipated (  $E_{\rm cOFF}$  ) during tum-OFF transition can be written as

$$E_{cOFF} = \frac{1}{2} * V_{in} * I_{av} * t_{cOFF}$$

(2.60)

Figure 2.7(b) shows the instantaneous power dissipation ( $p_{ST} = v_{ST}^{m} i_{ST}^{s}$ ) across the boost switch. From equation 2.57 and 2.60 the average power loss ( $P_{SS}$ ) due to these transitions for a switching frequency of ( $F_{S}$ ) is given as

$$P_{SS} = \frac{1}{2} * V_{ss} * I_{ss} * F_{S} * [t_{cON} + t_{cOFF}]$$

(2.61)

The other major contribution to the power loss in the boost switch is the average power dissipated during the ON-state  $P_{ON}$ , which is given by

$$P_{QN} = V_{QN} * I_{av} * \frac{I_{out}}{T_S}$$

(2.62)

The leakage current during the OFF state of the boost switch is negligibly small and therefore can be neglected. Hence, the total average power dissipation ( $P_T$ ) across the boost switch is given by

$$P_T = P_{ss} + P_{ov} \tag{2.63}$$

The worst case power loss across the boost switch will occur at the peak input voltage. Using the equations 2.61, 2.62 and 2.63 and assuming  $t_n$ ,  $t_{pON}$ ,  $t_n$ ,  $t_{pOFP}$ ,  $V_{ON}$  to be 100ns, 50ns, 100ns, 200ns and 1.5V respectively, the average power loss at the peak input voltage for a constant switching frequency of 100kHz, is obtained as

$$P_T = \left[\frac{1}{2} * 240\sqrt{2} * 2.36 * 100 * 10^3 * 450 * 10^{-9}\right] + \left[1.5 * 2.36 * \frac{1\mu s}{10\mu s}\right] = 18.37W$$

(2.64)

# 2.1.6 SIMULATION OF THE PFC CIRCUIT FOR THE

I :-- -- !! 240!!! .

Normally the PFC circuit is operated at higher frequencies so as to reduce the total harmonic distortion of the input current. However, the circuit has been simulated at a reduced frequency in order to show the details of the waveform. The two values of switching frequency used for the simulation are 100KHz and 5KHz. The procedure outlined in the previous section is used to determine the circuit parameters at the two frequencies, which are as follows

1:-- --- 1/ - 1001//----

| Line voltage, $V_i = 240 V (mis)$            | Line voltage, $V_i = 100 V(mis)$             |

|----------------------------------------------|----------------------------------------------|

| Line frequency, $f_i = 60$ Hz                | Line frequency, $f_i = 60$ Hz                |

| Output Voltage, $V_{\pi} = 380 \text{V(dc)}$ | Output Voltage, $V_{\pi} = 200 \text{V(dc)}$ |

| Output power, $P_a = 400W$                   | Output power, $P_n = 160W$                   |

| Switching frequency, $F_s = 100 \text{kHz}$  | Switching frequency, $F_s = 5 \text{kHz}$    |

| Boost inductor, L = 1.5mH                    | Boost inductor, L = 5.5mH                    |

| Output capacitor, C = 470 μF                 | Output capacitor, $C = 1000 \mu F$           |

#### Per-unit values

| l p.u voltage = 240V                       | 1 p.u voltage =100V                       |

|--------------------------------------------|-------------------------------------------|

| 1 p.u power = 400W                         | 1 p.u power = 160W                        |

| 1 p.u current = $\frac{400}{240}$ = 1.67 A | 1 p.u current = $\frac{160}{100}$ = 1.6 A |

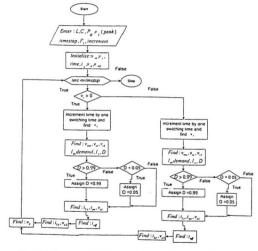

### 2.1.6.1 SIMULATION PROCEDURE

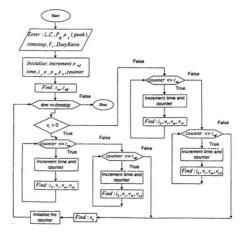

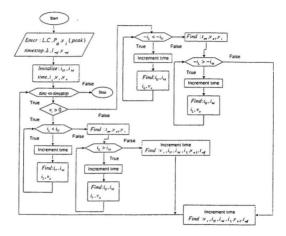

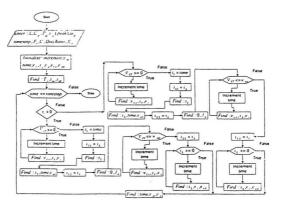

The flow chart of the complete simulation procedure of the CFCC control is given in fig 2.8. MATLAB is used to simulate the design equations.

Figure 2.8: Flow chart of the CFCC control scheme showing the simulation procedure

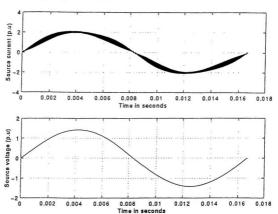

### 2.1.6.2 SIMULATION RESULTS

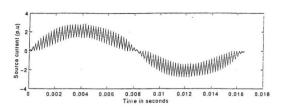

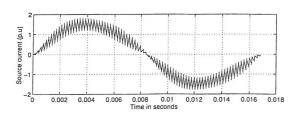

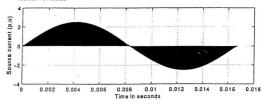

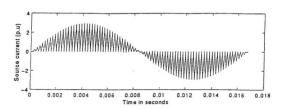

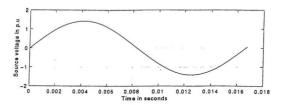

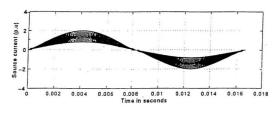

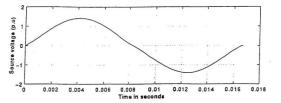

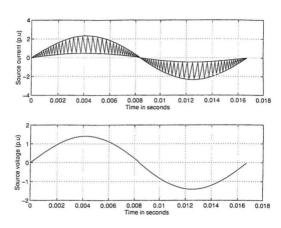

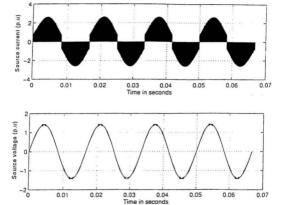

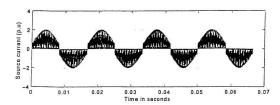

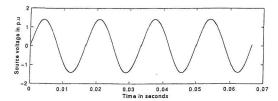

Figures 2.9 and 2.10 show the source current and source voltage in per unit at 100KHz and 5KHz respectively. As seen from the graphs, this control scheme is capable of producing nearly sinusoidal input current waveform.

Figure 2.9: Per-unit source current and source voltage waveforms

( L = 1.5mH, C = 470

$$\mu$$

F, F, = 100kHz)

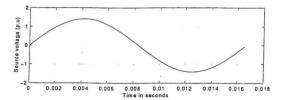

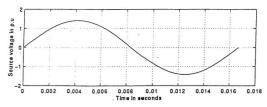

Figure 2.10 : Per unit source current and source voltage waveforms

( L = 5.5mH, C = 1000

$$\mu F$$

,  $F_{\rm r}$  = 5kHz)

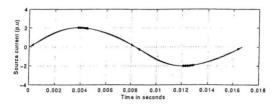

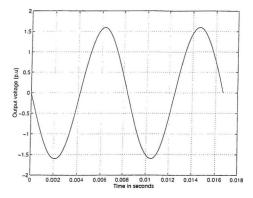

The total harmonic distortion (THD) for fig 2.9 is calculated to be 4%. The performance characteristics ( fig 2.11 and 2.12) show that the peak to peak ripple of the boost inductor current decreases with increase in the value of the boost inductor for a fixed output capacitor and switching frequency of 100kHz and 5kHz respectively.

Figure 2.11: Per unit source current and source voltage waveforms

$$(L = 5mH, C = 470 \mu F, F = 100kHz)$$

Figure 2.12: Per unit source current and source voltage waveforms

$$(L = 10mH, C = 1000 \mu F, F_r = 5kHz)$$

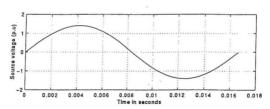

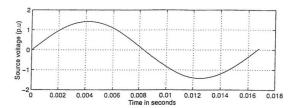

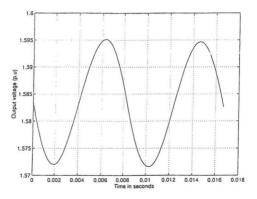

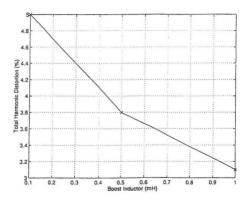

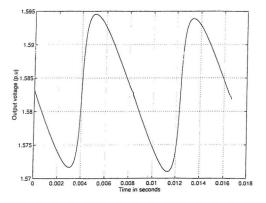

Figure 2.13 shows the per-unit output voltage ripple waveform. The peak-to-peak ripple on the output voltage is found to be 1.4% as assumed in the design example. Figures 2.14 and 2.15 show a plot of the total harmonic distortion (THD) of the source current with respect to varying boost inductor value and switching frequency respectively.

Figure 2.13: Per-unit output voltage waveform

( L = 1.5mH, C = 470

$$\mu$$

F, F, = 100kHz)

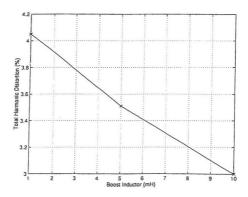

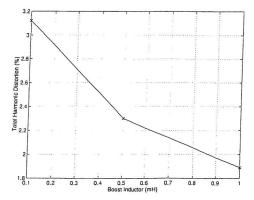

Figure 2.14: THD of the source current versus varying boost inductor

$$(C = 470 \,\mu F, F_s = 100 \,\text{kHz})$$

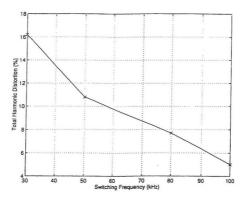

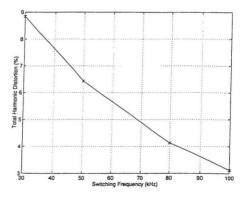

Figure 2.15 : THD of the source current versus varying switching frequency (L = 1.5 mH, C =  $470 \,\mu F$ )

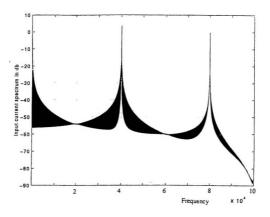

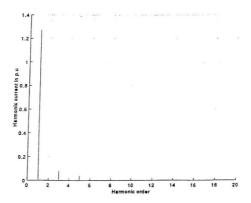

It can be seen that at constant switching frequency the THD decreases for increasing values of the boost inductor. Increasing values of boost inductor decreases the instantaneous input current value which in turn decrease the THD. It can be seen from fig 2.15 that for a given boost inductor, the THD decreases with increasing switching frequency. The turn ON time of the boost switch decreases with the increasing switching frequency which decreases the THD of the input current. Figure 2.16 shows the harmonic component of the input current (per-unit) with respect to the order of the harmonics.

Figure 2.16: Per-unit harmonic component of the source current versus harmonic order ( L = 1.5 mH,  $C = 470 \, \mu\text{F}$ , F = 100 kHz)

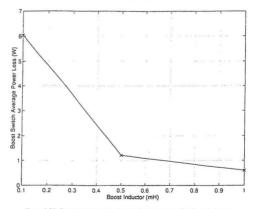

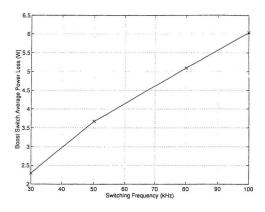

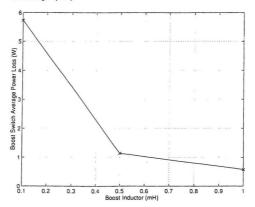

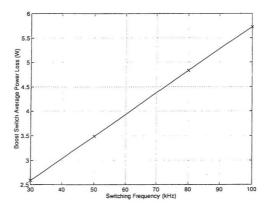

Figure 2.17 and 2.18 show the average power loss across the boost switch with respect to varying boost inductor value and switching frequency respectively.

Approximate average power loss is found to be 8.31W from fig 2.17 (for L=1.5mH). It can be seen that at constant switching frequency the average power loss decreases with increasing values of the boost inductor.

Figure 2.17: Power loss across the boost switch versus varying boost inductor ( C=470  $\mu$ F ,  $F_s$ =100kHz )

For a given boost inductor value the average power loss increases with increasing switching frequency. Figure 2.18 validates the equations 2.61 and 2.62, where it shows that the average power loss is proportional to the switching frequency.

Figure 2.18: Power loss across the boost switch versus varying switching frequency ( L=1.5mH,  $C=470~\mu F$  )

The main disadvantage of constant frequency continuous current control (CFCC) method is that there is a continuous finite value of current through and voltage across the boost switch at every switching instant. Hence, the boost switch is subjected to continuous power losses. The discontinuous current control can be implemented to minimize the continuous power losses in the switch.

## 2.2 CONSTANT FREQUENCY DISCONTINUOUS CURRENT CONTROL.

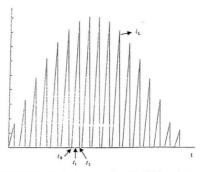

The constant frequency discontinuous current control scheme gives a discontinuous boost inductor current at a fixed switching frequency. The inductor current is allowed to decrease to zero at the end of the OFF interval, resulting in a discontinuous inductor current. In this scheme, the duty ratio is fixed for a given output voltage and the boost switch is operated at constant frequency.

This type of current control method is also used in rectifier converter circuits to achieve a constant DC output voltage and nearly unity power factor at the input. The drawback of the constant frequency continuous current control scheme, i.e. the continuous power loss of the boost switch, can be minimized by this type of control scheme.

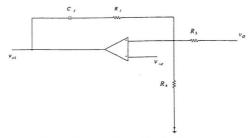

Fig 2.19 shows the constant frequency, discontinuous current control scheme. The actual DC output voltage is first compared with a reference through an error amplifier. The output of the error amplifier provides the reference current for the inductor current. The comparator (EA) compares the actual inductor current with the reference current. The output of the comparator is fed to a control block, P, which performs the function of a look-up table, giving the appropriate duty cycle which corresponds to the desired minimum output capacitor voltage. The look-up table has a set of duty ratios (D), preprogrammed for varying output voltage of the error amplifier.

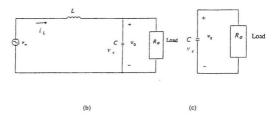

Figure 2.19: Control circuit of the CFDC control scheme

#### 2.2.1 MODELLING AND ANALYSIS OF THE CONTROL SCHEME

This section presents the modelling and analysis of the CFDC control scheme during the ON/OFF time of the boost switch (S). The peak current value during each ON interval is proportional to the average value of the input voltage during the same ON interval. Since the average value of the input voltage varies sinusoidally, the peak value of the input current peak also varies sinusoidally. In the analysis of the control scheme, the resistances associated with the boost inductor and the output capacitor are neglected.

#### 2.2.1.1 THE ON STATE

During the ON time of the boost switch (S) the input current  $(i_L)$  rises at the rate determined by the source voltage  $(v_i)$  and the boost inductor (L). Figure 2.20(a) shows the equivalent circuit when the boost switch is ON. The inductor current during this period  $(t_R \le t \le t_i)$  is given by,

$$V_{s}\sin(\omega r) = L\frac{di_{t}}{dt}$$

(2.65)

On solving equation 2.65 for  $i_L$  and substituting the initial conditions,  $i_L(\omega t_0) = 0$

$$i_{L}(\omega r) = \frac{V_{r}}{\omega L} \left[ \cos(\omega r_{0}) - \cos(\omega r) \right]$$

(2.66)

where

to is the instant at which the boost switch is turned ON

t, is the instant at which the boost switch is turned OFF