DESIGN AND IMPLEMENTATION OF ENCRYPTION Algorithms in a coarse grain Reconfigurable environment

CENTRE FOR NEWFOUNDLAND STUDIES

TOTAL OF 10 PAGES ONLY MAY BE XEROXED

(Without Author's Permission)

JASON P. RHINELANDER

National Library of Canada Bibliothèque nationale du Canada

Acquisitions and Bibliographic Services

Acquisisitons et services bibliographiques

395 Wellington Street Ottawa ON K1A 0N4 Canada 395, rue Wellington Ottawa ON K1A 0N4 Canada

> Your file Votre référence ISBN: 0-612-93054-8 Our file Notre référence ISBN: 0-612-93054-8

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, Ioan, distribute or sell copies of this thesis in microform, paper or electronic formats.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission. L'auteur a accordé une licence non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou alurement reproduits sans son autorisation.

In compliance with the Canadian Privacy Act some supporting forms may have been removed from this dissertation.

While these forms may be included in the document page count, their removal does not represent any loss of content from the dissertation. Conformément à la loi canadienne sur la protection de la vie privée, quelques formulaires secondaires ont été enlevés de ce manuscrit.

Bien que ces formulaires aient inclus dans la pagination, il n'y aura aucun contenu manquant.

# Canadä

## DESIGN AND IMPLEMENTATION OF ENCRYPTION ALGORITHMS IN A COARSE GRAIN RECONFIGURABLE ENVIRONMENT

BY

JASON P. RHINELANDER

A Thesis submitted to the School of Graduate Studies in partial fulfillment of the requirements for the degree of Master of Engineering

#### FACULTY OF ENGINEERING AND APPLIED SCIENCE

MEMORIAL UNIVERSITY OF NEWFOUNDLAND

2003

#### MASTER OF ENGINEERING THESIS

OF

#### JASON P. RHINELANDER

APPROVED: thesis Committee

Major Professors

DEAN OF THE SCHOOL OF GRADUATE STUDIES

#### MEMORIAL UNIVERSITY OF NEWFOUNDLAND

2003

## Abstract

In early 2000, Chameleon Systems Incorporated and Memorial University formed a research agreement to evaluate the viability of the Chameleon Systems CS2112 Reconfigurable Communications Processor (RCP) for use in implementing popular cryptographic algorithms. The CS2112 has a coarse grain reconfigurable architecture, capable of run time reconfigurability.

The benefit of coarse grain reconfigurable architectures is that they can offer many of the flexibilities found in software, such as reprogrammability and ease of modification to implementation, while giving performance advantages of speed and hardware encapsulation.

This research involves examining the implementation characteristics of two popular symmetric key block ciphers, RC5 and RC6, and two popular cryptographic hash algorithms, MD5 and SHA-1 with respect to the CS2112.

RC5 was designed as an iterative loop and then expanded to provide a parallel pipeline to maximize the usage of the reconfigurable fabric. RC6 was designed as an iterative loop and a pipeline. For both hash algorithms, initial designs were drafted and performance figures were estimated from experience gained through simulation and testing on a CS2112 development board.

By implementing these algorithms, the architecture of the CS2112 was evaluated for its suitability for cryptographic applications. Moreover, the reconfigurable fabric of the CS2112 was evaluated with respect to its support for the primitive operations that are required for cryptographic algorithms. The conclusions of this research and reccomendations for future research are directly related to resource use on the CS2112. In particular, support for control and datapath logic, memory space, and global communication resources within the CS2112 were all design constraints. More specifically, it would be advantageous to have direct support for accessing memory without using datapath resources. Also hardware support for data dependent logical rotations and unsigned integer multiplications would greatly save resource usage and increase performance. Finally the design process for the CS2112 was sometimes time intensive and cumbersome, especially with respect to layout and placement of reconfigurable logic. Advances in the area of automatic placement and layout for coarse grain primitives would benefit the design process for the CS2112 versity.

## Acknowledgements

I would like acknowledge the sources of help that I have received while pursuing my Masters' degree in Electrical Engineering. I would like to thank my supervisors, Dr. Howard Heys, and Dr. Ramachandran Venkatesan, not only for their superb guidance throughout my work, but for introducing me to the field of cryptography and hardware design. I would also like to thank Dr. Mark Rollins from Chameleon Systems Incorporated for his technical support and guidance.

This thesis would not have been possible without the sources of funding from: The School Of Graduate Studies at Memorial University, Dr. Heys and Dr. Venkatesan, Chameleon Systems Inc. and the Government of Newfoundland and Labrador.

I would like to thank numerous colleagues and friends for their assistance and support throughout the duration of my Masters research. I would like to thank my parents for their constant support and guidance in all my endeavours. My colleague Andrew Cook for his help and a 'fresh view on things''. My special friend Cindy O'Driscoil, for all her proofersading and grammatical expertise.

i

## Contents

| Abstract                                         | ii   |

|--------------------------------------------------|------|

| Acknowledgements                                 | iv   |

| Acknowledgements                                 | iv   |

| Table of Contents                                | v    |

| List of Tables                                   | ix   |

| List of Figures                                  | x    |

| List of Abbreviations                            | xiii |

| 1 Introduction                                   | 1    |

| 1.1 Motivation for Research                      | 5    |

| 1.2 Research Scope                               | 6    |

| 1.3 Thesis Outline                               | 7    |

| 2 Block Ciphers, Hash Functions and Applications | 8    |

| 2.1 Symmetric Key Block Ciphers                  | 8    |

| 2.1.1 Electronic Codebook Mode (ECB)             | 10   |

| 2.1.2 Cipher-block Chaining Mode (CBC)           | 10   |

| 2.2 Hash Functions                               | 11   |

|   | 2.3 | Description of an HMAC                                   | 12 |

|---|-----|----------------------------------------------------------|----|

|   | 2.4 | The RC5 Block Cipher                                     | 15 |

|   | 2.5 | The RC6 Block Cipher                                     | 16 |

|   | 2.6 | The MD5 Algorithm                                        | 18 |

|   | 2.7 | The SHA-1 Algorithm                                      | 21 |

|   | 2.8 | An Example Application: The IP Security Protocol (IPSec) | 24 |

|   |     | 2.8.1 Authentication Header Protocol                     | 25 |

|   |     | 2.8.2 Encapsulating Security Payload Protocol            | 26 |

|   | 2.9 | Concluding Remarks                                       | 28 |

|   |     |                                                          |    |

| 3 |     |                                                          | 29 |

|   | 3.1 | Software vs. Hardware Algorithms                         | 29 |

|   | 3.2 | Application-Specific Integrated Circuits                 | 30 |

|   |     | 3.2.1 Designs and Performance                            | 32 |

|   | 3.3 | Field-Programmable Gate Arrays                           | 33 |

|   |     | 3.3.1 Implementations and Performance                    | 35 |

|   | 3.4 | Coarse Grain Reconfigurable Architecture                 | 36 |

|   |     | 3.4.1 Survey of Existing Technologies                    | 41 |

|   |     | 3.4.2 Cryptographic Applications                         | 42 |

|   | 3.5 | Chameleon Systems CS2112                                 | 43 |

|   |     | 3.5.1 CS2112 High Level Architecture Description         | 44 |

|   |     | 3.5.2 CS2112 Data Path Unit                              | 46 |

|   |     | 3.5.3 CS2112 Local Store Memory                          | 48 |

|   |     | 3.5.4 CS2112 Multiplier                                  | 48 |

|   |     | 3.5.5 CS2112 Control Logic Unit                          | 50 |

|   |     | 3.5.6 Design Process For The CS2112 Fabric               | 51 |

| Syn | ametric Block Cipher Design and Implementation                                                                     | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|-----|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.1 | Diagram Use                                                                                                        | 55                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4.2 | RC5 Designs                                                                                                        | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 4.2.1 RC5 Simple Iterative Design                                                                                  | 57                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 4.2.2 Two Half-Round, Full Slice Version of RC5                                                                    | 64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 4.2.3 Full Fabric RC5 Design                                                                                       | 68                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 4.2.4 Summary of RC5 Results                                                                                       | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

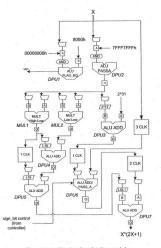

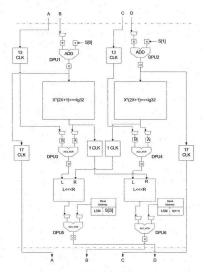

| 4.3 | RC6 Designs                                                                                                        | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 4.3.1 Unsigned 32-bit Integer Multiplication                                                                       | 70                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

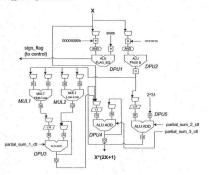

|     | 4.3.2 Iterative RC6 Design                                                                                         | 73                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 4.3.3 Pipeline Primitives                                                                                          | 75                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 4.3.4 Pipelined Multiplication                                                                                     | 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 4.3.5 RC6 Full Pipelined Design                                                                                    | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 4.3.6 Summary of RC6 Designs                                                                                       | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 4.4 | Summary                                                                                                            | 87                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

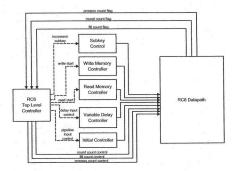

| Eva | luation of Message Digest Algorithms                                                                               | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5.1 | MD5 Implementation                                                                                                 | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 5.1.1 Performance and Usage Estimates for MD5                                                                      | 91                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5.2 | SHA-1 Implementation                                                                                               | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 5.2.1 Recursive Array Expansion                                                                                    | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

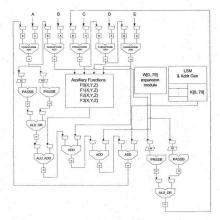

|     | 5.2.2 SHA-1 Auxiliary Function Design                                                                              | 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 5.2.3 Full SHA-1 Datapath                                                                                          | 96                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|     | 5.2.4 Performance and Resource Usage of SHA-1                                                                      | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5.3 | Comparison of SHA-1 and MD5 Implementations                                                                        | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 5.4 | Summary                                                                                                            | 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|     | <ul> <li>4.1</li> <li>4.2</li> <li>4.3</li> <li>4.4</li> <li>Eva</li> <li>5.1</li> <li>5.2</li> <li>5.3</li> </ul> | 4.2       RC5 Designs         4.2.1       RC5 Simple Iterative Design         4.2.2       Two Half-Round, Full Slice Version of RC5         4.2.3       Full Fabric RC5 Design         4.2.4       Summary of RC5 Results         4.3       RC6 Designs         4.3.1       Unsigned 32-bit Integer Multiplication         4.3.2       Iterative RC6 Design         4.3.3       Unsigned 32-bit Integer Multiplication         4.3.4       Pipelined Frimitives         4.3.5       RC6 Full Pipelined Design         4.3.6       Summary <b>Evaluation of Message Digest Algorithms</b> 5.1       MD5 Implementation         5.2       SHA-1 Implementation         5.2.1       Recursive Array Expansion         5.2.2       SHA-1 Auxiliary Function Design         5.2.3       Full SHA-1 Datapath         5.2.4       Performance and Resource Usage of SHA-1         5.3       Comparison of SHA-1 and MD5 Implementations |

| 6  | Sun        | amary and Conclusions                                    | 101  |

|----|------------|----------------------------------------------------------|------|

|    | 6.1        | Summary of Results                                       | 101  |

|    | 6.2        | CS2112 Architectural and Support Features                | 102  |

|    | 6.3        | Considerations For Future Work                           | 103  |

| Li | st of      | References                                               | 105  |

| Aj | open       | dices                                                    | A-1  |

| A  | San        | aple Verilog Code for Selected Modules                   | A-1  |

|    | A.1        | RC5 Testbench                                            | A-1  |

|    | A.2        | Iterative RC5 Top Level Module                           | A-1  |

|    | A.3        | Iterative RC5 Controller Module                          | A-2  |

|    | A.4        | Iterative RC5 Datapath Module                            | A-6  |

|    | A.5        | Unsigned Integer Multiplier Module Controller            | A-12 |

|    | A.6        | Unsigned Integer Multiplier Module Datapath              | A-14 |

|    | A.7        | Verilog Testbench For Controlling RC5 Iterative Pipeline | A-19 |

| в  | AN         | SI C Code for Select Implementations                     | B-2  |

|    | B.1        | RC5 C Code For Testing                                   | B-2  |

|    | <b>B</b> 2 | BC6 C Code For Testing                                   | R.4  |

## List of Tables

| 3.1  | Results from AES candidates in ASIC technology                            | 32  |

|------|---------------------------------------------------------------------------|-----|

| 3.2  | Simulation results from RC6 ASIC designs using 128 bit keys               | 33  |

| 3.3  | Some results of FPGA simulations of AES candidates.                       | 35  |

| 3.4  | Some results of FPGA implementations of RC6                               | 36  |

| 3.5  | Survey of existing coarse grain reconfigurable technologies               | 41  |

| 4.1  | Resource usage for the simple iterative version of RC5                    | 63  |

| 4.2  | Timing information for the simple iterative version of RC5                | 64  |

| 4.3  | Resource usage for the two half-round design of RC5.                      | 67  |

| 4.4  | Timing for the full slice design of RC5.                                  | 68  |

| 4.5  | Resource use for the full fabric version of RC5 (control logic excluded). | 69  |

| 4.6  | Resource estimates for a single slice of RC6 in the fabric                | 75  |

| 4.7  | Timing information for the RC6 pipeline.                                  | 84  |

| 4.8  | Resource usage for a fully pipelined RC6                                  | 85  |

| 4.9  | Control logic resource usage for a fully pipelined RC6 design             | 86  |

| 4.10 | Summary of block ciphers on the CS2112.                                   | 88  |

| 5.1  | Resource usage for preliminary MD5 implementation                         | 93  |

| 5.2  | Delay through MD5 datapath.                                               | 93  |

| 5.3  | Resource utilization of SHA-1.                                            | 99  |

| 5.4  | Summary hash algorithms on the CS2112                                     | 100 |

| 6.1  | Summary of designs on the CS2112.                                         | 101 |

## List of Figures

| 1.1  | Description of encryption with respect to a data network        | 3  |

|------|-----------------------------------------------------------------|----|

| 2.1  | Block diagram of secure communications                          | 9  |

| 2.2  | ECB mode.                                                       | 10 |

| 2.3  | CBC mode                                                        | 11 |

| 2.4  | Operation of HMAC.                                              | 14 |

| 2.5  | Flow diagram of the RC5 block cipher.                           | 16 |

| 2.6  | Illustration of a simplified 8-bit left data dependent rotation | 16 |

| 2.7  | Flow diagram of the RC6 block cipher.                           | 17 |

| 2.8  | Procedure of initial processing arbitrary length message        | 18 |

| 2.9  | Looking into the H_MD5 function                                 | 19 |

| 2.10 | Operations involved in a single step of H_MD5. $\ldots$         | 20 |

| 2.11 | Procedure of processing arbitrary length message                | 21 |

| 2.12 | A decomposition of the H_SHA1 function.                         | 22 |

| 2.13 | A decomposition of a step in the H_SHA1 function                | 23 |

| 2.14 | AH packet format.                                               | 26 |

| 2.15 | ESP packet format.                                              | 27 |

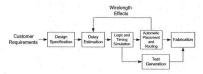

| 3.1  | A view of the ASIC design process.                              | 31 |

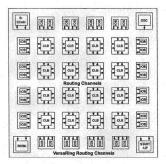

| 3.2  | Abstracted internal FPGA structure.                             | 34 |

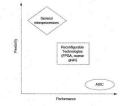

| 3.3  | Flexibility verses performance of hardware technologies         | 37 |

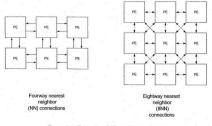

| 3.4  | Examples of 2D mesh connections.                                | 38 |

| 3.5  | An example of a linear array configuration.                     | 38 |

| 3.6  | An example of a crossbar configuration                             | 39 |

|------|--------------------------------------------------------------------|----|

| 3.7  | An example of a KressArray configuration. Multiple communication   |    |

|      | schemes between processing elements are used                       | 39 |

| 3.8  | Chameleon cipher chip, designed for encryption                     | 42 |

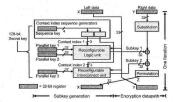

| 3.9  | Process of swapping active and background fabrics                  | 43 |

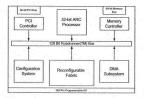

| 3.10 | High level block diagram of CS2112 components                      | 44 |

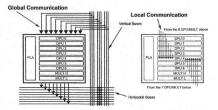

| 3.11 | High level decomposition of reconfigurable fabric.                 | 45 |

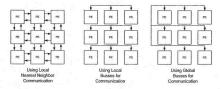

| 3.12 | Communication arrangement between processing elements              | 46 |

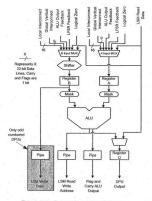

| 3.13 | Datapath unit block diagram.                                       | 47 |

| 3.14 | Multiplier block diagram                                           | 49 |

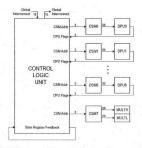

| 3.15 | CLU communication and interaction with processing elements         | 50 |

| 3.16 | Design flow for the CS2112.                                        | 52 |

| 3.17 | Screen capture of the graphical floorplanner                       | 53 |

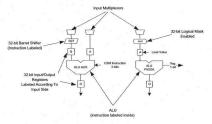

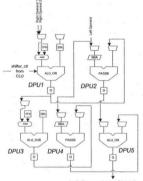

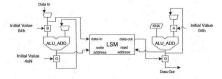

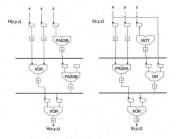

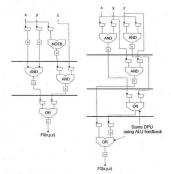

| 4.1  | Examples of configured DPU structures                              | 56 |

| 4.2  | Two methods for describing memory structures containing one LSM    |    |

|      | and one DPU                                                        | 57 |

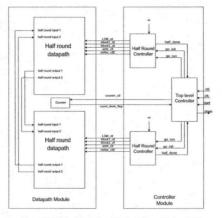

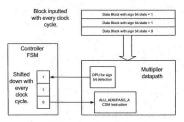

| 4.3  | Abstracted block digram of simple iterative RC5 design             | 59 |

| 4.4  | Structural diagram of data dependent rotation                      | 61 |

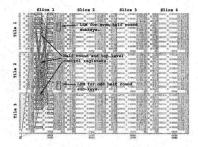

| 4.5  | C~SIDE floor<br>planner screen shot of simple iterative RC5 design | 63 |

| 4.6  | High level abstraction of the two half-round design of RC5         | 65 |

| 4.7  | Four DPU implementation of the data dependent rotation             | 66 |

| 4.8  | Screen capture of the two half-round RC5 fabric function           | 67 |

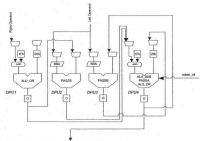

| 4.9  | Screen capture of the full fabric RC5 implementation               | 69 |

| 4.10 | Creating a 32-bit unsigned integer multiplier                      | 71 |

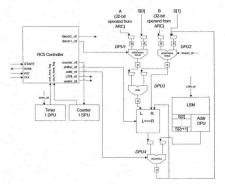

| 4.11 | Iterative multiplier setup.                                        | 73 |

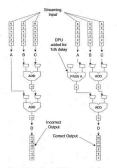

| 4.12 | Need of delay in a pipeline.                                       | 77 |

| 4.13 | First-in, first-out queue setup.                                   | 78 |

| 4.14 | Pipelined multiplier module                      |  |

|------|--------------------------------------------------|--|

| 4.15 | Multiplier and controller interaction            |  |

| 4.16 | Fixed logical rotation by five bits              |  |

| 4.17 | One full round of RC6                            |  |

| 4.18 | Description of control and datapath interaction  |  |

| 4.19 | RC6 pipeline floorplan                           |  |

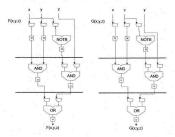

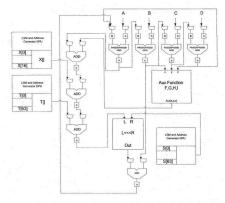

| 5.1  | Implementation of F and G functions              |  |

| 5.2  | Implementation of H and I functions              |  |

| 5.3  | A proposed MD5 datapath for one step of H_MD5 92 |  |

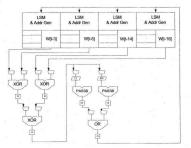

| 5.4  | Recursive expansion of W[015] to W[079]          |  |

| 5.5  | Auxiliary function implementation                |  |

| 5.6  | Auxiliary function implementation                |  |

| 5.7  | SHA-1 datapath design                            |  |

AES Advanced Encryption Standard

AH Authentication Header

ALU Arithmetic Logic Unit

ARC Argonaught RISC Core

ASIC Application-Specific Integrated Circuit

CBC Cipher-block Chaining Mode

CLB Configurable Logic Block

CLU Control Logic Unit

CMOS Complementary Metal Oxide Semiconductor

CSM Control Store Memory

**DES** Data Encryption Standard

DMA Direct Memory Access

DPU Data Path Unit

**DSA** Digital Signature Algorithm

DSP Digital Signal Processing

ECB Electronic Codebook Mode

ESP Encapsulating Security Payload

FIR Finite Impulse Response

FPGA Field-Programmable Gate Array

FSM Finite State Machine

HDL Hardware Description Language

HMAC Hashed Message Authentication Code

ICV Integrity Check Value

IOB Input Output Block

**IP** Internet Protocol

IPSec IP Security Protocol

LSM Local Store Memory

MAC Message Authentication Code

MD Message Digest

MSP Message Security Protocol

NESSIE New European Schemes for Signatures, Integrity, and Encryption

NIST National Institute of Standards and Technology

PE Processing Element

PGP Pretty Good Privacy

PIO Programmable Input Output

PLA Programmable Logic Array

RCP Reconfigurable Communications Processor

RTL Register Transfer Level

S-HTTP Secure Hypertext Transfer Protocol

SA Security Association

SRB State Register Block

SSL Secure Sockets Layer

VPN Virtual Private Network

## Chapter 1

## Introduction

It is hard to imagine today's society without modern communication systems. While it is a necessity for people to communicate with each other to share information, the way in which this is undertaken has changed dramatically since the advent of global voice and data networks.

The Internet has grown at an exponential rate in the last decade. Not only are people using the Internet as a medium for communication, but the transmission and storage of sensitive data has also seen increased usage. Online banking is a good example of both the transmission and storage of sensitive data. A person must transmit their account number along with a password to access their personal information and accounts stored on the bank's computers. By the year 2007 it is estimated that 30% of Americans will use online banking and in the salary range of \$50,000-\$75,000, usage will be 50% [1]. With respect to the Internet economy, quarterly growth figures between 1999 and 2000 were estimated to be between 20% and 30% [2]. Corportations are utilizing Virtual Private Networks (VPNs) to connect remote locations to the private infrastructure of the company network.

While modern communication through global networks has increased communication efficiency, it has also become easy for people to intercept data traveling across shared networks such as the Internet. For example, a packet sniffer is a system that looks at traffic flowing across a network so that a third party can view private information. A packet sniffer is a common way to obtain user IDs and passwords [3].

Cryptography can be used to provide security to information flowing through a publicly accessible network. Most cryptographic applications lie in the digital world of computers, but cryptography has a much older past. Given below are some interesting facts about the history of cryptography [4]:

- The first known emergence of a cryptographic substitution cipher occurred around 1900 B.C. in a town called Meneu Khufu, near the river Nile. Some unique hieroglyphic symbols were used in place of normal ones.

- Ancient Egyptians used substitutions of hieroglyphs, and the use became more popular with the increasing occurrence of tombs.

- Mechanical encryption devices were used extensively in World War II for the encryption of military and political messages.

- Some of the first mechanical computers were invented and used by Marian Rejewski to break codes produced from the German WWII Enigma machine [5].

The use of data networks has been increasing at an astonishing rate and with this growth in use, there is a need to secure private information across the network. Within the scope of data security, encryption plays a large role. Encryption provides data confidentiality, but there is also a need for the following security services [6]:

- Access Control: Maintains privileged access to information.

- Data Integrity: Prevents unauthorized modification of information.

- Authentication and Replay Prevention: Verifies a sender's identity and prevents unauthorized re-transmission of information.

- · Scalable Key Management: Allows the secure deployment of cryptographic keys.

- Accountability and Non-repudiation: Maintains the identity of sender and prevents deniability.

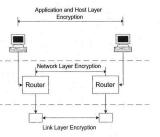

The support of data integrity within a data network prevents the modification of data while it is in transit across the network. A data integrity service over a network often uses a hash function to produce a Message Digest (MD) of a message. A digital signature technique such as the Digital Signature Algorithm (DSA) also uses a hash algorithm in its operation [7]. Figure 1 is a typical hierarchy with respect to encryption in a data network.

Figure 1.1: Description of encryption with respect to a data network.

Encryption algorithms, or ciphers, can be implemented in hardware or software. Some examples of popular secure communication protocols that are targeted for software encryption are: Secure Hypertext Transfer Protocol (S-HTTP), Pretty Good Privacy (PGP), Message Security Protocol (MSP), Secure Sockets Layer (SSL) and IP Security Protocol (IPSec). Software encryption implementations are slower than hardware implementations. Hardware implementations are used in high bandwidth, low latency environments such as the link layer of a data network [6]. In addition to potentially higher performance compared to software, hardware based encryption can often be more secure than software. It is harder for an attacker to obtain information about the cipher during operation [8].

There are various ways of implementing encryption algorithms in hardware. One way is through a special cryptographic processor that can be configured for various algorithms. One example can be found in the CryptoManiac device [9]. CryptoManiac is a cryptographic co-processor and is designed to speed software encryption. Broadcom offers two cryptographic co-processors (BCM5840/41) that work at the host level to aid encryption speeds of software [10]. Another way to use hardware encryption is through an Application-Specific Integrated Circuit (ASIC) or Field-Programmable Gate Array (FPGA) technology.

The field of ASICs is a broad one. ASICs can be full custom integrated circuits or semi-custom. A full-custom ASIC engineer will design some or all of the logic, circuits and layout for a particular chip. In most application areas full-custom ASICs are not as popular as they once were, but they are growing in the area of integrated analog and digital ASICs [11]. Semi-custom ASICs are designed using standard cells that provide functionality as simple as logic gates to the level of complexity of microprocessor cores. Once the design is simulated and laid out it can be fabricated. The fabrication of an ASIC involves the masking of layers of silicon similarly to standard integrated circuits. Once the design is fabricated it cannot be changed.

An ASIC implementation is specifically designed for the cipher(s) of choice and has the main advantage of speed. Another advantage of ASICs is that the designer has complete control over placement, and is limited only by the design rules imposed by the fabrication process. Cost, design time and lack of flexibility are some

#### disadvantages of ASIC design.

FPGAs are a more flexible way of designing algorithms in hardware. FPGAs were developed initially as a fast way to prototype cells to be used in ASIC designs. Since then FPGAs have grown in size and capability allowing designers to implement market products in FPGAs. FPGAs contain programmable logic devices that are set by antifuse or static random access memory technology. The matrix of programmable logic cells are connected together by a network of wires allowing communication between cells [12].

An FPGA solution is considered to be a fine grain reconfigurable solution and will allow faster design cycles because designs can be re-burned or reconfigured without restarting the whole design process as with ASICs. A disadvantage of FPGA implementation is that routing can have overhead and can be problematic [13].

Newer coarse grain architectures are emerging to exploit the advantages of hardware while simultaneously offering the flexibility of software. Run-time reconfigurable processing, ease of modification, and quick turn around times in design and testing, are advantages of coarse grain architectures. Unlike an FPGA, coarse grain architectures can use datapaths that are greater than 1-bit [13].

#### 1.1 Motivation for Research

The Chameleon Systems Inc. CS2112 RCP is a coarse grain reconfigurable architeture [14] designed for communication and Digital Signal Processing (DSP) applications. The performance of coarse grain reconfigurable architectures with respect to cryptographic applications can be dependent on resources and characteristics offered by the specific reconfigurable product. With the increased need for secure communication, commerce, faster transmission speeds, and increased traffic over public networks, there is a need for implementation of new ciphers in hardware. A survey of companies in 2003 shows that medium to large sized businesses utilize hardware based security services over software based methods [15].

The Chameleon Systems CS2112 offers a reconfigurable environment for encryption that gives the security and performance of hardware while offering the flexibilities of software. Since the CS2112 is a general purpose communications processor with support for any of the arithmetic and logical operation found in encryption, a research agreement was developed between Memorial University and Chameleon Systems to investigate and evaluate the performance of popular ciphers on the CS2112 [16].

It is the purpose of this research to not only investigate the performance of popular encryption algorithms on the CS2112, but to investigate where the CS2112's architecture is inadequate to support these algorithms efficiently and to determine the advantages of using the CS2112 for security applications. Results of this research were reported back to Chameleon Systems Inc. for future design considerations.

#### 1.2 Research Scope

The purpose of this thesis is to investigate the suitability of symmetric key encryption and cryptographic hash algorithms on the Chameleon Systems RCP. Two symmetric key block ciphers that were explored are RC5 [17] and RC6 [18]. Hash functions that were explored are MD5 [19] and SHA-1 [7]. Various design methods of these algorithms were addressed along with testing and performance evaluation.

Before addressing the topic of this research, the reader will be given adequate background in cryptography, hardware implementation technologies for encryption algorithms, and a high level description of the CS2112 architecture. RCS was the first algorithm to be investigated and this focused on an iterative approach to cipher implementation. Optimizations to this design were carried out to maximize use of the CS2112. Next, RC6 was evaluated with a pipelined design optimized for high speed operation. MD5 and SHA-1 were designed based on information gained from designing RC5 and RC6 on the CS2112. When design and testing were completed the CS2112 is evaluated for its suitability for supporting the selected algorithms with respect to its processing resources and support for cryptographic primitives.

## 1.3 Thesis Outline

This thesis follows the outline below:

- Chapter One is an introduction to the research conducted with the CS2112.

- Chapter Two will introduce the reader to symmetric key block ciphers, cryptographic hash functions, and give an example of a popular protocol that makes use of both types of algorithms.

- Chapter Three will focus on different hardware implementation technologies while giving some examples of cryptographic applications and performance. The CS2112 is also introduced in Chapter Three outlining its architecture and target application areas.

- Chapter Four describes implementation and performance of symmetric key block ciphers on the CS2112.

- Chapter Five describes the design and performance of hash functions on the CS2112.

- Chapter Six provides conclusions with respect to the CS2112 and gives some recommendations on coarse grain architectural support for cryptography in relation to the CS2112.

## Chapter 2

## Block Ciphers, Hash Functions and Applications

The purpose of this chapter is to give an overview of symmetric key block ciphers, hash functions, and their applications such as the IP Security Protocol. Primitive operations that ciphers and hash functions utilize also will be discussed.

## 2.1 Symmetric Key Block Ciphers

When a message or plaintext is encrypted using an encryption algorithm, it is computationally infeasible to extract the information from the eiphertext unless the corresponding decryption algorithm is used. Cryptology is the field that is made up of Cryptography and Cryptanalysis. Cryptography is the field that involves mapping plaintext to eiphertext in a secure fashion. The purpose of Cryptanalysis is to test the security of eiphers by decrypting encrypted messages in a method not intended by the decryption algorithm, in effect testing the security of the encryption. A block eipher is a function that mathematically maps an *n*-bit plaintext block to an *n*-bit eiphertext block, with the block size defined to be n [20].

Extra information, called a key, is required to execute an encryption algorithm. If the same key is used for both encryption and decryption it is called a symmetric key cipher [17]. The use of a symmetric key block cipher to transmit an encrypted message is illustrated in Figure 2.1 [20].

The total possible number of keys is defined as the keyspace and the security of a cipher is related to both the keyspace and n. A cipher is unconditionally secure if ciphertext blocks and plaintext blocks are statistically independent. In general, an increase in block size and/or in size of the keyspace will increase the implementation cost of the cipher [20].

Figure 2.1: Block diagram of secure communications.

Iterated round ciphers involve a sequential loop of an internal function (a round), involving blocks of plaintext. A round consists of simple cryptographic operations such as additions and data dependent rotations. Each round uses a subkey that is derived from the original key that is mixed with the data. Virtually all block ciphers are iterated, and RC5 and RC6 operate in this fashion.

Block ciphers may be used in different modes of operation. Modes of operation will be discussed, Electronic Codebook Mode (ECB) and Cipher-block Chaining Mode (CBC). ECB is a mode that does not involve feedback of a previous operation, while CBC requires feedback from its previous operation. For the two modes of operation discussed, a brief explanation of the advantages and disadvantages with respect to security and error recovery will be presented.

#### 2.1.1 Electronic Codebook Mode (ECB)

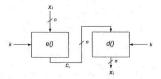

ECB is illustrated in Figure 2.2. The symbol n is the block size in bits,  $X_i$  represents the i-th block of plaintext  $C_i$  represents the i-th block of eiphertext, e() represents the encryption function, d() represents the decryption function, and k represents the key.

Figure 2.2: ECB mode.

When a message is more then *n*-bits long, it is sectioned into *n*-bit blocks, each block is encrypted separately, and decryption is carried out in a similar fashion. ECB mode has the advantage of being the simplest encryption mode. An error in a transmitted encrypted block will result in a full plaintext block being decrypted in error on the receiver's end. ECB mode has the disadvantage that it does not hide data patterns [20]. In ECB mode an observer can view ciphertext across an insecure network and may sometimes have knowledge of the plaintext that is being transmitted. The observer can then build a library of plaintext-ciphertext pairs allowing partial decryption of future messages.

#### 2.1.2 Cipher-block Chaining Mode (CBC)

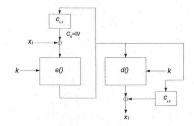

CBC is illustrated in Figure 2.3. CBC mode starts with an initial value or IV vector and subsequent encryptions are carried out with the use of the previous ciphertext block. The IV vector is required because this mode uses feedback. When the first plaintext block is encrypted there is no previous ciphertext block to use, therefore a value is provided externally so that the operation can proceed. CBC has the advantage of hiding patterns in plaintext values.

Figure 2.3: CBC mode.

Some of the disadvantages of CBC mode are that an error in the transmitted ciphertext block will result in an incorrect deciphering of  $C_i$  and  $C_{i+1}$ . In addition, the order of plaintext blocks matter because the decryption requires the receiver to have the previous block of ciphertext.

#### 2.2 Hash Functions

Hash functions take a finite arbitrary length input and output a fixed length message digest or simply a hash of the message. In other words, a hash function will map an arbitrary ranged input to a fixed and smaller ranged output [20]. Hash functions are used in both cryotographic and non-cryotographic applications. Cryptographic hash functions are one way functions, meaning that you cannot get the original input based solely on the output. A collision occurs when two inputs map to the same output value. The output value of a hash function is regarded as a compact digital image or representation of the input data. For cryptographic applications, a hash function must exhibit strong and weak collision avoidance. To explore the concept of strong and weak collision avoidance, the hash function will be defined as h(), the input to the function is x and another input to the function is x' (different than x). Strong collision avoidance is observed if it is computationally infeasible to find both x and x' such that h(x) = h(x'). Weak collision avoidance is observed in given x, finding x' such that h(x) = h(x') is infeasible [20].

Hash functions are primarily used in data integrity schemes and may be keyed or not keyed. A keyed hash function will take two inputs (data and a secret key) and produce one output referred to as a Message Authentication Code (MAG). A hash function that is not keyed can be configured as MACs producing an Hashed Message Authentication Code (HMAC).

For the purposes of this research single input, single output hash functions used for authentication schemes will be addressed.

#### 2.3 Description of an HMAC

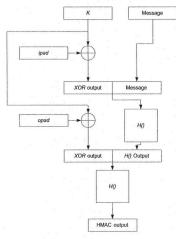

HMAC is a mechanism for message authentication that utilizes a cryptographic hash function. MACs provide a way to check the integrity of information transmitted across an insecure medium [21]. The HMAC scheme uses a cryptographic hash function and a secret key. The input information to an HMAC is the message to be authenticated, and the secret key. It is assumed that only the sender and receiver has access to the secret key. To describe the operation of HMAC, the following definitions are made [21]:

- H(), a cryptographic hash function that processes an arbitrary length message formatted into length B-byte blocks.

- L, byte length of hash function output. It is assumed that L will be less than B.

- K, the secret key used in the HMAC. The secret key is of variable length and any length that is less than B will have zero bytes appended to the end of the key. For key (K1) with length greater than B the following will occur, H(K1) = K2. K2 has a length of L, and will be used as the secret key.

- ipad, the value 0x36 repeated B times.

- opad, the value 0x5c repeated B times.

Figure 2.4 illustrates the operation of an HMAC. In illustrations, adjoining blocks of data represent the appending of two blocks into a single, larger block. The  $\oplus$ operator is the bit-wise XOR operation.

The construction of an HMAC provides two functions. The integrity of the message is protected because the cryptographic hash function provides a digital fingerprint of the original text. A message cannot be forged because a secret key is mixed into the HMAC. HMACs are used in the Authentication Header (AH) protocol within IPSec.

The performance of the HMAC depends on the underlying hash function and it is desired to use hash functions that will perform well in software. The main goal is to make HMACs scalable to faster or more secure hash functions in the future [21].

### 2.4 The RC5 Block Cipher

Ronald L. Rivest developed RC5 [17] at the MIT Laboratory for Computer Science and it is a trademark of RSA Data Security. RC5 is an extremely compact cipher and is suitable for both hardware and software implementations. Listed below are some more notable characteristics of RC5 [17]:

- RC5 is a symmetric block cipher. The same cryptographic key is used for both encryption and decryption. The ciphertext and plaintext are of fixed bit length.

- RC5 uses operations and instructions that are commonly found on typical microprocessors.

- RC5 is iterative and can have a variable number of rounds.

- RC5 uses little memory so that it is useful with smart cards, mobile computing platforms, micro controllers, and other low memory environments.

- RC5 makes use of data dependent rotations as one of its diffusion primitives.

- RC5 is parameterized as RC5 w/r/b. The word size is defined as w and the block size is 2w. The number of iterative rounds is given by τ, and b specifies the key size in bytes. For this research RC5-32/12/16 will be used.

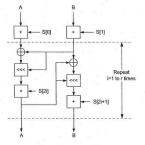

The RCS cipher is illustrated in Figure 2.5. The parameters A and B are 32bit blocks of plaintext. The array S[0.2r + 1] is composed of 32-bit words that are created by manipulation of the initial key. The + operation is mod 2<sup>32</sup> addition and L  $\ll$  R is the data dependent bit-wise left rotation of L by the amount R. To further illustrate the process of a data dependent left rotation, a simplified operation is given in Figure 2.6.

The bit-wise XOR operation is defined as  $\oplus$ . The *i* parameter is used to indicate which round the algorithm is in: for example, the statement repeat i = 1..r is the

Figure 2.5: Flow diagram of the RC5 block cipher.

| 90 (base 10) | <<< | 2 (base 10) = | 106 (base 10) |

|--------------|-----|---------------|---------------|

| 1.1          |     |               | +             |

| +            |     | +             | 1             |

| 10011010     | <<< | 00000010 =    | 01101010      |

Figure 2.6: Illustration of a simplified 8-bit left data dependent rotation.

equivalent of a loop where the variable i is incremented by one each round. Therefore in the second round of RC5, S[4] and S[5] are used in the algorithm.

### 2.5 The RC6 Block Cipher

RC6 was a submission to the National Institute of Standards and Technology (NIST) for consideration as a candidate for the Advanced Encryption Standard (AES) in 1998 (Rijudael was chosen to be the algorithm for AES [22]). RC6 was also considered for the New European Schemes for Signatures, Integrity, and Encryption (NESSIE) specification, but did not make it through to the final round of selections due to ongoing intellectual property rights issues [23]. RC6 is a direct evolution of RC5.

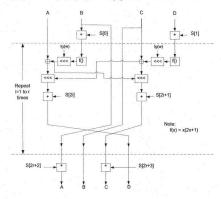

Figure 2.7: Flow diagram of the RC6 block cipher.

Since RC6 is an advancement of RC5 there are various similarities. RC6 is parameterizable like RC5 with the same parameter format, namely, RC6-w/r/b. All of the operations that are used in RC5 are also found in RC6. The operation of RC6 is shown in Figure 2.7 [18]. From the flow diagram the differences in RC6 are evident. There is a left rotation by lg(w), where lg() is the  $log_2()$  operation. The use of four w-bit input blocks of plaintext denoted as A, B, C and D make RC6 a 128-bit block cipher when w=32. There is a permutation of the data blocks at the end of each round. The biggest difference, especially from the viewpoint of performance is the operation f(), which represents the following relationship,  $f(x) = x(2x+1) \mod 2^{20}$ . Hence, f() requires an unsigned integer multiplication operation. For this research, RGG-32/20/16 will be used.

## 2.6 The MD5 Algorithm

MD5 is a cryptographic hash function that takes a message of arbitrary length and produces a 128-bit message digest. MD5 exhibits weak and strong collision avoidance, and is a popular hash algorithm that has found much use in Internet based message authentication [19].

Figure 2.8: Procedure of initial processing arbitrary length message.

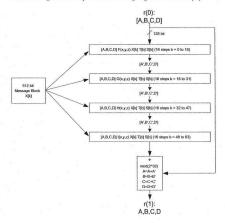

Once the message of arbitrary length has been formatted into N 512-bit blocks as shown in Figure 2.8, it is passed into the compression algorithm denoted as H.MD5. The inputs to the compression function are one 512-bit block of the formatted arbitrary length message, and four initialized registers A, B, C, and D. The outputs of the function are the modified values of the registers that were used by the input. These four registers act as temporary buffers for subsequent calls to the compression function. The values r0, r1, r2...rN - 1 are used to denote the state of the four registers before and after a call to the compression function where N - 1 would be the last call to H\_MD5. When each block of the message is processed in this fashion, the values of the registers make up the 128-bit message digest or hash value [19].

#### Figure 2.9: Looking into the H\_MD5 function.

There are 64 steps involved with the execution of H.MD5, as shown in Figure 2.9. Each grouping of 16 steps are abstracted into a block showing inputs, outputs, and data values involved. The F, G, H and I functions denote auxiliary functions that take in three 32-bit values and output a single 32-bit value. These operations are solely made up of bit-wise operations (AND, OR and XOR). The registers are re-assigned to during the execution represented by a superscript " ' ". The final operation is to add the old values of the 32-bit registers to the new modified values.

Figure 2.10: Operations involved in a single step of H\_MD5.

The array T[0.63] is an array of 32-bit values derived from the sin() function. The array S[0.63] contains values for the data dependent rotation operation. The array X[0.16] contains 32-bit words of the 512-bit message block that was passed into the compression function. The mapping of b to k is accomplished by using a permutation mod 16 operation, therefore elements of X are used and reused during the execution of H.MD5.

## 2.7 The SHA-1 Algorithm

SHA-1 [7] is a hash algorithm used in digital signature schemes and for HMACs within IPSee [24]. SHA-1 uses primitives from MD4, and there are similarities between MD5 and SHA-1. SHA-1 generates a 160-bit message digest from a message of arbitrary length [7] and this process is illustrated in Fizure 2.11.

Figure 2.11: Procedure of processing arbitrary length message.

The compression function is defined as H.SHA1. With each call to the compression function, five 32-bit registers are used as input, labeled A,B,C,D, and E. A 512-bit block of the arbitrary length message is also used as an input to the compression function. The output of the function are the five registers modified from their original values and they are used as the input to the next call to H.SHA1. Once all of the message blocks are processed the final value of the registers make up the 160-bit message (set [7].

The compressing function is decomposed in Figure 2.12. The 512-bit block is stored in the 32-bit array element W[0.13], and is expanded to a 80 element array of 32-bit values. The process of expanding W is recursive and only depends on W. There are 80 steps in total for running the compression function. The 80 steps have been further divided into groups of 20 steps. Each one of these sub-groupings is illustrated as a rectangle with input, output and other parameters listed inside. The

Figure 2.12: A decomposition of the H.SHA1 function.

functions F0, F1, F2, and F3, take as input three 32-bit values and output a single 32-bit value using bit-wise operations. The K parameter is a 32-bit constant that is used for that particular grouping of steps. The operation of the first block is further decomposed in Figure 2.13 to show the operations that take place in each step. The specific operations involved are addition, rotation, and bit-wise logical operations contained in F0 [7]. The other three groupings use F1, F2, and F3 respectively.

Figure 2.13: A decomposition of a step in the H\_SHA1 function.

For the purposes of this research it is important to look directly at the implementation of the H.SHA1 function.

# 2.8 An Example Application: The IP Security Protocol (IPSec)

The following section is an overview of how symmetric key block ciphers and hash algorithms are used in popular applications to provide general security to communications over the Internet. IPSec is the proposed standard with respect to the security architecture for the Internet protocol (IP) [25]. IPSec allows the implementation of VPNs through the establishment of secure tunnels [26]. The biggest advantage of a VPN over the Internet is that businesses can abandon private dial-in and leased communication lines in favor of using more popular public connection methods. Partners, suppliers, and customers can be seamlessly connected over a private network that is based upon a public medium [26]. IPSec will be examined in terms of how and where symmetric block ciphers and hash functions are utilized. IPSec is designed to be algorithm-independent while offering a set of required algorithms for operation on different platforms [25]. IPSec provides the following functionality to IP based networks, including the Internet [25]:

- Access Control

- Connectionless Integrity

- Data Origin Authentication

- Protection Against Replay Attacks

- Confidentiality

For the purpose of this research it is important to look at how and where IPSec is implemented. IPSec can be applied to the host level (often in software) or in conjunction with an Internet gateway or router (possibly in hardware). Three implementation possibilities arise:

- Into the native Internet Protocol (IP) implementation at the host level or at the gateway level, requiring access to IP source code [25].

- Underneath the existing IP protocol stack referred to as "Bump-in-the-stack" or BITS. Implementation is transparent to existing architecture [25].

- 3. In external hardware referred to as "Bump-in-the-wire" or BITW. BITW is often used in business and military applications and is usually IP addressable. The BITW arrangement can act as a host or a security gateway (possibly both) [25]. The BITW scheme will often require high throughput and a hardware solution.

IPScc works in either a transport mode or tunnel mode. In either case there are Security Associations (SAs) associated with each connection. In the creation of SAs there are three types of protocols that work together to provide security services: Encapsulating Security Payload (ESP), AH, and various key management protocols [26].

#### 2.8.1 Authentication Header Protocol

The role of the IP Authentication Header is to provide data origin authentication, data integrity, and protection against replay attacks. To protect against replay attacks, the receiver must check the sequence number of the incoming packets [24].

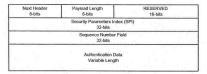

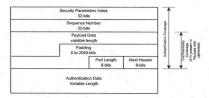

Algorithm options for the AH protocol are: HMAC MD5 or HMAC SHA-1. The protocol authenticates the entire packet with the exception of the destination address [26]. The format of the AH contains various fields as described in Figure 2.14. The field "Authentication Data" contains the computation of the Integrity Check Value (ICV). The ICV is the output of the specific HMAC algorithm used. The length of the "Authentication Data" field is variable but its length must be a multiple of 32-bits for IP version-4 or 64-bits for IP version-6 [24], while non-multiple lengths are explicitly padded [24].

Figure 2.14: AH packet format.