# EXTENSIBLE HIERARCHICAL OBJECT-ORIENTED LOGIC SIMULATION WITH AN ADAPTABLE GRAPHICAL USER INTERFACE

CENTRE FOR NEWFOUNDLAND STUDIES

## TOTAL OF 10 PAGES ONLY MAY BE XEROXED

(Without Author's Permission)

DONALD C. CRAIG

## Extensible Hierarchical Object-Oriented Logic Simulation with an Adaptable Graphical User Interface

by Donald C. Craig

A thesis submitted to the School of Graduate Studies in partial fulfillment of the requirements for the degree of Master of Science

Department of Computer Science Memorial University of Newfoundland

1996

St. John's Newfoundland

Ottawa, Ontano K1A 0N4

Acquisitions and Bibliographic Services Branch 395 Wellington Street Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques

395, rue Wellington Ottawa (Ontario) K1A QN4

Your life Value référence

Our Sin Notice of Strengte

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette la disposition des personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-612-17583-9

#### Abstract

Simulators provide an economical means of understanding and evaluating the performance of both abstract and real world systems. In addition to being efficient and easy to use, modern day simulators must be able to cope with the demands of increasing complexity within systems. Simulators must also be easily extensible so that the behaviour and performance of a wide variety of systems may be studied.

This report will outline the design and implementation of a utility which integrates an interactive, graphical design tool with a discrete event simulation engine that employs the object-oriented paradigm as a means of combating complexity. Central to the simulation technique is the concept of local time, in which each entity being simulated maintains its own notion of time throughout the simulation. This concept promotes component encapsulation and self-containment thereby facilitating the implementation of distributed event-driven simulators. Although the simulation domain described in this report will consist primarily of digital logic circuits, the simulation techniques should also be amenable to the simulation of any discrete event system.

The graphical user interface front-end to the simulator engine is designed to be easy to use, hence making the underlying simulator engine accessible to a wide audience. The implementation of the interface is loosely integrated with the simulator engine, thereby providing a high degree flexibility between the interface and the simulator itself. The interface and the simulator can each operate as distinct, self-contained applications. As a result, the simulator engine could be configured to employ a different graphical interface and the graphical interface can be adapted for a variety of existing text-based simulator engines.

#### Acknowledgements

Once again, I would like to thank my supervisor. Dr. Paul Gillard, for his patience and support over the past three years and for continuing as my supervisor during his sabbatical. His enlightening discussions and flexible style made my graduate program both educational and enjoyable.

I am indebted to the Natural Sciences and Engineering Research Council (NSERC) for their generous financial support during the first two years of my graduate program.

I would also like to thank both Mrs. June Poltz and Dr. Wlodek Zuberek for formally approving my admission to Graduate School. In addition, I'd like to thank Dr. Zuberek for gently (but firmly) reminding me of my academic responsibilities after I had resumed full-time employment outside the University prior to the completion of my thesis. His encouragement contributed to the timely completion of this report.

Thanks also go to several other members of the Department of Computer Science, including Dr. Rodrigue Byrne who made several suggestions for improving an earlier version of the implementation and Miss Flaine Boone, whose proofreading skills helped eliminate several typographical and grammatical errors in an earlier draft of this thesis. Of course, I take full responsibility for any mistakes or oversights remaining in this report.

Finally, I would like to express my gratitude to the thousands of individuals responsible for the development and distribution of robust and inexpensive software tools. Freely available operating systems and software packages such as Linux, XFree86, Tcl/Tk, \(\mathbb{U}\)\(\mathbb{E}\)\(\mathbb{X}\), the GNU C++ compiler and related tools contributed significantly to the successful completion of this project.

## Contents

| A  | bstra | ict    |                                      | ii  |

|----|-------|--------|--------------------------------------|-----|

| A  | ckno  | wledge | ements                               | iii |

| Li | st of | Table  | s                                    | x   |

| Li | st of | Figur  | es                                   | хi  |

| 1  | Int   | roduct | ion                                  | 1   |

|    | 1.1   | The N  | Reed for Simulation                  | 3   |

|    |       | 1.1.1  | Advantages of Simulation             | 4   |

|    |       | 1.1.2  | Disadvantages of Simulation          | 6   |

|    | 1.2   | Classi | fication of Simulation Systems       | 8   |

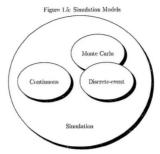

|    | 1.3   | Simul  | ation Models                         | 9   |

|    |       | 1.3.1  | Continuous Simulation                | 9   |

|    |       | 1.3.2  | Discrete-Event Simulation            | 11  |

|    | 1.4   | Abstra | action Levels for Circuit Simulation | 14  |

|    |       | 1.4.1  | Circuit-level Simulators             | 15  |

|    |       | 1.4.2  | Logic-level Simulators               | 16  |

|   |     | THE ANNUAL PLANT CO. LEWIS CO., LAND |      |

|---|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|   |     | 1.4.3 Functional- and Behavioural-level Simulators                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 17   |

|   | 1.5 | The Purpose of this Report                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 19   |

| 2 | The | Simulator User Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 20   |

|   | 2.1 | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 20   |

|   | 2.2 | GUI Platform and Implementation Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 22   |

|   |     | 2.2.1 GUI Platform                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 22   |

|   |     | 2.2.2 Implementation Language                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 23   |

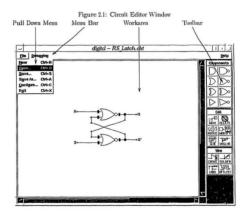

|   | 2.3 | Overview of the Simulator GUI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 28   |

|   |     | 2.3.1 Circuit Editor Window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 28   |

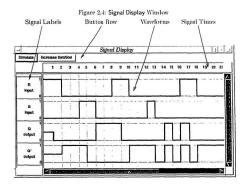

|   |     | 2.3.2 Signal Display Window                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 38   |

|   | 2.4 | Configuration Options and Resource Database                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | -11  |

|   | 2.5 | GUI Limitations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | -1-1 |

| 3 | GU  | I Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 46   |

|   | 3.1 | Overview of the Implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -16  |

|   | 3.2 | Pull-Down Menu Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | -19  |

|   | 3.3 | Toolbar Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 51   |

|   | 3.4 | Workarea Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 54   |

|   | 3.5 | Component Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 57   |

|   |     | 3.5.1 Component Creation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 57   |

|   |     | 3.5.2 Component Representation Arrays                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 61   |

|   |     | 3.5.3 Component Manipulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 62   |

|   | 3.6 | Netlist Modules                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 65   |

|   |     | 3.6.1 Netlist Creation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 66   |

|      | 5.0.2 Sectise representation Arrays                                   | UC  |

|------|-----------------------------------------------------------------------|-----|

|      | 3.6.3 Netlist Manipulation                                            | 70  |

| 3.7  | Multibox Modules                                                      | 81  |

| 3.8  | Signal Display Modules                                                | 8-  |

| 3.9  | Miscellaneous Modules                                                 | 87  |

| 3.10 | Simulation                                                            | 88  |

| Sin  | nulator Engine                                                        | 89  |

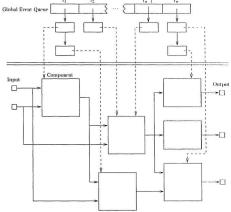

| 4.1  | Simulation Using a Global Event Queue                                 | 90  |

|      | 4.1.1 Drawbacks of the Global Event Queue                             | 91  |

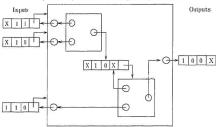

| 4.2  | Object-Oriented Approach Towards Simulation                           | 98  |

|      | 4.2.1 Examples of Digital Simulator Designs                           | 98  |

| 4.3  | An Alternative Approach Towards Simulation                            | 97  |

|      | 4.3.1 The Concept of Local Time                                       | 98  |

|      | 4.3.2 Distributed Event Queues                                        | 99  |

|      | 4.3.3 Circuit Classification and Representation                       | 101 |

|      | 4.3.4 Class Design                                                    | 104 |

|      | 4.3.5 The Simulation Algorithm                                        | 118 |

| Sys  | tem Integration                                                       | 119 |

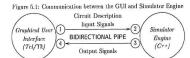

| 5.1  | System Integration Techniques                                         | 119 |

|      | 5.1.1 Integrating Modules Using Command Pipelines $\ \ldots \ \ldots$ | 121 |

| 5.2  | Advantages of Using Command Pipelines                                 | 123 |

| 5.3  | Overview of the Interaction Protocols                                 | 126 |

|      | 5.3.1 The Component Protocol                                          | 127 |

5

|    |       | 5.3.2 The Netlist Protocol                    | 128 |

|----|-------|-----------------------------------------------|-----|

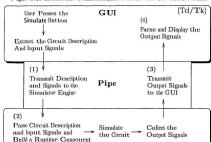

|    | 5.4   | Implementation of the System Integration      | 130 |

|    |       | 5.4.1 Step 1: GUI Protocol Transmission       | 130 |

|    |       | 5.4.2 Step 2: Simulator Protocol Reception    | 133 |

|    |       | 5.4.3 Step 3: Simulator Protocol Transmission | 135 |

|    |       | 5.4.4 Step 4: GUI Protocol Reception          | 138 |

| 6  | Cor   | clusions                                      | 140 |

|    | 6.1   | Application and Future Work                   | ы   |

| Bi | bligi | aphy                                          | 145 |

| A  | Inst  | allation Guide                                | 150 |

|    | A.1   | Extracting the Archive File                   | 151 |

|    | A.2   | Compiling the Simulator Engine                | 151 |

|    | A.3   | Environment Variables                         | 152 |

|    | A.4   | Running the DigiTcl Circuit Editor            | 15: |

| В  | Circ  | uit File Format                               | 155 |

|    | B.1   | The component Stanza                          | 150 |

|    | B.2   | The point Stanza                              | 157 |

|    | B.3   | The label Stanza                              | 158 |

| C  | Sim   | ulator Engine Class Dictionary                | 160 |

|    | C.1   | The Component Class                           | 16  |

|    |       | C.1.1 Public Members                          | 16  |

|      | C.1.2  | Protected Members    |     |  |  |  |   |  |  |  |  |  |  |    |   | 163 |

|------|--------|----------------------|-----|--|--|--|---|--|--|--|--|--|--|----|---|-----|

|      | C.1.3  | Private Members .    |     |  |  |  |   |  |  |  |  |  |  |    | • | 163 |

| C.2  | The C  | onnector Class       |     |  |  |  |   |  |  |  |  |  |  |    |   | 164 |

|      | C.2.1  | Public Members       |     |  |  |  |   |  |  |  |  |  |  | į. |   | 165 |

|      | C.2.2  | Protected Members    |     |  |  |  |   |  |  |  |  |  |  |    |   | 100 |

|      | C.2.3  | Private Members .    |     |  |  |  |   |  |  |  |  |  |  |    |   | 166 |

| C.3  | The V  | fire Class           |     |  |  |  |   |  |  |  |  |  |  |    |   | 166 |

|      | C.3.1  | Public Members       |     |  |  |  |   |  |  |  |  |  |  |    |   | 167 |

|      | C.3.2  | Protected Members    |     |  |  |  |   |  |  |  |  |  |  |    |   | 168 |

|      | C.3.3  | Private Members .    |     |  |  |  |   |  |  |  |  |  |  |    |   | 168 |

| C. ' | The P  | ort Class            |     |  |  |  | × |  |  |  |  |  |  | ٠  |   | 168 |

|      | C.4.1  | Public Members       |     |  |  |  |   |  |  |  |  |  |  |    |   | 169 |

|      | C.4.2  | Protected Members    |     |  |  |  |   |  |  |  |  |  |  |    |   | 170 |

|      | C.4.3  | Private Members .    |     |  |  |  |   |  |  |  |  |  |  |    |   | 170 |

| C.5  | The In | put Class            |     |  |  |  |   |  |  |  |  |  |  |    |   | 170 |

|      | C.5.1  | Public Members       |     |  |  |  |   |  |  |  |  |  |  |    |   | 171 |

|      | C.5.2  | Protected Members    |     |  |  |  |   |  |  |  |  |  |  |    |   | 171 |

|      | C.5.3  | Private Members .    |     |  |  |  |   |  |  |  |  |  |  |    |   | 172 |

| C.6  | The O  | utput Class          |     |  |  |  |   |  |  |  |  |  |  |    |   | 172 |

|      | C.6.1  | Public Members       |     |  |  |  |   |  |  |  |  |  |  |    |   | 172 |

|      | C.6.2  | Protected Members    |     |  |  |  |   |  |  |  |  |  |  |    |   | 173 |

|      | C.6.3  | Private Members .    |     |  |  |  |   |  |  |  |  |  |  |    |   | 173 |

| C.7  | The R  | untime_Component Cla | ass |  |  |  |   |  |  |  |  |  |  |    |   | 173 |

|      | C.7.1  | Public Members       |     |  |  |  |   |  |  |  |  |  |  |    |   | 173 |

|      | C.7.2  | Protected Members |  |  |  |  |  |  |   |  |  |  |  |   | 175 |

|------|--------|-------------------|--|--|--|--|--|--|---|--|--|--|--|---|-----|

|      | C.7.3  | Private Members . |  |  |  |  |  |  | ٠ |  |  |  |  | ٠ | 175 |

| C.8  | The P  | arser Class       |  |  |  |  |  |  |   |  |  |  |  |   | 175 |

|      | C.8.1  | Public Members    |  |  |  |  |  |  |   |  |  |  |  |   | 176 |

|      | C.8.2  | Protected Members |  |  |  |  |  |  |   |  |  |  |  |   | 177 |

|      | C.8.3  | Private Members . |  |  |  |  |  |  |   |  |  |  |  |   | 178 |

| C.9  | The S  | ignal Class       |  |  |  |  |  |  |   |  |  |  |  |   | 180 |

|      | C.9.1  | Public Members    |  |  |  |  |  |  |   |  |  |  |  |   | 180 |

|      | C.9.2  | Protected Members |  |  |  |  |  |  |   |  |  |  |  |   | 181 |

|      | C.9.3  | Private Members . |  |  |  |  |  |  |   |  |  |  |  |   | 181 |

| C.10 | The L  | ist Class         |  |  |  |  |  |  |   |  |  |  |  |   | 181 |

|      | C.10.1 | Public Members    |  |  |  |  |  |  |   |  |  |  |  |   | 182 |

|      | C.10.2 | Protected Members |  |  |  |  |  |  |   |  |  |  |  |   | 182 |

|      | C.10.3 | Private Members . |  |  |  |  |  |  |   |  |  |  |  |   | 183 |

## List of Tables

| 3.1  | Pull-down Menu Module Responsibilities           | 0   |

|------|--------------------------------------------------|-----|

| 3.2  | Toolbar Module Responsibilities                  | 2   |

| 3.3  | High-level Workarea Modules                      | 1-1 |

| 3.4  | Component Creation and Manipulation Modules      | 8   |

| 3.5  | Netlist Creation and Manipulation Modules        | 5   |

| 3.6  | Netlist Representation Arrays                    | 9   |

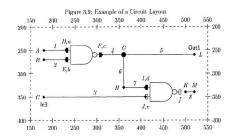

| 3.7  | Point Tags for the Circuit in Figure 3.9         | 1   |

| 3.8  | Wire Tags for the Circuit in Figure 3.9          | 2   |

| 3.9  | Point Array Values for the Circuit in Figure 3.9 | 3   |

| 3.10 | Net Array Values for the Circuit in Figure 3.9   | 5   |

| 3.11 | Multibox Creation and Manipulation Modules       | 2   |

| 3.12 | Signal Display Modules                           | 4   |

| 3.13 | Miscellaneous Module Responsibilities            | 7   |

| A.1  | Files Included in the DigiTcl Distribution       | 1   |

| 1.2  | Environment Variables Used by Tcl/Tk             | 2   |

| A.3  | Environment Variables Used by DigiTcl            | 3   |

|      |                                                  |     |

## List of Figures

| 1.1 | Depletion Mode Transistor Pulling Up Capacitive Load |

|-----|------------------------------------------------------|

| 1.2 | Graph Representing Continuous Behaviour              |

| 1.3 | Simple Digital Logic Circuit                         |

| 1.4 | Graph Representing Discrete Behaviour                |

| 1.5 | Simulation Models                                    |

| 2.1 | Circuit Editor Window                                |

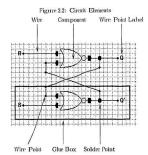

| 2.2 | Circuit Elements                                     |

| 2.3 | Netlist Label Dialog Box                             |

| 2.4 | Signal Display Window                                |

| 2.5 | Configure Dialog Box                                 |

| 3.1 | Modularization of the GUI Source                     |

| 3.2 | Invoking the pullmenu_create Procedure 5             |

| 3.3 | The tb_buttons Associative Array                     |

| 3.4 | Establishing Canvas Bindings in tb_set_bindings      |

| 3.5 | Creating Structured Graphics on a Canvas             |

| 3.6 | Primitive Composition of a NAND Gate                 |

| 3.7  | Tel Code to Build a NAND Gate                               | 6   |

|------|-------------------------------------------------------------|-----|

| 3.8  | Rotation Equations for Canvas Primitives                    | 6   |

| 3.9  | Example of a Circuit Layout                                 | 71  |

| 3.10 | Splitting a Netlist                                         | 7   |

| 3.11 | Traversing and Retagging a Netlist                          | 7!  |

| 3.12 | Source Code Uniting Two Netlists                            | 81  |

| 4.1  | Digital Simulation Using a Global Event Queue               | 93  |

| 4.2  | System Overview of a Hierarchical Simulator                 | 9   |

| 4.3  | Digital Simulation Using Distributed Event Queues           | 100 |

| 4.4  | Representation of a Simple Composite Circuit                | 103 |

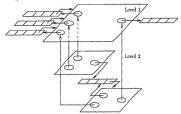

| 1.5  | Three-dimensional Hierarchical Circuit Representation       | 10  |

| 1.6  | Component Class Diagram                                     | 107 |

| 1.7  | Connector Class Diagram                                     | 11  |

| 1.8  | Sending a signal to a Port                                  | 11- |

| 1.9  | Sending a signal to a Wire                                  | 114 |

| 1.10 | Class diagram of a 3-input AND gate                         | 115 |

| 5.1  | Communication between the GUI and Simulator Engine          | 121 |

| 5.2  | Tel Script Opening a Pipe to an Executable                  | 122 |

| 5.3  | The C++ Program addnum                                      | 123 |

| 5.4  | A 2-input $NAND$ Gate and its Corresponding Protocol Stanza | 128 |

| 5.5  | Intermodule Communication Between the GUI and Simulator     | 131 |

| 5.6  | Example of a Circuit                                        | 132 |

| 5.7  | Example of Input Signal Waveforms                           | 132 |

| 5.8  | Protocol for the Circuit and Inputs in Figure 5.6 and Figure 5.7 $$ | 133 |

|------|---------------------------------------------------------------------|-----|

| 5.9  | The main() Function of the Simulator Module                         | 135 |

| 5.10 | The show_signals() Member Function of the Wire Class                | 136 |

| 5.11 | The display_signals() Member Function of the Wire Class             | 137 |

| 5.12 | Sample Protocol for an Output Signal Waveform                       | 137 |

| 5.13 | Output Signal Waveform Displayed Graphically                        | 138 |

| B.1  | Example of a component Stanza                                       | 157 |

| B.2  | Example of a point Stanza                                           | 158 |

| B.3  | Example of a label Stanza                                           | 159 |

### Chapter 1

#### Introduction

Advances in technology invariably lead to the construction of systems with additional layers of complexity being wrapped around more primitive but equally complex subsystems. In the future, these systems may then, in turn, become sub-systems of larger, even more complex, super-systems. Simulators provide a means by which such abstract and real world systems may be understood and evaluated by duplicating the behaviour of these systems through hardware and software. Formally, we can define simulation as

"... the process of designing a model of a real system and conducting experiments with this model for the purpose either of understanding the behaviour of the system of or evaluating various strategies (within the limits imposed by a criterion or a set of criteria) for the operation of the system." [261]

Simulators must adapt to increases in system complexity by permitting users to simulate a system at several conceptual levels. Unfortunately, the design and implementation of simulators is almost as complex as the systems being simulated. As a result, there has been a concerted effort by the software community to apply the latest advancements in software technology in an attempt to counteract this ever increasing complexity. Their efforts have lead to simulators which are easy to maintain and extend while at the same time preserving their relative efficiency. The prominent paradigm currently being used to implement simulators is the ubiquitous object-oriental [3] paradigm, in which software entities closely model their real world counterparts. This paradigm has been successfully employed to implement a wide variety of simulators ranging from samulil production [22] to air base logistics [20].

This thesis represents a major enhancement to an existing discrete-event simulation engine [7] which employs distributed event queues as its primary nechanism for event management instead of the more commonly used global event queue. By adopting a concept of local time, it will be shown how the global event queue may be replaced by several distributed queues, each of which are self contained within a simulation component. The system being simulated can then be decomposed hierarchically into several such components thereby promoting extensibility and modularity of the simulation system. Details will also be provided regarding how this simulation technique addresses the need for extensibility and how the simulation entities may be reused from system to system so as to avoid needless duplication of effort when constructing a new system. The advantages and disadvantages of using a global queue versus distributed queues will be discussed as the two simulation techniques are compared from a design, implementation and philosophical perspective.

In addition to describing and comparing the two simulation strategies described above, this report will also discuss the design and implementation issues associated with providing the simulator engines with a graphical user interface. Such an interface can be used to layout and connect the simulation entities, observe the dynamics of the system during simulation and collect various reports upon completion of the simulation for verification or performance evaluation. The ability to observe the dynamic interaction between components makes the simulator an ideal tool for understanding subtle aspects of a particular design or to teach novice designers the fundamental behaviour of elementary systems.

Before presenting details about the design and implementation of a distributed queue simulator, this chapter will provide a general overview of simulation. The need for simulators will be explained as will the potential problems that may arise through their imprudent use. After discussing some different simulation models, a few practical uses of simulators will be described.

#### 1.1 The Need for Simulation

A simulator is a collection of hardware and software systems which are used to mimic

the behaviour of some entity or phenomenon. Typically, the entity or phenomenon

being simulated is from the domain of the tangible—ranging from the operation of

integrated circuits to behaviour of a light aircraft during wind sheer. Simulators may

also be used to analyze and verify theoretical models which may be too difficult to

grasp from a purely conceptual level. Such phenomenon range from examination of

black holes to the study of highly abstract models of computation. As such, simulators

provide a crucial role in both industry and academia.

Despite the increasing recognition of simulators as a viable and necessary research

tool, one must constantly be aware of the potential problems which simulators may

introduce. Many of the problems are related to the computational limitations of ex-

isting hardware platforms but are quickly being overcome as more powerful platforms are introduced. Other problems, unfortunately, are inherent within simulators and are related to the complexity associated with the systems being simulated. This section highlights some of the major advantages and disadvantages posed by modern day simulators.

One of the primary advantages of simulators is that they are able to provide users

#### 1.1.1 Advantages of Simulation

with practical feedback when designing real world systems. This allows the designer to determine the correctness and efficiency of a design before the system is actually constructed. Consequently, the user may explore the morits of alternative designs without actually physically building the systems. By investigating the effects of specific design decisions during the design phase rather than the construction phase, the overall rost of building the system diminishes significantly. As an example, consider the design and fabrication of integrated circuits. During the design phase, the designer is presented with a myrind of decisions regarding such things as the placement of components and the routing of the connecting wires. It would be very costly to actually fabricate all of the potential designs as a means of evaluating their respective performance. Through the use of a simulator, however, the user may investigate the relative superiority of each design without actually fabricating the circuits themselves. By mimicking the behaviour of the designs, the circuit simulator is able to provide the designer with information pertaining to the correctness and efficiency of alternate designs. After carefully weighing the ramifications of each design, the best circuit

may then be fabricated.

Another benefit of simulators is that they permit system designers to study a problem at several different levels of abstraction. By approaching a system at a higher level of abstraction, the designer is better able to understand the behaviours and interactions of all the high level components within the system and is therefore better equipped to counteract the complexity of the overall system. This complexity may simply overwhelm the designer if the problem had been approached from a lower level. As the designer better understands the operation of the higher level components through the use of the simulator, the lower level components may then be designed and subsequently simulated for verification and performance evaluation. The entire system may be built based upon this "top-down" technique. This approach is often referred to as hierarchical decomposition [32] and is essential in any design tool and simulator which deals with the construction of complex systems. For example, with respect to circuits, it is often useful to think of a microprocessor in terms of its registers, arithmetic logic units, multiplexors and control units. A simulator which permits the construction, interconnection and subsequent simulation of these higher level entities is much more useful than a simulator which only lets the designer build and connect simple logic gates. Working at a higher level abstraction also facilitates rapid prototyping in which preliminary systems are designed quickly for the purpose of studying the feasibility and practicality of the high-level design.

Thirdly, simulators can be used as an effective means for teaching or demonstrating concepts to students. This is particularly true of simulators that make intelligent use of computer graphics and animation. Such simulators dynamically show the behaviour and relationship of all the simulated system's components, thereby providing the user

with a meaningful understanding of the system's nature. Consider again, for example, a circuit simulator. By showing the paths taken by signals as inputs are consumed by components and outputs are produced over their respective famout, the student can actually see what is happening within the circuit and is therefore left with a better understanding for the dynamics of the circuit. Such a simulator should also permit students to speed up, slow down, stop or even reverse a simulation as a means of aiding understanding. This is particularly true when simulating circuits which contain feedback loops or other operations which are not immediately intuitive upon an initial investigation.

During the presentation of the design and implementation of the simulator in this report, it will be shown how the above positive attributes have been or can be incorporated both in the simulator engine and its user interface.

#### 1.1.2 Disadvantages of Simulation

Despite the advantages of simulation presented above, simulators, like most tools, do have their drawbacks. Many of these problems can be attributed to the computationally intensive processing required by some simulators. As a consequence, the results of the simulation may not be readily available after the simulation has started—an event that may occur instantaneously in the real world may actually take hours to mimic in a simulated environment. The delays may be due to an exceedingly large number of entities being simulated or due to the complex interactions that occur between the entities within the system being simulated. Consequently, these simulators are restricted by limited hardware platforms which cannot meet the