# EXPLORING LINEAR SPEEDUP IN PARALLEL ATPG THROUGH SPECIAL TOPOLOGY

CENTRE FOR NEWFOUNDLAND STUDIES

## TOTAL OF 10 PAGES ONLY MAY BE XEROXED

(Without Author's Permission)

National Library of Canada

Acquisitions and Bibliographic Services Branch 395 Wellington Street Ottawa, Onland K1A 0N4 Bibliothèque nationale du Canada

Direction des acquisitions et des services bibliographiques 395, rue Wollington Ottawa (Ontario) KTA 0N4

harbe litterstome

the Morgeone

#### NOTICE

The quality of this microform is heavily dependent upon the quality of the original thesis submitted for microfilming. Every effort has been made to ensure the highest quality of reproduction possible.

If pages are missing, contact the university which granted the degree.

Some pages may have indistinct print especially if the original pages were typed with a poor typewriter ribbon or if the university sent us an inferior photocopy.

Reproduction in full or in part of this microform is governed by the Canadian Copyright Act, R.S.C. 1970, c. C-30, and subsequent amendments.

#### AVIS

La qualité de cette microforme dépend grandement de la qualité de la thèse soumise au microfilmage. Nous avons tout fait pour assurer une qualité supérieure de reproduction.

S'il manque des pages, veuillez communiquer avec l'université qui a conféré le grade.

La qualité d'impression de certaines pages peut laisser à désirer, surtout si les pages originales ont été dactylographiées à l'aide d'un ruban usé ou si l'université nous a fait parvenir une photocopie de qualité inférieure.

La reproduction, même partielle, de cette microforme est soumise à la Loi canadienne sur le droit d'auteur, SRC 1970, c. C-30, et ses amendements subséquents.

# Canadä

# Exploring Linear Speedup in Parallel ATPG Through Special Topology

By Zhimin Shi, BSc.

A thesis submitted to the School of Graduate

Studies in partial fulfillment of the

requirements for the degree of

Master of Science

Department of Computer Science Memorial University of Newfoundland March 12, 1994 National Library of Canada

Bibliothèque nationale du Canada

Acquisitions and Bibliographic Services Branch 395 Wetington Street Ottawa, Onlario K1A 0N4 Direction des acquisitions et des services bibliographiques 395, ruo Wellington Ottawa (Ontario) K14 ON4

tourse someoppiere

Charles Alston rettings in

The author has granted an irrevocable non-exclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of his/her thesis by any means and in any form or format, making this thesis available to interested persons.

L'auteur a accordé une licence irrévocable et non exclusive permettant à la Bibliothèque nationale du Canada de reproduire, prêter, distribuer ou vendre des copies de sa thèse de quelque manière et sous quelque forme que ce soit pour mettre des exemplaires de cette thèse à la disposition des personnes intéressées.

The author retains ownership of the copyright in his/her thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without his/her permission. L'auteur conserve la propriété du droit d'auteur qui protège sa thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

ISBN 0-315-91620-6

#### Abstract

In digital system design, test pattern generation requires a considerable amount of computing time. Using a level-sensitive scan design, test pattern generation can be confined to the combinational circuits. It has been shown that the problem of test pattern generation for combinational circuits is NP-complete. Although many excellent algorithms have been developed to generate test patterns, they still do not keep pace with VLSI technology. Research is ongoing in the development of parallel processing techniques for test pattern generation, but there has been little research into what kind of topology has the greatest potential to speed up test pattern generation.

In this work, simulation software was developed for measurement of the speedup, and three topologies are proposed to explore the parallelism for automatic test pattern generation. These topologies are: modified complete binary tree (MCBTA), autonomous modified complete binary tree (AMCBTA), and square array structure (SQARRAY). The empirical results for these topologies show that a special topology has the potential capability to speed up test pattern generation and super-linear speedup can often result if an autonomous structure is adopted.

### Acknowledgements

I wish to express my thanks to my supervisor Dr. Paul Gillard for his guidance, interest, constructive criticism and enthusiasm. Without his contribution, it would be impossible to give this thesis its current quality.

I would like to thank the systems support staff for providing help and assistance while I conducted this research.

I am also very grateful to the Administrative staff who have helped in one way or another in the preparation of this thesis.

In addition, I would like to acknowledge the financial support received from the Department of Computer Science and the School of Graduate Studies.

Special thanks are due to my fellow graduate students and good friends, and in particular to Zhengqi Lu, Xu He, Sun Yongmei, and Chen Hao for their valuable comments and useful suggestions. I would also like to thank Dr. Siwei Lu, Patricia Murphy and Elaine Boone for their help and assistance. This thesis is dedicated to

my wife. Zhang Min

and my parents

for their support and encouragement throughout

the course of my education

## Contents

Introduction

| ı | Intr | oduction                               | 2  |

|---|------|----------------------------------------|----|

| 2 | Con  | ventional ATPG Algorithms              | 6  |

|   | 2.1  | Stuck-at Fault Model & Testing Problem | 6  |

|   |      | 2.1.1 Stuck-at Fault Model             | 6  |

|   |      | 2.1.2 Testing Problems                 | 8  |

|   | 2.2  | D-algorithm                            | 10 |

|   | 2.3  | PODEM Algorithm                        | 14 |

|   | 2.4  | FAN Algorithm                          | 16 |

| 3 | 'Tax | onomy of Parallel ATPG Algorithms      | 19 |

|   | 3.1  | Fault Partitioning                     | 19 |

|   | 3.2  | Heuristic Parallelization              | 21 |

|   | 3.3  | Search-space Partitioning              | 23 |

|   | 3.4  | Functional (algorithmic) Partitioning  | 25 |

|   | 3.5  | Topological Partitioning               | 27 |

|   | Har  | d-to-detect Faults                     | 29 |

|    | 4.1 | Data from Experiments                       | 29 |

|----|-----|---------------------------------------------|----|

|    | 4.2 | Inference from Experiments                  | 31 |

| II | S   | imulation Environment                       | 33 |

|    |     |                                             |    |

| 5  | Mod | del for Measurement                         | 34 |

|    | 5.1 | Model for Measurement                       | 34 |

|    | 5.2 | Parallel Speedup in Test Pattern Generation | 37 |

| 6  | Alg | orithms                                     | 44 |

|    | 6.1 | Parser Construction                         | 44 |

|    |     | 6.1.1 The Grammar Rules                     | 44 |

|    | 6.2 | Compiler Driven Simulation                  | 48 |

|    | 6.3 | Checking Trial Test Patterns                | 54 |

|    | 6.4 | Heuristics                                  | 56 |

|    | 6.5 | Expansion of Trial Test Patterns            | GO |

|    | 6.6 | Detection of Redundant Faults               | 62 |

| 11 | I.  | ATPG and 4 Connected Architecture           | 64 |

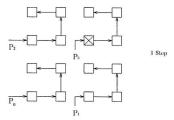

| 7  | Fou | r Connected Topology                        | 65 |

|    | 7.1 | 4 Connected Structure and Examples          | 65 |

|    | 7.2 | Characteristics of 4 Connected Topology     | 68 |

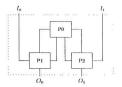

|    |     | 7.2.1 4CS naturally supports parallel ATPG  | 68 |

|    |     | 7.2.2 Isomorphic 4CS systems                | 69 |

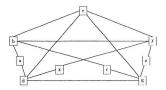

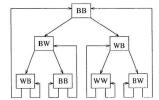

| 8 | AT  | PG Us | sing MCBTA                             | 74 |

|---|-----|-------|----------------------------------------|----|

|   | 8.1 | MCB   | TA Architecture and Parallel Algorithm | 74 |

|   |     | 8.1.1 | Architecture and Algorithm             | 74 |

|   |     | 8.1.2 | Empirical Results and Analysis         | 84 |

|   | 8.2 | Autor | omous MCBTA Architecture               | 86 |

|   |     | 8.2.1 | Architecture                           | 86 |

|   |     | 8.2.2 | Λ Parallel Algorithm                   | 87 |

|   |     | 8.2.3 | Empirical Results and Analysis         | 88 |

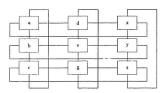

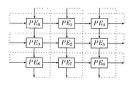

| 9 | ΛT  | PG Us | ing Square Array                       | 93 |

|   | 9.1 | Squar | e Array and Its Parallel Algorithm     | 93 |

|   |     | 9.1.1 | Square Array Architecture              | 93 |

|   |     | 9.1.2 | Completeness of Square Array           | 95 |

|   |     | 9.1.3 | A Parallel Algorithm                   | 96 |

|   |     | 9.1.4 | Empirical Results and Analysis         | 96 |

|   |     |       |                                        |    |

| I | J   | Conc  | lusion and Discussion 10               | 01 |

# List of Tables

| 2.1 | Test Cubes for Justification First          |     | ٠ |  | ٠ |   |   | ٠ |   | 1 |

|-----|---------------------------------------------|-----|---|--|---|---|---|---|---|---|

| 2.2 | Test Cubes for Propagation First            |     |   |  |   | ٠ |   |   |   | 1 |

| 3.1 | Summary of Fault Partitioning               |     | • |  |   |   |   |   |   | 2 |

| 3.2 | Summary of Heuristic Parallelization        |     | ٠ |  |   |   |   |   |   | 2 |

| 3.3 | Summary of Search Space Partitioning .      |     |   |  |   |   |   |   |   | 2 |

| 3.4 | Summary of Algorithmic Partitioning         |     |   |  |   |   |   |   |   | 2 |

| 3.5 | Summary of Topological Partitioning $$ . $$ |     |   |  |   |   |   |   |   | 2 |

| 4.1 | Statistical Data for Circuits               |     |   |  | ٠ |   |   |   | - | 3 |

| 5.1 | A Process of the Proof of a Redundant Fa    | ult |   |  |   |   |   |   |   | 4 |

| 5.2 | A Process of the Proof of a Redundant Fa    | nlt |   |  |   |   | d |   |   | 4 |

# List of Figures

|     | A Official for D-augorithm                 |    |

|-----|--------------------------------------------|----|

| .2  | A Podem Example                            | 14 |

| .3  | Podem Search Space Diagram                 | 16 |

| .4  | A Fan Example                              | 17 |

| .1  | Virtual 2 Phase Clock                      | 35 |

| .2  | One Processor Searches 16 Elements         | 39 |

| .3  | 4 Processors Search 16 Elements            | 40 |

| .4  | A Circuit with One Fault                   | 41 |

| . 1 | Ineffective Logic Gates                    | 53 |

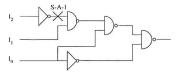

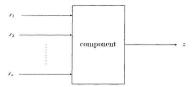

| .2  | Diagram for a Component                    | 57 |

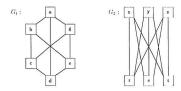

| .1  | The Diagram for Graph in Example 1         | 67 |

| .2  | The Diagram for Graph in Example 2         | 67 |

| .3  | Two Isomorphic Graphs                      | 70 |

| .4  | A Non-planar 4-connected Graph             | 71 |

| .5  | A Subdivision of K <sub>5</sub>            | 72 |

| ij. | Complete Binary Tree Architecture          | 75 |

| .2  | Modified Complete Binary Tree Architecture | 77 |

|     |                                            |    |

19

| 8.3  | Dayout of MCB1A using 11-tree                             | 11  |

|------|-----------------------------------------------------------|-----|

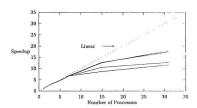

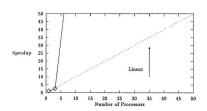

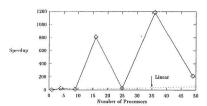

| 8.4  | Speedup for 4 Redundant Faults in MCBTA                   | 85  |

| 8.5  | Speedup for an Irredundant Hard-to-detect Fault in MCBTA  | 85  |

| 8.6  | A Pure MCBTA                                              | 87  |

| 8.7  | Autonomous MCBTA                                          | 88  |

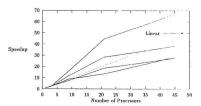

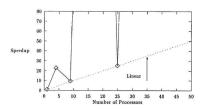

| 8.8  | Speedup for 4 Redundant Faults in AMCBTA                  | 89  |

| 8.9  | Speedup for an Irredundant Hard-to-detect Fault in AMCBTA | 90  |

| 8.10 | Scaled Diagram for Figure 8.9                             | 9(  |

| 8.11 | Experiment With 1 Module                                  | 91  |

| 8.12 | Experiment With 7 Modules                                 | 91  |

| 8.13 | Experiment With 15 Modules                                | 91  |

| 9.1  | The Symbol for a Processor in SQARRAY                     | 94  |

| 9.2  | SQARRAY with 9 Processors                                 | 9   |

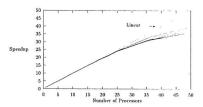

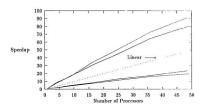

| 9.3  | Speedup for 4 Redundant Faults in SQARRAY                 | 91  |

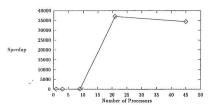

| 9.4  | Speedup for an Irredundant Fault in SQARRAY               | 917 |

| 9.5  | Scaled Speedup for the Irredundant Fault in SQARRAY       | 91  |

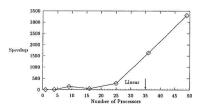

| 9.6  | Speedup in Complementary SQARRAY (4 redundant faults)     | 99  |

| 9.7  | Speedup in Complementary SQARRAY (an irredundant fault)   | 10  |

# $\mathbf{PartI}$

# Introduction

## Chapter 1

### Introduction

Generating test patterns for testing digital circuits is a very important aspect of VLSI design. It often consumes a significant portion of the design time. Owing to techniques such as the widely used level-sensitive scan design[5], the problem of test pattern generation is reduced to the problem of generating test patterns for combinational circuits. Even this problem has been shown to be NP complete[17].

There are two basic approaches to solve the automatic test pattern generation (ATPG) problem: algorithmic test pattern generation and statistical, or r cudorandom, test pattern generation. In the algorithmic approach, a specific ATPG algorithm is used to generate a test for each fault in the circuit. Most of these algorithms can be proved to be complete; that is, they are guaranteed to find a test for a fault — as long as a test exists. However, this may involve searching the entire solution space, which is computationally expensive.

Statistical test pattern generation, on the other hand, selects test patterns at random, or by using some heuristic, and uses fault simulation to determine the faults detected by the pattern. Test patterns are selected and added to the test set if they detect any previously undetected faults, until some required fault.

coverage measure or computation time limit is reached. This method finds tests for the easy-to-detect faults quickly but becomes less and less efficient as the easy-to-detect faults are removed from the fault list and only the hard-to-detect faults remain. In many cases, the required fault coverage cannot be achieved without excessive computation times.

An efficient combined method for solving the ATPG problem uses statistical methods to find tests for the easy-to-detect faults on the fault list and switches to an algorithmic method to find tests for the remaining hard-to-detect faults. In either the combined or the purely algorithmic method, a significant portion of the computation time will be spent generating tests for the hard-to-detect faults algorithmically. Therefore, finding a method to speed up this process should reduce the overall computation time considerably.

Much research has gone into increasing the efficiency of algorithms for ATPG. However, the overall geins achieved through these improvements have not kept pace with increasing circuit size, and computation time is still excessive. Another approach to reducing computation time is simply to use a faster machine. Parallel-processing machines are becoming available for general use and are helping to solve other problems in computer-aided design.

Much research has been done to parallelize the test pattern generation problem.

Most of this work concentrates on how to use existing multi-processor systems, such as the Intel iPSC/2, Network of Sun workstations, or the Links-1 Z8000 based systems, to effectively generate test patterns.

Parallel techniques for ATPG problem can be classified into five major categories[8]:

- 1. fault partitioning,

- 2. heuristic parallelization,

- 3. search-space partitioning.

- 4. functional (algorithmic) partitioning,

- 5. and topological partitioning.

Although some promising results have been shown, much work still remains.

As the development of microelectronics technology progresses, massively powerful processors will be used to form special parallel architectures to generate test patterns. New architectures for the interconnection of processors have to be studied so as to design a very efficient multi-processor system for ATPG. Therefore, it is natural to investigate a good interconnection network to speed up the ATPG process, when many processors are available. This thesis discusses this problem by proposing several special parallel architectures, and examining the empirical results through simulation. These special architectures are the modified complete binary tree (MCBTA), the autonomous modified complete hinary tree (AMCBTA), and the square array architecture. With these special architectures, the parallel algorithms discussed in this work were found to achieve linear, and sometimes superlinear speedup. The empirical results also show that AMCBTA is the best one among these special architectures.

This report is arranged as follows: Chapter 2 and chapter 3 give a survey of automatic test pattern generation. Chapter 4 shows our experimental results about the faults. Chapter 5 discusses the model for measuring the performance of a parallel automatic test pattern generation system. Chapter 6 describes all algorithms used in our simulation software to simulate parallel automatic test pattern generation systems and evaluate their performance. Chapter 7 briefly discusses 4 connected structures and isomorphism of two graphs. Chapter 8 and 9 demonstrate our three architectures designed to solve test pattern generation problem in parallel. In the conclusion, the results are summarized and some future work are discussed.

## Chapter 2

## Conventional ATPG Algorithms

In this chapter, we will review 3 widely used algorithms, the D-algorithm, the Podem algorithm, and the Fan algorithm. Before this review, the stuck-at model and the testing problem are described.

#### 2.1 Stuck-at Fault Model & Testing Problem

This section first introduces the stuck-at fault model followed by a discussion of the testing problem.

#### 2.1.1 Stuck-at Fault Model

Logic gates are realized by transistors, normally either bipolar transistors or metal oxide semiconductor field-effect transistors (MOSFET, or simply MOS). The technology families based on bipolar transistors are transistor-transistor logic (TTL), emitter-coupled logic (ECL), and so forth. Some logic families based on MOSFET are p-channel MOSFET (p-MOS), n-channel MOSFET (n-MOS), and complementary MOSFET (CMOS). Although ECL and TTL are important for high-speed applications, their integration sizes are limited by the heat generated by their heavy power consumption and by large gate sizes. In contrast, the MOS logic

families are well suited for LSI or VLSI, because higher integration can be obtained than with bipolar logic families. Most LSI and VLSI circuits of today are implemented with MOS.

A fault in a circuit is a model at the logic level of the effect of a physical defect of one or more of its components. Faults can be classified as logical or parametric. is logical fault is a defect that causes the logic function of a circuit element or an input signal to be changed to some other logic function; a parametric fault alters the magnitude of a circuit parameter, causing a change in some factor such as circuit speed, current, or voltage.

Circuit malfunctions associated with timing are due mainly to circuit delays.

Those faults that relate to circuit delays such as slow gates are called delay faults.

Usually, delay faults only affect the timing operation of the circuit, which may cause hazards or critical races.

Faults that are present in some intervals of time and absent in others are intermittent faults. Faults that are always present and do not appear, disappear, or change their nature during testing are called permanent faults or solid faults. Although many intermittent faults eventually become solid, the early detection of intermittent faults is very important to the reliable operation of a circuit. However, there are no reliable means of detecting their occurrence, since such a fault may disappear when test is applied. In this thesis, we will consider mainly logical and solid faults.

When an input or output of a logic gate is always a fixed voltage, either high or low, it is said to have a stark-at fauth. For positive logic, if a node is low, it is said to be stark-at the when it is always a high voltage, it is said to be stark-at t. The most popular fault model used in gate level simulation is the stuck-atfault. The stuck-at-fault model was originally used as a means of describing

faults in early electromagnetic relay computers. However, the model was also

found to be applicable to diode transistor logic (DTL); this led to its use in small

scale integration (SSI) and medium scale integration (MSI) fault modeling. Thus

the model became a standard widely used in the integrated circuit industry[31].

When Roth [32] developed the D-algorithm in 1966, to automatically generate test

sets based on the stuck-at-fault model, its continuation was assured. However, as

failure modes in modern VLSI circuits are better understood, its applicability

and usefulness are being challenged [34]. The CMOS stuck open fault model is

an example.

#### 2.1.2 Testing Problems

To ensure the proper operation of a system, we must be able to detect a fault when one has occurred and to locate it or isolate it to a specific component — preferably an easily replaceable one. The former procedure is called fault detection, and the latter is called fault location, fault isolation, or fault diagnosis. These tasks are accomplished with tests. A lest is a procedure to detect and/or locate faults. Tests are categorized as fault-detection tests or fault diagnostic tests. A fault-detection test tells only whether a circuit is faulty or fault-free; it tells nothing about the identity of a fault if one is present. A fault diagnostic test provides the location and the type of a fault and other information. The quantity of information provided is called the diagnostic resolution of the test; a fault-detection test is a fault diagnostic test of zero diagnostic resolution. If a test not only detects a fault

but also locates the fault, it is a fault diagnostic test of high diagnostic resolution.

Logic circuits are tested by applying a sequence of input ratterns that produce erroneous responses when faults are present and then comparing the responses with the correct (expected) ones. Such an input pattern used in testing is called a trst puttern. In general, a test for a logic circuit consists of many test patterns. They are referred to as a trst srt or test sequence. The latter term, which means a series of test patterns, is used if the test patterns must be applied in a specific order. Test patterns, together with the output responses, are sometimes called trst data.

If there exists only one fault in a circuit, it is said to exhibit a single fault. If there exist two or more faults at the same time, then the circuit exhibits multiple faults. Here, we are only concerned with a single fault in a circuit. For a circuit with k lines, there are tt most 2k possible single stuck-at faults since each line has at most 2 possible faults: stuck-at-0 and stuck-at-1.

The testing of logic circuits is performed in two main stages: generating test patterns for a circuit under test (the test generation stage) and applying the test patterns to the circuit (the test application stage). Thus, the generation of test patterns is important; however, it is very difficult for large circuits, so most of the effort of the past 20 years in this field went into research and development of efficient and economical test generation procedures.

The quality of a test (a set or a sequence of test patterns) depends much on the fault coverage as well as the size or length of the test. The fault coverage (or test coverage) of a test is the fraction of faults that can be detected or located within the circuit under test. The fault coverage of a given test is determined by a process called fault simulation, in which every given test pattern is applied to a fault-free circuit and to each of the given faulty circuits, each circuit behavior is simulated, and each circuit response is analyzed to find what faults are detected by the test pattern. Fault simulation is also used to produce fault dictionaries, in which the information needed to identify a faulty element or component is gathered.

#### 2.2 D-algorithm

The first algorithm for ATPG that was proved complete is the D-algorithm introduced by Roth in 1966[4]. The D-algorithm includes a notation and a calculus with which a single stuck-at fault can be detected at a node in the circuit and propagated to a primary output of the circuit. This algorithm uses a five-valued logic, which consists of the logic value 0 and 1, an unknown value X, and two additional values D and  $\overline{D}$ . A D value signifies a value of 1 in the good circuit and 0 in the faulty circuit, and a  $\overline{D}$  value represents a value of 0 in the good circuit and 1 in the faulty circuit.

Each gate in the circuit has two D-cubes associated with it, the primitive Dcube of a fault (pdcf) and a propagation D-cube (pdc). A pdcf is the set of inputs that produces an error signal on the output of that gate if it contains any fault of the particular type. A pdc specifies the input values necessary to propagate an error signal on an input of a gate to the output.

The D-algorithm's basic operation is the repeated intersection of the D-cubes necessary to perform the tasks required to test for a specific fault. These tasks consist of three processes: fault sensitization, fault propagation, and justification. Fault sensitization is the process by which the circuit node presumeed to exhibit the fault is made to produce an erroneous value as a result of the fault. Sensitization is accomplished by specifying an input combination for the circuit element containing the fault, using the pdcl's, such that the node presumed to exhibit the fault holds the complement of the fault value.

The list of circuit elements closest to the primary outputs that have a D or  $\overline{D}$  on the output is called the D frontier. The objective of fault propagation is to advance the D frontier to the primary outputs. This process sensitizes all possible paths from the fault site to the primary outputs. This multiple-path sensitization is necessary for the D-algorithm to guarantee completeness.

During fault sensitization and fault propagation, certain circuit nodes are required to take on specific values. Establishing this value, or goal, on the node by placing values on the primary inputs is called justification. The primary inputs that can be used to justify a goal are usually determined by backtracking through the circuit topology from the node in question to the primary inputs. A criue is chosen for one of these inputs, and a forward simulation-like process, called forward implication, is performed to see if this input assignment is consistent with satisfying the goal. If it is not, a different value is chosen and the process is repeated. A test is finally generated when the fault sensitized, a path for the fault to be observed at the primary outputs in sensitized, and all of the goals are instified.

As an example of the D-algorithm, consider the circuit under test shown in Figure 2.1. Assume that a test is being generated for a stuck-at 1 fault on node J. The first step is to fill in an initial test cube with a  $\overline{D}$  on node J, as shown in test

Figure 2.1: A Circuit for D-algorithm

| Test Cube | A | В | C | D | E | F | G | 11 | 1 | J  | K | L  |

|-----------|---|---|---|---|---|---|---|----|---|----|---|----|

| 0         |   |   |   |   |   |   |   |    |   | 75 |   |    |

| 1         |   |   |   |   |   |   | 1 |    | N | D  |   |    |

| 2         | 1 | 1 |   |   |   |   | 1 |    | N | D  |   |    |

| 3         | 1 | 1 |   |   |   | 0 | 1 |    | 0 | 7) | 0 |    |

| 4         | 1 | 1 |   |   | 0 | 0 | 1 | 0  | 0 | 1) | 0 | 1) |

| 5         | 1 | 1 | 0 | X | 0 | 0 | 1 | 0  | 0 | 1) | 0 | 1) |

Table 2.1: Test Cubes for Justification First

cube 0 in Table 2.1. This value is then sensitized using a pdcf for the NOR gate (test cube 1). Next, all values implied on other circuit nodes by the previous step are filled in (test cube 2). The next step is to advance the D frontier by setting node K to 0. This implies values on nodes I and F (test cube 3). The 0 value on node I in turn implies 0 values on nodes E and II (test cube 4). The final step is to justify the 0 value on node I by setting input C to a 0 value (test cube 5).

If the values shown in test cube 1b, Table 2.2, were chosen when selecting the

| Test Cube | Λ | В | C | D | Е | F | G | Н | I | J  | K | L |

|-----------|---|---|---|---|---|---|---|---|---|----|---|---|

| 0h        |   |   |   |   |   |   |   |   |   | 75 |   |   |

| 1b        |   |   |   |   |   |   | X |   | 1 | D  |   |   |

| 2b        |   |   |   |   |   |   | X |   | 1 | D  | 1 | 1 |

Table 2.2: Test Cubes for Propagation First

pdcf for the initial fault, the implications of that choice would have caused a test to be impossible, as test cube 2b shows. This problem would have caused the algorithm to backtrack to the last point a choice was made, pick the alternate choice, and proceed from there. In the D-algorithm, choices are available at many internal nodes in the circuit, and more than two choices can be present if there are gates in the circuit with more than two inputs. This fact greatly increases the size of the algorithm's search space and makes backtracking more complex. The D-algorithm can be implemented as recursive routine that pushes or pops test cubes off a test cube stack as required for forward progress or backtracking.

Note that justification of two separate node assignments cannot be undertaken simultaneously, because if an inconsistency occurs, it will not be possible to determine which unique assignment caused it. Also, the original D-algorithm does not specify which process — fault sensitization or fault propagation — is to be undertaken first or whether justification is to be done in intermediate steps or deferred until the process ends. These details are left to the implementation. Unfortunately, the efficiency with which a test can be generated for a specific fault depends heavily on the order of these operations, and the most efficient order is determined by the circuit topology. For example, if in generating a test for J

Figure 2.2: A Podem Example

stuck-at-1 in the circuit of Figure 2.1, fault propagation is done before selecting a pdcf, the unique value of 0 required on node / will be discovered and the pdcf for the faulty gate will be fixed. Test generation can then proceed without the possibility of backtracking. Finding the most efficient order for operations and detecting inconsistencies early in the process is the focus of most subsequently developed algorithms.

#### 2.3 PODEM Algorithm

The Podem (Path-Oriented DEcision-Making) algorithm is an attempt to reduce the size of the solution space that must be searched. Recall that the D-algorithm tries to assign a value to each circuit node. Conflicts can arise when values assigned to different nodes cannot all be justified. Podem tries to eliminate these hidden conflicts by assigning values only to the primary inputs.

The algorithm begins by trying to justify the D or  $\overline{D}$  at the node under test,

similar to the D-algorithm. This justification is done by assigning values to primary inputs that affect the node in question. These primary inputs are again found by backtracking through the circuit topology. When an input assignment is made, a simulation-like process, called forward implication, is run to find all of the node values implied by the assignment. If this new input assignment is incompatible with the goal, the complementary value is tried. If the complementary value assignment also conflicts, the algorithm backtracks efficiently to the previous input assignment. This process results in an orderly search methodology that will implicitly search the entire input space.

This search methodology can be represented by a binary search tree, as Figure 2.3 shows. After the value at the faulty node is justified, subsequent objectives are set up to propagate the D frontier along a path or paths to some primary output. The exact order in which this process occurs is again implementation dependent. The important point is that this strategy of assigning values only to primary inputs orders the search space. This procedure lets the search methodology prune the search tree implicitly and increase efficiency.

Consider, for example, the Figure 2.2, a representation of the binary search space for a J stuck-at-0 fault in the circuit under test. This search space was constructed using the simple heuristic of always first trying the logic value 1 on a primary input. Since assignment of the value 1 for node B in the left-hand subtree is inconsistent, all solutions that live below B in that part of the solution space can be pruned from the search tree. This ordering of the search space also allows it to be divided into disjoint sections so that work on the different sections can proceed simultaneously. Note that the processor must have access to the entire

Figure 2.3: Podem Search Space Diagram

circuit topology and that only one goal may be justified at a time, as with the D-algorithm.

#### 2.4 FAN Algorithm

The Fan algorithm is similar to Podem but includes improvements to increase its efficiency. The major goal of Fan is to reduce the number of backtracks in the search tree. This is accomplished using several techniques, including the consideration of fan-out branches in the circuit as a special case, hence the name Fan.

To examine this concept, we must define several terms. A freeline is a circuit node that has no predecessors that are part of a fan-out loop. As such, freelines may have a uniquely assigned value. In Figure 2.4, lines A through I are examples of freelines. A bound line is the opposite of a freeline. Nodes J and K are bound lines and cannot have unique (independent) values assigned to them. Headlines

Figure 2.4: A Fan Example

are freelines that drive a gate that is part of a reconvergent fan-out loop. Node

/ in the figure is a headline. By definition, headlines can also be assigned values

arbitrarily because they are freelines and can always be independently justified.

They can therefore be treated as primary inputs in the justification process.

Identification of these nodes makes reconvergent fan-out loops much easier to handle. Once a test is found by treating headlines as primary input, the values on them can be justified at the end of the test generation process. Fan also uses a multiple-backtrace procedure for reconvergent fan-out branches buried in the circuit to reduce the number of backtracks that must be made in the search. For example, if a certain value is necessary at node L in the figure, and this circuit is part of some larger circuit, a single backtrace could be made along the path  $L \to J \to G \to A, B$ . Values for inputs A and B could be chosen so that the goal is satisfied with a unique value on nodes I and K. Then if the value on K cannot be achieved with the value chosen for I, a significant amount of backtracking in

the search tree can result. First, with a multiple-backtrace both the  $L \to J \to I$  and  $L \to K \to I$  paths can be used to determine the value needed at I to satisfy the goal. This value would then be set as a requirement for the justification of the value at node L. This process can increase the Fan algorithm's efficiency significantly in a circuit with numerous buried reconvergent fan-out loops.

Three conventional automatic test pattern generation algorithms were discussed. They can often be used to generate test patterns for very hard-to-detect faults. Parallelization is one of the methods used to speed up this procedure.

## Chapter 3

# Taxonomy of Parallel ATPG Algorithms

As mentioned earlier, techniques to parallelize ATPG can be classified into five major categories according to Robert's contribution in [8]: 1) fault partitioning; 2) heuristic parallelization; 3) search-space partitioning; 4) functional (algorithmic) partitioning; and 5) topological partitioning. Tables 3.1, 3.2, 3.3, 3.4 and 3.5 in the following section are taken from this reference. The following sections will give an overview for each category, and present its advantages and disadvantages, the type of parallel machine it has been implemented on, and a brief summary of the reported results.

#### 3.1 Fault Partitioning

Fault partitioning is the simplest way to parallelize the ATPG problem. It first divides the fault set F into several subsets  $F_i$ ,  $i = 1, \dots, m$ ,  $F = \bigcup_{i=1}^m F_i$ , and  $F_i \cap F_j = \emptyset$  where  $i \neq j$ . Every processor  $P_i$  is assigned to generate test patterns to the fault set  $F_i$ . This scheme is called static fault partitioning.

Static fault partitioning results in each processor having a completely separate

Table 3.1: Summary of Fault Partitioning

| Researchers                               | Parallel<br>Machine                    | Scalability                                                                         | Major<br>Results                                                                                                                                                                               |

|-------------------------------------------|----------------------------------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Srinivas<br>Patil, Prith<br>Banerjee      | Intel<br>iPSC/2                        | Neany linear speedup<br>for up to 8 processors;<br>speedup falls off after<br>that. | Demonstrated that ATPG with<br>fault simulation is more efficient<br>than ATPG alone, even in paral-<br>lel environment. Fault partition-<br>ing shows good speedup for up to<br>8 processors. |

| Hideo Fuji-<br>wara, To-<br>moo Inoue     | Network<br>of Sun 3/50<br>workstations | Nearly linear speedup for up to 5 processors.                                       | Verified analysis of optimal grain<br>size for fault-partitioning system<br>with experimental results.                                                                                         |

| Susheel<br>J.Chandra,<br>Janak<br>H.Patel | Network<br>of Sun 3/50<br>workstations | Uniform partitioning:<br>nearly linear speedup for<br>5 processors.                 | Introduced concept of heuris-<br>tic parallelization and developed<br>two methods: uniform and<br>concurrent heuristics. Demon-<br>strated uniform partitioning pro-<br>duces better speedup.  |

task in that it performs the entire test generation procedure on its own. If the fault set is divided carefully, each processor will have roughly the same amount of work and will finish in about the same time. If this is the case, the communication cost is low. In practice, it is very difficult to get such a partition prior to executing the APTG algorithms, so dynamic scheduling is used. In dynamic scheduling, each processor requests a new fault from a master scheduler when it is idle. Dynamic scheduling increases the communications overhead because of requests from idle processors for new faults.

In ATPG, one test pattern can test several faults at the same time. This implies that the time to generate test patterns for those other faults can be saved if a test pattern is found for one fault and at the same time the test pattern can detect those other faults. In static fault partitioning, if one test pattern for fault  $f_i \in F_i$  is found and after fault simulation,  $f_{i_1}, \dots, f_{i_k}$  are found to be detectable by the same test pattern,  $f_{i_1}, \dots, f_{i_k}$  should be removed from F. If  $f_{i_j} \in F_{i_j}$ , it is easy to remove it since the processor itself can do without any communication with other processors. If  $f_{i_j} \in F_i$  ( $i \neq l$ ), communication between  $P_i$  and  $P_i$  is necessary to remove  $f_{i_j}$  from  $F_i$ . This communication increases the parallel system's communication overhead and reduces the possible speedup.

Table 3.1 summaries the current research work using fault partitioning. The best scalability to date is 8 processors.

### 3.2 Heuristic Parallelization

As we know heuristics can be used to guide the algorithm to generate test patterns.

Research has indicated that many heuristics will produce a test for a given fault

within some computation time limit when other heuristics have failed to do so[9].

We can use complementary heuristics to speed up the ATPG in multiprocessor systems.

Suppose there are k different heuristics. k processors are used to generate test patterns, and each processor uses a different heuristic. All the processors compute a test for the same fault. Once a processor succeeds in generating a test for the fault, it sends a message to other processors to notify them to stop working. Then all processors begin to work for a new fault.

Heuristic parallelization has the potential to achieve grader speedups than the uniform-partitioning method because of possible anomalies in the ordering of the heuristics for different faults. For example, suppose the time limit for each of five heuristic in the uniform-partitioning method is 10 seconds and only the last heuristic on the list can generate a test for a specific fault within the time limit, say in 5 seconds. Then the processing time for the uniform-partitioning method will be 45 seconds. However, the concurrent heuristic method will find a test for the same fault in only 5 seconds.

In the heuristic parallelization method, there is no way to ensure that the search space of each processor is disjoint. That is, even though the heuristics used by the processors differ, they might all lead the ATPG algorithm down similar paths to a non-solution and a test may not be found in the allotted time, even though one exists. This means that the heuristic techniques cannot be guaranteed to make all processors work efficiently togeth.: to find a test for a single hard-todetect fault which takes a large amount of computation time.

Table 3.2 gives a summary of heuristic parallelization. It shows that the

Table 3.2: Summary of Heuristic Parallelization

| Researchers                                                        | Parallel<br>Machine | Scalability                                                                 | Major<br>Results                                                                                                                                                                              |

|--------------------------------------------------------------------|---------------------|-----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Susheel J.Chandra, Janak H.Patel  Network of Sun 3/50 workstations |                     | Concurrent heuristics: less<br>than linear speedup for only<br>5 processors | Introduced concept of heuris-<br>tic parallelization and developed<br>two methods: uniform and<br>concurrent heuristics. Demon-<br>strated uniform partitioning pro-<br>duces better speedup. |

speedup is less than linear speedup, for up to at least 5 processors.

# 3.3 Search-space Partitioning

Search-space partitioning is a technique to make all processors work efficiently together to find a test pattern for a single fault.

The search space is divided into sub-search spaces. Given a circuit with  $N_{pi}$ primary inputs, there are  $2^{N_{pi}}$  possible input patterns. The search space is the set which contains all these patterns. A sub-search space is a subset of the search space. A processor searches one of the sub-search spaces. The sub-search spaces for the processors are disjoint and are spread as far as possible across the solution space to maximize the area of the current search. This organization increases the chances of finding a valid solution quickly.

The following is an example which shows one way to partition the whole search space. Suppose there are  $2^k$  processors, the number of primary inputs for a given circuit is  $N_{pi}$  ( $N_{pi} \ge k$ ). Then the whole search space is  $2^{N_{pr}}$ . We can divide it into  $2^k$  sub-search spaces if every processor has an identifier i ( $0 \le i < 2^k - 1$ ). From  $N_{pi}$  inputs, k inputs are selected. These k inputs can work as processor identifiers, or identifiers of sub-search spaces, since  $2^k$  different values can be used to represent  $2^k$  processors. The whole search space is divided by these  $2^k$  values. Without losing generality, the selected k bits are the first k bits in  $N_{pi}$  bits

$$a_0 \cdots a_{k-1} \underbrace{x \cdots x}_{N_m - k}$$

where  $a_i \in \{0,1\}$ ,  $i = 0, \dots, k-1$  and x is a unspecified value forming a sub-search space. This space is assigned to processor  $P_s$ , where  $s = \sum_{i=0}^{k-1} a_i 2^i$ . For each  $P_s$ ,  $P_s = \{s_1 \neq s_2\}$ ,  $s_1 = \sum_{i=0}^{k-1} a_1 2^i$ ,  $s_2 = \sum_{i=0}^{k-1} a_2 2^i$ , there is at least one i,  $a_1 \neq a_2$ . Otherwise, we have

$$s_1 = \sum_{i=0}^{k-1} a_{1i} 2^i = \sum_{i=0}^{k-1} a_{2i} 2^i = s_2$$

This contradicts that  $s_1 \neq s_2$ . Therefore the sub-search spaces are disjoint.

It is impossible to search the whole space within limited time, for large problems, because the search space increases exponentially, so a backtrack limit still must be specified. When the number of backtracks exceeds the limit, the algorithms will give up the search and consider this fault as a hard-to-detect fault.

[13] makes the following observations: First, increasing the backtrack limit on the uniprocessor implementation does not yield better results on hard-to-detect faults, and the parallel algorithm yields better results for an equal number of backtracks. The results are better because the parallel algorithm scarches a larger portion of the solution space. Second, the parallel algorithm runs much faster than the uniprocessor implementation and exhibits early linear speedup in most cases for up to 16 processors.

Table 3.3 shows the current research for search space partitioning. One result

Table 3.3: Summary of Search Space Partitioning

| Researchers                                                                         | Parallel<br>Machine              | Scalability                                                                             | Major<br>Results                                                                                                |

|-------------------------------------------------------------------------------------|----------------------------------|-----------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|

| Srinivas<br>Patil, Prith<br>Banerjee                                                | Intel<br>iPSC/2                  | Nearly linear speedup for up<br>to 16 processors. Superlinear<br>speedup in some cases. | Introduced efficient search space<br>partitioning using Podem<br>algorithm.                                     |

| Akira Moto-<br>hara, Kenji<br>Nishimura,<br>Hideo Fuji-<br>wara, Issao<br>Shirakawa | Links-1<br>Z8000-based<br>system | Averaged linear speedup for<br>up to 50 processors during<br>search space phase.        | Demonstrated good speedup is<br>possible for large numbers of<br>processors using search space<br>partitioning. |

shows that linear speedup can be had for up to 16 processors. Another shows that linear speedup can be had for up to 50 processors. These results are much better than the results in previous subsections.

# 3.4 Functional (algorithmic) Partitioning

An algorithm can be divided into independent subtasks that can then be executed on separate processors in parallel. This method is referred to as functional partitioning.

Motohara[11] uses a type of functional partitioning to remove the easy-todetect faults from the fault list. This procedure is done before the parallel method for hard-to-detect faults presented in the previous section is run. The method begins by dividing the fault list into groups of related faults. Typical related faults include those along the same path between a fault site and a primary output. After the fault list is divided into groups, each group is sent to a cluster of processors that

Table 3.4: Summary of Algorithmic Partitioning

| Researchers                                                                         | Parallel<br>Machine              | Scalability                                                                      | Major<br>Results                                                                                                                                                                               |

|-------------------------------------------------------------------------------------|----------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Srinivas<br>Patil, Prith<br>Banerjee                                                | Intel<br>iPSC/2                  | Nearly linear speedup for up<br>to 8 processors; speedup falls<br>off after that | Demonstrated that ATPG with<br>fault simulation is more efficient<br>than ATPG alone, even in paral-<br>lel environment. Fault partition-<br>ing shows good speedup for up to<br>8 processors. |

| Akira Moto-<br>hara, Kenji<br>Nishimura,<br>Hideo Fuji-<br>wara, Issao<br>Shirakawa | Links-1<br>Z8000-based<br>system | Linear speedup for up to<br>10 processors during algo-<br>rithmic phase.         | Introduced combination of algo-<br>rithmic and search space parti-<br>tioning systems.                                                                                                         |

includes a test generator and a fault simulator. The test generator takes the first fault and generates a test for it using a Podem algorithm with a limited number of backtracks. If a test for a fault is not generated within the backtrack limit, it is considered a hard-to-detect fault and is processed later. If a test is found, it is sent to a fault simulator node. This node runs a version of a concurrent fault simulator[33] to determine which other faults the test pattern detects. These faults are then removed from the fault list.

So far most serial ATPG algorithms developed are difficult to parallelize functionally. In order to efficiently use functional partitioning, a new algorithm for ATPG must be designed.

Table 3.4 shows that the current algorithmic partitioning systems can reach linear speedup for up to 10 processors.

Table 3.5: Summary of Topological Partitioning

| Researchers                                                       | Parallel<br>Machine                               | Scalability                                                                                             | Major<br>Results                                                                                                                                                                            |

|-------------------------------------------------------------------|---------------------------------------------------|---------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Fumiuasu<br>Hirose,<br>Koichiro<br>Takayama,<br>Nobuaki<br>Kamato | Special pur-<br>pose simula-<br>tion<br>processor | No results available speedup<br>falls off after that                                                    | Demonstrated topological parti-<br>tioning for simulation portion of<br>ATPG process.                                                                                                       |

| Glenn A.<br>Kramer                                                | Connection<br>Machine                             | Linear speedup for circuits<br>with up to 15 - 18 inputs.<br>Speedup falls off rapidly af-<br>ter that. | Employs topological partitioning<br>by mapping one circuit element<br>to each Connection Machine pro-<br>cessor. Only current algorithm<br>demonstrated on massively paral-<br>lel machine. |

## 3.5 Topological Partitioning

All parallel algorithms discussed so far require each processor to access to the entire circuit database. This may be a problem for large circuits because each processor may not have enough memory to hold the entire circuit database. Topological partitioning tries to divide a circuit into separate partitions and instantiate each partition on a different processor. Each processor only processes a partition of circuit therefore less memory is needed. Since it is a difficult task to partition circuits so as to parallelize the ATPG algorithm, no ideal method has been reported so far. Further work is needed.

Table 3.5 shows the summary of current research systems using topological partitioning. It is clear that the results are not satisfactory.

So far, most of the techniques for parallel-processing ATPG use one of the commercially available networks to provide communication between processors. Tables 3.1 to 3.5 summarize the previous research work in parallel processing ATPG. For example, [14] and [13] used the Intel iPSC/2; a network of Sun3/50 workstations were used by [10] and [12]. As the number of processors increases, it is unavoidable that network communication load becomes heavier and heavier. As the limited capacity of the communication network is provided, traflic jams appear, computation time decreases and the network saturates. Therefore, in order to permit the computing time to decrease linearly, ATPG requires a communication network which can avoid communication conflicts.

# Chapter 4

# Hard-to-detect Faults

Since massively parallel machines with hundreds or thousands of processors will be available in the future, can these machines be used to efficiently solve the automatic test pattern generation problem? What is the problem which should be concentrated on? Some experiments may give us some hints.

## 4.1 Data from Experiments

Let us first do several experiments.

If we use the PODEM algorithm (implemented by ourselves) with heuristics, which will be discussed later, we can try to discover what the relationship is between backtrack limits and what percentage of faults are solved faults. Here, a solved fault is a fault for which a test pattern is found or its redundancy is proved.

It is reasonable to take the number of primary inputs as a unit of backtrack limit. For example, C432[23] has 36 primary inputs, the backtrack limit is assigned as 36, 2 \times 36, etc. The following explains why it is reasonable.

Different circuits have different sizes. A test set for a circuit with only 10 logic gates can be generated within a constant backtrack limit k. For a

Table 4.1: Statistical Data for Circuits

| Circuit |     | Gates | Faults | Solved Faults |             | Percentage(%) |        |

|---------|-----|-------|--------|---------------|-------------|---------------|--------|

|         | PI  |       |        | Step1         | Step 2      | Step1         | Step 2 |

| C422    | 36  | 160   | 524    | 471           | 471 + 45    | 89.88         | 98.47  |

| C499    | 41  | 202   | 758    | 254           | 254 + 496   | 33.50         | 98.94  |

| C880    | 60  | 383   | 942    | 872           | 872 + 44    | 92.56         | 97.23  |

| C1355   | 41  | 546   | 1574   | 350           | 350 + 1152  | 22.23         | 95.42  |

| C1908   | 33  | 880   | 1879   | 1369          | 1369 + 459  | 72.85         | 97.28  |

| C2670   | 233 | 1193  | 2747   | 2678          | 2678 + 0    | 97.48         | 97.48  |

| C3540   | 50  | 1669  | 3428   | 3180          | 3180 + 96   | 92.70         | 95.50  |

| C5315   | 178 | 2307  | 5350   | 5259          | 5259 + 8    | 98.20         | 98.40  |

| C6288   | 32  | 2416  | 7744   | 6274          | 6274 + 1457 | 81.01         | 99.83  |

| C7552   | 207 | 3512  | 7550   | 7073          | 7073 + 12   | 93.68         | 93.84  |

|         |     |       |        |               |             |               |        |

circuit with 1000 logic gates, within the same backtrack limit k, no test pattern is likely to be found even for one fault. Hence, it is not a good idea to take a constant value as a backtrack limit for all circuits, without considering the difference between their sizes.

In combinational circuits, the size of a circuit is strongly related to the number of primary inputs. In other words, to some extent, the number of primary inputs represents the size of the circuit.

We assign the backtrack limit as the number of primary inputs (one unit) and double the number of primary inputs (two units), respectively, and observe the number of solved faults and percentage of faults. For 10 typical circuits[23], we obtain the following 10 groups of data, which are represented by Table 4.1.

In those tables, every unit is the number of primary inputs of the circuit under

test. For example, circuit C499 has 41 primary inputs. Its unit is 41. Here, 499 represents the number of connecting lines in the circuit. The number of faults is a reduced equivalent fault set based on equivalence fault collapsing [17]. The number of faults to be tested can be reduced by combining, for example, indistinguishable faults into a single set [30]. "Indistinguishable faults", are faults such that there is no test to distinguish between them. Therefore, when generating a test for an n-input AND (OR) gate only (n+2) rather than (2n+2) faults of the gate need to be tested. A systematic approach that reduces the number of faults that have to be tested is based on the idea of fault equivalence classes, i.e. such faults that are covered by a single test set [30].

## 4.2 Inference from Experiments

In the previous section, some experimental results about automatic test pattern generation were discussed. Now, we will see what kind of conclusion we can deduce.

Our data tells us that over 93% faults are solved faults if the backtrack limit is double the number of primary inputs. For the circuit C6288, over 99% of the faults are solved faults. This fact implies that in a system which contains massive processors, fault partitioning can work very efficiently to generate test patterns for most faults. (Why? because most faults are easy to detect). The next stage is the time to concentrate on how to coordinate all processors to solve the remaining faults, which are called hard-to-detect faults.

If there is a system which consists of massive processors, the fault partitioning method can be used to efficiently solve the test pattern generation problem for most of the faults (93% or over), namely, the easy-to-detect faults. There is no communication problem among processors after each processor is assigned a subset of faults. The backtrack limit is double the number of primary inputs, which is a small integer. This implies that there is no big difference between the amount of work done by each processor. The test set may, however, contain many redundant test patterns.

After this first step, the remaining faults are hard-to-detect faults. Any one

of them may require several hours, days or even weeks if one conventional ATPG

algorithm and one processor are used. It was also shown that current parallel

systems are still unsatisfactory for the solution of the automatic test pattern

generation problem.

Therefore, it is time to think about designing a special structure to interconnect many processors in order to make a group of processors solve the automatic test pattern generation problem more effectively, for those hard-to-detect faults.

# PartII Simulation Environment

# Chapter 5

# Model for Measurement

Some kind of a measurement model is important to measure the quality of a system, or to allow meaningful comparisons of different systems. The measurement model must encapsulate the essential functionality of the system in a quantifiable manner.

## 5.1 Model for Measurement

If there is a system which consists of lots of processors and has a specific topology to connect these processors, can the quality of this system be measured? Here quality means the quality of the system for parallel processing of automatic test pattern generation.

One criterion for evaluating the quality of a parallel solution to a problem is how well it scales. There are two aspects which play important roles in the quality of a parallel solution. One is the algorithm, the other is the topology of a multi-processor system.

So far, most research has concentrated on the design of parallel algorithms, which can be executed by a specific multi-processor system. The measure of the

Figure 5.1: Virtual 2 Phase Clock

quality of a parallel solution is determined by how well the algorithm scales. An algorithm scales well if the computation time decreases linearly, or nearly so, with an increase in the number of processors in the system. The speedup of a given parallel algorithm is defined as the ratio of the time taken by the fastest sequential algorithm running in an equivalent uniprocessor to the time taken by the parallel algorithm on the parallel machine. The goal is to have the algorithm's speedup scale linearly with the number of processors.

Since our goal is to design a multi-processor system which has a high performance when generating test patterns, the quality of a parallel solution is how well the system scales. Analogous to the case for a parallel algorithm, a parallel system scales well if the computation time decreases linearly, or nearly so, with an increase in the number of processors in the system. The speedup of a system is defined as the ratio of the time taken by the algorithm running in one processor to the time taken by the algorithm on the multi-processor machine. The goal is to have the system's speedup scale linearly with the number of processors.

A multi-processor system is a tuple  $(P, C, p_i)$ , where P is a set of processors, and every processor is identical. C is a set which contains interconnection information for the processors. All processors execute their own algorithms synchronously under the control of a virtual two phase clock (2PC). Figure 5.1 shows the diagram of 2PC. It is also required that these checking algorithms have the same time complexity. This is very important since all processors work in synchronization. The period of 2PC depends on the lowest speed processor. Since all processors in P are the same, the greater the time complexity, the lower the speed. A low speed will cause other processors to wait.

$p_i \in P$ ,  $p_i$  is the master processor of the system. The master processor is in charge of coordinating the system. For example, it receives tasks from outside, and is the first processor to begin to generate test patterns. It decides whether it is time to stop working because one test pattern has been found to detect a given fault, or time has run out, or a redundant fault is found. It also should report the result to the outside. C determines the topology of a multi-processor system since a topology depends on the connections among processors. If there is a connection between two processors, it means that there is a wire between them on the physical level. Limitations are needed for C because it is impractical to have many wires to input or output data for each processor. Later, we will show that all our multi-processor systems have a 4 connected structure, two for inputs and two for outputs. This results in a simple and natural layout.

In order to measure the quality of a system, the number of two phase clock (2PC) steps is used. The number of 2PC steps (N2PC) is counted to record how many N2PC are used to find a test pattern, or a redundant fault, or a hard-todetect fault. If a multi-processor system can generate all possible 2<sup>th</sup> values for any given integer k, a test pattern can be found eventually — as long as it exists, or a conclusion of redundancy can be reached. Hard-to-detect faults are those whose test pattern has not been found within the specified time limit. With an increasing number of processors, that is  $\mid P \mid \rightarrow \infty$ , every N2PC is recorded. These data are analyzed to determine whether a multi-processor system scales well, which represents the quality of the system.

# 5.2 Parallel Speedup in Test Pattern Generation

In 1864, the philosopher Charles Babbage said:

It is impossible to construct machinery occupying unlimited space; but it is possible to construct finite machinery, and to use it through unlimited time. It is this substitution of the infinity of time for the infinity of space which I have made use of to limit the size of the engine and yet to retain its unlimited power.

We may call this Babbage's thesis. This thesis states that time and space complexity are related and can be traded for one another. As hardware technology develops, we can employ the converse of Babbage thesis: use a very large number of processors to solve the test pattern generation problem. That is to say, we can use space to gain invaluable time.

The central issue in parallel and concurrent processing using a large number of processors is the design of multi-processor systems and parallel algorithms whose performance can be somehow related to the time complexity of the single-processor sequential algorithm,  $T_1$ . Ideally, we require that a parallel algorithm which takes a problem and uses N processors in time  $T_N$  is related to  $T_1$  by the relation  $T_N = T_1/N$ . In other words, we hope that a multi-processor system with N independent processors should be able to compute the solution of a problem Xtimes faster than a single processor. This is called *ideal speed-up*. However, in practice, this speed-up ratio  $T_1/T_N$  often turns out to be far less than N for the following reasons:

- Processors competing for the same communication paths with other processors or to a shared memory can slow down because of the non-availability of paths.

- Since simultaneous reading and writing from a file can cause conflicts, the processors are forced to wait for mutual exclusion.

- Processors need to be conditionally synchronized when different tasks are to be coordinated.

- 4. The sequential component in an algorithm limits the speed of the total process; in o'her words, if T<sub>s</sub> and T<sub>p</sub> are respectively the time spent on serial and parallel components of an algorithm in a single processor, then the maximum speed-up S<sub>N</sub> that can be achieved using N processors in parallel for the parallel component is given by:

$$S_N \le \frac{T_s + T_p}{T_s + \frac{T_p}{N}} = \frac{1}{f + \frac{(1-I)}{N}}$$

where  $f = \frac{T_*}{T_* + T_0}$  and  $0 \le f \le 1$ .

We can find that f is the fraction of computations performed sequentially. For example, if  $f = \frac{1}{k}$ , where k > 1, then  $S_N \le k$ , even if N is very large; obviously, for f = 0,  $S_N = N$ . This is called Amdahl's law.

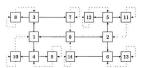

Figure 5.2: One Processor Searches 16 Elements

However, the test pattern generation problem is anomalous. To find a test pattern for a given fault can be considered equivalent to searching a space. N cooperating processors may reach the goal much faster than one processor, even more than N times faster.

Suppose there is a space which has 16 elements. One processor  $P_0$  searches the space according to some heuristics. The goal element can be reached after 15 steps, as shown in Figure 5.2. If four processors,  $P_0$ ,  $P_1$ ,  $P_2$  and  $P_3$ , take part in the search according to the same heuristics, each will search a sub-space, as shown in Figure 5.3. The goal element is found by  $P_3$  after one step.  $T_1/T_4$  is 15, which has greater than 4. This means that there is greater than linear speedup, called superlinear speedup.

This anomaly can also be seen from another point of view. In general, a problem contains n sub-problems. In order to solve this problem, the processing

Figure 5.3: 4 Processors Search 16 Elements

elements in a parallel system have to cooperate with each other to solve all of these n sub-problems. But for the test pattern generation, if a test pattern is found, all of the remaining computation can be omitted. Therefore, not all of the sub-problems must be done.

If a circuit has  $N_{pi}$  primary inputs, the test pattern generation problem for this circuit can be divided into  $2^{N_{pi}}$  sub-problems according to the representive at its primary inputs. Every sub-task is to solve one sub-problem, which is to check whether the given pattern in primary inputs can detect the given fault. If one of the sub-tasks is done and a test pattern is found, all of the remaining unfinished sub-tasks can be ignored. Again, consider the examples in Figure 5.2 and Figure 5.3. In Figure 5.2, when a test pattern is found, 15 sub-tasks have been done, which occupies 93% of all sub-tasks. But in Figure 5.3, only 25% of all sub-tasks

Figure 5.4: A Circuit with One Fault

| Step | 12 | 11 | $I_0$ | Status    |

|------|----|----|-------|-----------|

| 1    | X  | X  | X     | potential |

| 2    | 0  | X  | X     | cannot    |

| 3    | 1  | X  | X     | potential |

| 4    | 1  | 0  | X     | cannot    |

| 5    | 1  | 1  | X     | potential |

| 6    | 1  | 1  | 0     | cannot    |

| 7    | 1  | 1  | 1     | cannot    |

Table 5.1: A Process of the Proof of a Redundant Fault

are done when a test pattern is found. Although only part of the sub-tasks are done, the test pattern generation problem is solved. This is one of the anomalous characteristics of the problem.

How about the redundant fault? Should all sub-tasks be done in order to prove its redundancy? The answer is "No", again.

| Step | 12 | 11 | 10 | Status    |

|------|----|----|----|-----------|

| 1    | X  | X  | X  | potential |

| 2    | X  | X  | 0  | cannot    |

| 3    | X  | X  | 1  | cannot    |

Table 5.2: A Process of the Proof of a Redundant Fault

For example, consider the circuit in Figure 5.4. Table 5.1 and Table 5.2 are two examples which show the process to prove the redundancy of the fault. They clearly show that: it is possible for the proof of a redundant fault to do only part of the sub-tasks, if an unknown value N is used as one of the primary input's value. These two tables also show that the different order of assigning values to primary inputs may cause a different number of sub-tasks to be done. Table 5.1 arranges I<sub>2</sub>, I<sub>1</sub>, I<sub>0</sub> as the order of assignment. Seven sub-tasks are done to prove the redundancy. But Table 5.2 selects I<sub>0</sub> as the first primary input to have its value assigned. It requires only 3 sub-tasks to prove the redundancy. In general, this order of primary inputs is dependent on what heuristics are adopted. Hence, it is not necessary for the proof of a redundant fault to do all of the sub-tasks. Moreover, the heuristics play an important role in deciding how many sub-tasks should be done.

So far, there is no standard method to measure the speedup of parallel systems for test pattern generation.  $T_1/T_N$  is the method widely used [13][8].

For the automatic test pattern generation problem, we may expect a multiprocessor system to generate a test pattern for a given fault very quickly if the test pattern exists and there are enough processors which are interconnected. For example, there is a circuit with N primary inputs. To detect a possible stuck-at fullt, there are  $2^N$  different patterns which can be fed to the circuit. These  $2^N$ different patterns form a pattern set. This pattern set is called the sourch-space because ATPG algorithms always try to search this set so as to find a pattern which can detect the given fault. If there is a multi-processor system which contains  $2^{N+1} - 1$  processors, which are connected to form a complete binary tree, then, within N steps, a test pattern can be found if it exists, or a redundant fault can be proved if there is no test pattern for the given fault.

In practice, it is impossible to have such a system since  $2^N$  is a huge number when N is a little bit large, say N > 20. Therefore, the problem is how to use limited resources, or processors, to find a test pattern in the search-space as quickly as possible. More exactly, the problem of exploring linear speedup is to design a topology to connect given N processors and a protocol to make these Nprocessors communicate with each other so as to find a test pattern or prove its redundancy N times faster than when one processor is used.

# Chapter 6

# Algorithms

This chapter introduces all the algorithms used in our simulation software. Their time complexities are also discussed.

# 6.1 Parser Construction

To generate test patterns, first of all, circuits have to be analyzed. The description of circuits is written in a netlist format[23]. This section discusses the grammar rules of the netlist format; the format is described in detail in Byron [23]. Based on the grammar rules, a parser can be developed directly.

### 6.1.1 The Grammar Rules

The description of the netlist format from Bryan [23] is a list of descriptions of logic gates. The description of a logic gate is called a node since each gate, or primary input, or fanout branch is considered as a node. Using the form of YACC [36], we can use the following grammar rules to represent these:

circuit : node\_list

node\_list : node

I node list node

A eirruit is a list of nodes, denoted by node\_list. A node\_list is described in a recursive way. A node forms a node\_list. A node\_list followed by a node also forms a node\_list.

From the netlist format, nodes can be classified into three types: primary inputs, fanout branches, and logic gates. They have different formats.

Primary inputs have the format:

address name INPT fanout ZERO faults

Fanout branches have the format:

address name FROM name faults

Logic gates have the format:

address name type fanout fanin faults fanin\_line

Here, type represents the type of the gate, for example, AND, NAND, OR, etc.

Using grammar rules, a node can be written as:

node : address name INPT fanout ZERO faults

address name FROM name faults

address name type famout famin faults famin line

Since we adopted the reduced equivalent fault set, which is based on equivalence fault collapsing[23], there may be some nodes labeled no fault, some labeled stuck.at.0, some stuck.at.1, some labeled both. Therefore, the grammar rules of faults can be described as faults :

| S\_A\_0

| S\_A\_1

| S\_A\_0 S\_A\_1

| S\_A\_1 S\_A\_0

The complete grammar rules can be listed as follow:

circuit : node\_list

node\_list : node

| node\_list node

node : address name INPT famout ZERO faults

| address name FROM name faults

address name type famout famin faults famin\_line

address : integer

name : STREAM

N\_ZERO

ZERO

type : AND

NAND

I OR

I NOR

1 XOR

I NXOR

BUFF

| NOT

fanout : integer

fanin : N\_ZERO

faults :

| S\_A\_0

| S\_A\_1

| S\_A\_0 S\_A\_1

| S\_A\_1 S\_A\_0

famin\_line : address\_list

address\_list : address

| address\_list address

integer : ZERO

I N\_ZERO

Here, the address should be an integer. The integer is a zero or a non-zero value. The name can be a zero, or non-zero value, or a string of characters. The fanin and the fanint are integers. The fanin cannot be zero since each logic gate must have at least one input. A logic gate has several inputs, whose addresses are put in the fanin-line field.

With each grammar rule, actions may be associated to be performed each time the grammar rule is recognized in the input process[36]. Then the netlist format can be analyzed, and the needed data structure can be constructed.

## 6.2 Compiler Driven Simulation

In a multi-processor system, there are a lot of processing elements, we call them checking processing elements (CPE), which simultaneously do the same task, checking whether the given trial test pattern can, or cannot, or is possible to detect a given fault. In order to do this job, every CPE does its work in two steps: