FLEXIBLE AND RESOURCE EFFICIENT DESIGN FOR HARDWARE IMPLEMENTATION OF THE ADVANCED ENCRYPTION STANDARD

## Flexible and Resource Efficient Design for Hardware Implementation of the Advanced Encryption Standard

by

© Cheng Wang, M.Sc., B.Eng.

A thesis submitted to the School of Graduate Studies in partial fulfilment of the requirements for the degree of Doctor of Philosophy

Faculty of Engineering and Applied Science Memorial University of Newfoundland March 2012

St. John's

Newfoundland

Canada

## Abstract

In this dissertation, we investigate the performance of a broad range of hardware implementations of symmetric key block ciphers. The major focus of this dissertation is dedicated to the investigation of the performance of hardware implementations of the Advanced Eneryption Standard (AES) influenced by the implementation architecture. The flexibility of the AES algorithm allows an extensive variety of implementation architectures making it necessary to investigate the performance characteristics of these architectures. On the one hand, this investigation identifies the most resourceefficient architecture for the AES implementation targeted at resource-constrained applications; while, on the other hand, this discloses the unique performance tradeoffs from the different architectures allowing flexible implementation of AES.

In this dissertation, two perspectives of the implementation architecture of AES are explored: 1) the pipeline configuration of the AES S-box with the composite field structure and 2) the datpath architecture of AES. For the S-box pipeline configuration, a gate-level approach for the pipeline of 2 to 7 stages and a component level approach for the pipeline of 2 to 4 stages are evaluated. For the datapath architecture, parameterized architectures with the datapath width of 8, 16, 32, 64 or 128 bits and the unrolling factor of 1, 2, 5 or 10 for the 128-bit width are evaluated, among which the 16, 32 and 64-bit architectures are novel designs.

Generic and typical models for these architectures are built. The performance of these implementations in terms of timing, area, power and energy is benchmarked based on Complementary Metal-Oxide Semiconductor (CMOS) technology following Application-Specific Integrated Circuit (ASIC) design flow. The benchmark results demonstrate the potentially significant performance improvement by selecting an appropriate architecture under given throughput requirements compared with other architectures.

For the investigation of S-box pipeline configurations, we examine the performance of the S-box implementation for the 9 configurations over a wide range of throughput requirements. Based on the results, we analyze the influence of the pipeline configuration on the performance and identified the regular trends of the resource costs varying with the pipeline configurations and the throughput requirement/timing constraint. Numerically, there are maximum reductions of 51% in area and 69% in power/energy with an appropriate pipeline configuration throughput requirement/timing constraint comparing with other configurations including no pipeline. For the investigation of datapath architecture, we examined the performance of the datapath implementation for the 8 datapath architectures over a wide range of throughput requirements. The quantitive performance of the architecture implementations is presented, compared and analyzed. The most efficient architecture implementation in area, peak nower and energy, as well as in the overall resource cost is identified. The performance trade-offs over a range of architecture parameter values are disclosed. In contrast to conventional belief, the most compact architecture implementation with the 8-bit width does not help to minimize, but actually increases, the energy consumption even running at a low clock frequency. As well, compact implementations do not result in the minimal peak power. In our research, we also combine the most energy efficient S-box pipeline configuration and datapath

architecture identified from the above and demonstrate the further reduction in energy consumption by the combination. It is found that the combination consumes about 50% less energy than solely the most energy efficient datapath architecture implementation and 80% less energy than the 8-bit width datapath architecture implementation.

The last chapter of this dissertation discusses the design of a newly proposed block cipher named PUFFIN2. PUFFIN2 is designated for lightweight applications with modest security strength requirements. PUFFIN2 has an involutional structure and can lead to a very compact implementation, which is smaller than the previous most compact block cipher PRESENT.

#### Acknowledgements

I would like to deeply express my sincere appreciation and respect to my supervisor Dr. Howard M. Heys. Being his student is really a beneficial and pleasurable experience. His wisdom and knowledge guided me through the difficulties in my studies and research. His kindness and tolerance added lots of flexibility and comfort to my life during the studies and research. His rigorous scholarship and justice convinced me to follow him for lifetime.

I also need to direct my thanks to my supervisory committee members Dr. Ramachandran Venkatesan and Dr. Lihong Zhang, who made efforts to support me, review my thesis and give valuable suggestions. I would also like to thank Dr. Cheng Li and Dr. Theodore S. Norvell for their helps.

It is my great joy to know and get along with many good friends and lab mates in the university, including Dr. Yuanlong Yu, Xiaoning Zhang, Jiankang Wang, Amir Zadeh, Ruoyu Su and Zehua Wang. Thanks for their accompany, support and encouragement. Special gratitude to Dr. Yuanlong Yu for listening to me, understanding me and encouraging me all along the days we work towards Ph.D. degree.

I am grateful to my landlords Betty and Steve, with whom I live since the first week I came here. They accommodate me with a comfortable and carefree home so that I can concentrate on my work at the university. They leave a light on every night for my late getting home, which makes me feel warm even in the coldest days.

Finally, I would like to mention that there is no way to fully appreciate my parents for their love and support and there is also no way to erase my regret not able to accompany them over the years as the only child of them.

# Contents

| A  | bstra | act    |                              | ii    |

|----|-------|--------|------------------------------|-------|

| A  | ckno  | wledge | ements                       | v     |

| Li | st of | Table  | 25                           | xiii  |

| Li | st of | Figur  | res                          | xvi   |

| 1  | Intr  | oduct  | ion                          | 1     |

|    | 1.1   | Motiv  | ration                       | 2     |

|    | 1.2   | Disser | rtation Outline              | 3     |

| 2  | AE    | S and  | the Hardware Implementations | 5     |

|    | 2.1   | The A  | AES Algorithm                | <br>5 |

|    |       | 2.1.1  | Round Function               | <br>6 |

|    |       | 2.1.2  | Datapath                     | <br>9 |

|    |       | 2.1.3  | Key Schedule                 | <br>9 |

|    |       | 2.1.4  | Modes of Operation           | 10    |

|    | 2.2   | Hardv  | ware Implementation of AES   | 11    |

|   |      | 2.2.1  | S-Box I    | mplementation                                      | 11 |

|---|------|--------|------------|----------------------------------------------------|----|

|   |      |        | 2.2.1.1    | Hardware Structures of the AES S-Box               | 11 |

|   |      |        | 2.2.1.2    | Performance of the AES S-Box Structures            | 13 |

|   |      |        | 2.2.1.3    | Pipelined AES S-Box Implementations                | 15 |

|   |      |        | 2.2.1.4    | Potential for S-box Pipelining                     | 16 |

|   |      | 2.2.2  | Datapat    | h Implementation                                   | 17 |

|   |      |        | 2.2.2.1    | High Throughput Implementation                     | 18 |

|   |      |        | 2.2.2.2    | Low Resource Cost Implementation                   | 18 |

|   |      |        | 2.2.2.3    | Potential for Different Architectures              | 20 |

|   |      | 2.2.3  | Charact    | erizing Datapath Implementation Architectures with |    |

|   |      |        | Paramet    | ers                                                | 21 |

|   | 2.3  | Sumn   | ary        |                                                    | 22 |

| 3 | Me   | thodol | ogy of H   | ardware Implementation and Performance Evalu-      |    |

|   | atic | n      |            |                                                    | 23 |

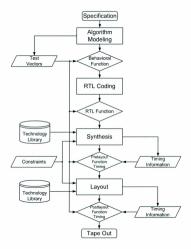

|   | 3.1  | Hardv  | vare Imple | ementation                                         | 23 |

|   | 3.2  | Perfor | mance Ev   | aluation                                           | 26 |

|   |      | 3.2.1  | Evaluati   | on of Timing and Area                              | 26 |

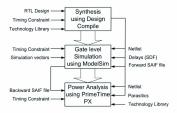

|   |      | 3.2.2  | Power C    | onsumption and Energy Consumption                  | 26 |

|   |      |        | 3.2.2.1    | Dynamic Power Consumption                          | 27 |

|   |      |        | 3.2.2.2    | Static Power Consumption                           | 30 |

|   |      |        | 3.2.2.3    | Energy Consumption                                 | 31 |

|   |      | 3.2.3  | Evaluati   | on of Power and Energy                             | 32 |

|   | 3.3  | Summ   | arv        |                                                    | 33 |

| 4 | Usi               | ng Pip                                                | elined AES S-Boxes for Resource Efficient   | Purpose:                              | An    |                                  |

|---|-------------------|-------------------------------------------------------|---------------------------------------------|---------------------------------------|-------|----------------------------------|

|   | Exa               | mple                                                  |                                             |                                       |       | 35                               |

|   | 4.1               | Introd                                                | uction                                      |                                       |       | 36                               |

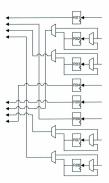

|   | 4.2               | Archit                                                | ecture Design                               |                                       |       | 37                               |

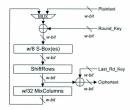

|   |                   | 4.2.1                                                 | The ShiftRows Component                     |                                       |       | 39                               |

|   |                   | 4.2.2                                                 | S-Box                                       |                                       |       | 39                               |

|   |                   | 4.2.3                                                 | The MixColumns Component                    |                                       |       | 40                               |

|   |                   | 4.2.4                                                 | Key Expansion Component                     |                                       |       | 40                               |

|   |                   | 4.2.5                                                 | Overall Design                              |                                       |       | 41                               |

|   | 4.3               | Imple                                                 | mentation Results and Discussion            |                                       |       | 42                               |

|   | 4.4               | Summ                                                  | ary                                         |                                       |       | 46                               |

| 5 | Ext               | loratio                                               | on of S-Box Pipeline Configurations for Fle | cible and I                           | 266-  |                                  |

| 0 |                   |                                                       |                                             | cible and i                           | 5111- |                                  |

|   | cier              | t Impl                                                | ementation                                  |                                       |       | 48                               |

|   |                   |                                                       |                                             |                                       |       |                                  |

|   | 5.1               | Introd                                                | uction                                      |                                       |       | 49                               |

|   | 5.1<br>5.2        |                                                       | uction                                      |                                       |       | 49<br>50                         |

|   |                   | The S                                                 |                                             |                                       |       |                                  |

|   | 5.2               | The S<br>Applic                                       | -box Structure for Pipelining               |                                       | •     | 50                               |

|   | 5.2<br>5.3        | The S<br>Applic                                       | box Structure for Pipelining                |                                       |       | 50<br>52                         |

|   | 5.2<br>5.3        | The S<br>Applic<br>Pipeli                             | box Structure for Pipelining                |                                       |       | 50<br>52<br>54                   |

|   | 5.2<br>5.3        | The S<br>Applic<br>Pipelii<br>5.4.1                   | box Structure for Pipelining                |                                       |       | 50<br>52<br>54<br>55             |

|   | 5.2<br>5.3        | The S<br>Applic<br>Pipelii<br>5.4.1<br>5.4.2<br>5.4.3 | box Structure for Pipelining                |                                       |       | 50<br>52<br>54<br>55<br>57       |

|   | 5.2<br>5.3<br>5.4 | The S<br>Applic<br>Pipelii<br>5.4.1<br>5.4.2<br>5.4.3 | box Structure for Pipelining                | · · · · · · · · · · · · · · · · · · · |       | 50<br>52<br>54<br>55<br>57<br>58 |

|   | 5.6  | Exper   | imental F   | tesults and Analysis                                      | 63 |

|---|------|---------|-------------|-----------------------------------------------------------|----|

|   |      | 5.6.1   | Perform     | ance versus Timing Constraints                            | 63 |

|   |      | 5.6.2   | Perform     | ance versus Pipeline Configurations for the Minimized     |    |

|   |      |         | Timing      | Constraint                                                | 66 |

|   |      | 5.6.3   | Perform     | ance versus Pipeline Configurations for Given Timing      |    |

|   |      |         | Constra     | ints                                                      | 67 |

|   |      |         | 5.6.3.1     | Area versus the Number of Pipeline Stages                 | 71 |

|   |      |         | 5.6.3.2     | Power/Energy versus the Numbers of Pipeline Stages        | 72 |

|   |      |         | 5.6.3.3     | Area versus the Placement Approaches                      | 73 |

|   |      |         | 5.6.3.4     | Power/Energy versus the Placement Approaches              | 73 |

|   |      |         | 5.6.3.5     | Energy-wise Costs                                         | 74 |

|   |      |         | 5.6.3.6     | Trends in One Picture                                     | 75 |

|   |      | 5.6.4   | Benefits    | of Using Pipelined S-Box Implementations                  | 75 |

|   |      |         | 5.6.4.1     | Benefits over Non-Pipelined Implementations $\ . \ . \ .$ | 76 |

|   |      |         | 5.6.4.2     | Benefits over Other Pipeline Configurations $\ . \ . \ .$ | 76 |

|   |      |         | 5.6.4.3     | Benefits of Providing More Performance Options/Trade-     |    |

|   |      |         |             | Offs                                                      | 77 |

|   | 5.7  | Gener   | ality of th | e Methodology and Results                                 | 77 |

|   | 5.8  | Summ    | ary         |                                                           | 78 |

| 6 | Exp  | loratio | on of Dat   | apath Architectures for Flexible and Efficient Im-        |    |

|   | pler | nentat  | ion         |                                                           | 80 |

|   | 6.1  | Introd  | uction .    |                                                           | 81 |

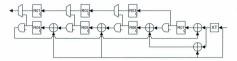

|   | 6.2  | The D   | atapath A   | Architectures of AES                                      | 83 |

|   |     | 6.2.1  | Common Issues                                                     |

|---|-----|--------|-------------------------------------------------------------------|

|   |     |        | 6.2.1.1 S-box Structure                                           |

|   |     |        | 6.2.1.2 Key Expansion                                             |

|   |     |        | 6.2.1.3 Impact of Modes of Operation                              |

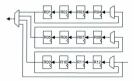

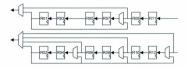

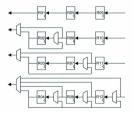

|   |     | 6.2.2  | Partial Datapath Architectures                                    |

|   |     |        | 6.2.2.1 S-boxes                                                   |

|   |     |        | 6.2.2.2 ShiftRows Components                                      |

|   |     |        | 6.2.2.3 MixColumns Components                                     |

|   |     |        | 6.2.2.4 Novel 16-bit, 32-bit and 64-bit Datapath Architectures 91 |

|   |     | 6.2.3  | Complete Datapath Architectures                                   |

|   | 6.3 | Metho  | dology                                                            |

|   |     | 6.3.1  | Deriving the Architecture Implementations                         |

|   |     | 6.3.2  | Evaluation of the Performance                                     |

|   | 6.4 | Exper  | mental Results and Analysis                                       |

|   |     | 6.4.1  | Area                                                              |

|   |     | 6.4.2  | Peak Power Consumption                                            |

|   |     | 6.4.3  | Average Energy Consumption                                        |

|   |     | 6.4.4  | Overall Resource Cost                                             |

|   | 6.5 | Summ   | ary 111                                                           |

| 7 | Der | nonstr | ation of Combined Effects for Energy Efficiency 113               |

|   | 7.1 | Introd | action                                                            |

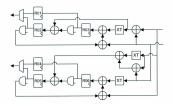

|   | 7.2 | The M  | ethodology                                                        |

|   | 7.3 | Result | s and Analysis                                                    |

|    | 7.4    | Summary                                               | • • | 121 |  |

|----|--------|-------------------------------------------------------|-----|-----|--|

| 8  | Des    | esign of a Lightweight Block Cipher PUFFIN2           |     |     |  |

|    | 8.1    | Introduction                                          |     | 123 |  |

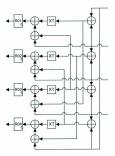

|    | 8.2    | Cipher Specification                                  |     | 125 |  |

|    |        | 8.2.1 Overall Structure                               |     | 125 |  |

|    |        | 8.2.2 Basic Components                                |     | 127 |  |

|    |        | 8.2.3 Encryption and Decryption Process               |     | 128 |  |

|    |        | 8.2.4 Key Schedule                                    |     | 133 |  |

|    | 8.3    | Security Analysis                                     |     | 134 |  |

|    |        | 8.3.1 Differential and Linear Cryptanalysis           |     | 134 |  |

|    |        | 8.3.2 Related-Key Attacks                             |     | 136 |  |

|    |        | 8.3.3 Weak Keys                                       |     | 137 |  |

|    |        | 8.3.4 Updated Cryptanalysis Results                   |     | 137 |  |

|    | 8.4    | Serialized Architecture for Hardware Implementation   |     | 138 |  |

|    | 8.5    | Hardware Implementation Results                       |     | 142 |  |

|    | 8.6    | Summary                                               |     | 144 |  |

| 9  | Cor    | clusions                                              |     | 145 |  |

|    | 9.1    | Summary of Research and Contributions                 |     | 145 |  |

|    | 9.2    | Suggestions for Future Work                           |     | 148 |  |

| Bi | ibliog | raphy                                                 |     | 151 |  |

| А  | Des    | cription of the Operation of the ShiftRows Components |     | 163 |  |

# List of Tables

| 4.1 | Register states of the round operation data path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 43  |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 4.2 | Register states of the key expansion component $\hdots \ldots \hdots \ldots \hdots$ .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 44  |

| 4.3 | Implementation results                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 44  |

| 4.4 | Normalized performance comparison of the architecture using a single                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |     |

|     | S-box with different number of stages $\hdots \hdots \hdo$ | 45  |

| 6.1 | Comparison of 32-bit AES datapath architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 91  |

| 6.2 | Assignments of the timing constraints (in ns) for the architectures ac-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|     | cording to the given throughputs $\hdots$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 98  |

| 6.3 | Areas of the architecture implementations (normalized to $978~{\rm GE})$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 101 |

| 6.4 | Ratios of the area to the maximum throughput of the architectures                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |     |

|     | (normalized to the value of U10)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 102 |

| 6.5 | Peak powers of the architecture implementations (normalized to $66.8$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|     | $\mu W)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 103 |

| 6.6 | Average energy for the encryption of 128-bit plaintext of the architec-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     |

|     | ture implementations (normalized to 0.73 nJ)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 105 |

| 6.7 | Average energy incurred due to static power for the encryption of 128-  |     |

|-----|-------------------------------------------------------------------------|-----|

|     | bit plaintext block of the architecture implementations (normalized to  |     |

|     | 1.1 <i>p</i> J)                                                         | 106 |

| 6.8 | Average energy incurred due to dynamic power of the registers for       |     |

|     | the encryption of 128-bit plaintext of the architecture implementations |     |

|     | (normalized to 34.2 $pJ)$                                               | 109 |

| 6.9 | Overall resource cost of the architecture implementations (normalized   |     |

|     | to the value of W32 under 2.13 Gbps)                                    | 110 |

| 7.1 | Assignments of the timing constraints (in ns) for the architectures un- |     |

|     | der comparison according to the given throughputs                       | 116 |

| 7.2 | Areas of the combined architecture and selected datapath architecture   |     |

|     | implementations (normalized to 978 GE)                                  | 117 |

| 7.3 | Peak powers of the combined architecture and selected datapath archi-   |     |

|     | tecture implementations (normalized to 66.8 $\mu \rm W)$                | 118 |

| 7.4 | Average energy for the encryption of 128-bit plaintext of the combined  |     |

|     | architecture and selected datapath architecture implementations (nor-   |     |

|     | malized to 0.35 <i>n</i> J)                                             | 119 |

| 8.1 | S-box mapping of PUFFIN2 (in hexadecimal)                               | 126 |

| 8.2 | 64-bit Permutation of PUFFIN2                                           | 127 |

| 8.3 | Description of the components of the key schedule                       | 131 |

| 8.4 | Round distribution of PL64, PR64, L64 and R64                           | 131 |

| 8.5 | Implementation results of PUFFIN2 and serialized PRESENT                | 141 |

| 8.6 | Count of hardware components of PUFFIN2 and serialized PRESENT          | 143 |

|     |                                                                         |     |

| A.1 | Contents of the registers of the 8-bit width $ShiftRows$ component at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

|     | the selected clock cycles $\hfill \ldots \hfill \hfill \ldots \hfi$      | 164 |

| A.2 | Contents of the registers of the 16-bit width $ShiftRows$ component at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|     | the selected clock cycles $\hfill \ldots \hfill \ldots \h$ | 164 |

| A.3 | Contents of the registers of the 32-bit width $ShiftRows$ component at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|     | the selected clock cycles $\hfill \ldots \hfill \ldots \h$ | 165 |

| A.4 | Contents of the registers of the 64-bit width $ShiftRows$ component at                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |     |

|     | the selected clock cycles $\hfill \ldots \hfill \ldots \h$ | 165 |

| B.1 | Contents of the registers of the 8-bit width $MixColumns\ {\rm component}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |     |

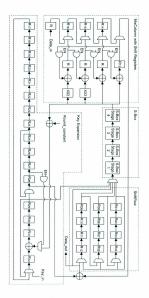

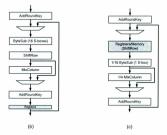

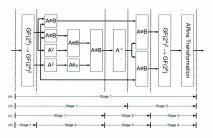

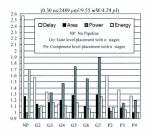

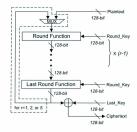

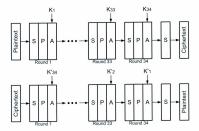

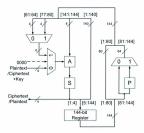

|     | for the clock cycles during a complete operation $(m=n+1)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 167 |