PERFORMANCE ANALYSIS, DESIGN AND RELIABILITY OF THE BALANCED GAMMA NETWORK

CENTRE FOR NEWFOUNDLAND STUDIES

TOTAL OF 10 PAGES ONLY MAY BE XEROXED

(Without Author's Permission)

YASER EL SAYED

### Performance Analysis, Design and Reliability of the Balanced Gamma Network

by

©Yaser El Sayed, B.Sc., M.Sc.

A thesis submitted to the School of Graduate Studies in conformity with the requirements for the Degree of Doctor of Philosophy

Faculty of Engineering and Applied Science Memorial University of Newfoundland December 1999

St. John's

Newfoundland

Canada

### Abstract

Switching is one of the bottlenecks restraining the efforts of researchers toward implementing broadband communication systems. In this dissertation, we provide a comprehensive study of a promising switching architecture called the Balanced Gamma (BG) network. The BG network has shown good performance in terms of throughput, average cell delay, and reliability, and has displayed potential for application in broadband communications switch fabrics.

Designing highly reliable systems is a crucial requirement in the industry of broadband communications where consequences of the system failures are very expensive. Accordingly, we provide an exact model for network reliability of the BG network. The model demonstrates that the network is highly reliable and can be confidently deployed in communication systems.

The performance of the network is further investigated under different payloads containing uniform and non-uniform traffic. Uniform random and bursty are the traffic types used. Several simulation experiments are carried out to measure the cell loss, cell average delay, and buffering requirements of the BG network. In addition, we pursue an analytical model under uniform random traffic to verify our simulation results. The performance of the network is compared with both an ideal nonblocking network and the crossbar network. It is determined that the network has much better behavior than the crossbar switch and operates very closely to the ideal architecture under most types of offered traffic loads.

Finally, we introduce a VLSI design for the BG network using 0.35 CMOS technology supported by the Canadian Microelectronics Corporation. The design has mainly three components, the switching element, the output port, and the network main controller. The design features built-in self-test (BIST) which has become an essential part of any fast digital system. We also parametrize the design such that the amount of effort needed to generate a fabric with arbitrary size is minimal. We describe the design in the Very High Speed Integrated Circuit Description Language (VHDL).

## Acknowledgments

First of all, I am thankful to The Almighty God, Who in His infinite mercy have helped me to bring this work to light.

I also owe a lot to my family, especially my mother and father for their continuous support and great sacrifices that were the major factors in making this work a reality.

I like to express my sincere thanks to my supervisor Dr. Venkatesan for his supervision, support, and cooperation in the course of this work. I also do not forget the support and help of my supervisory committee Dr. Howard Heys and Dr. Paul Gillard.

I like to thank the School of Graduate Studies at the Memorial University of Newfoundland for the financial support it provided during my Ph.D. program.

I will always remember the important discussions I had with Dr. Rod Byrne in the Department of Computer Science. These discussions have greatly enabled me in the design phase of the this work. Also, Mr. Michael Rendell in the Department of Computer Science deserves special thanks for his true cooperation in fixing the problems related to the VLSI CAD tools.

Finally, I like to thank all my friends and colleagues that sincerely helped during my Ph.D. program. I specially thank B. Balasubramanian, A. Khan, P. Mehrotra, K. Momin, F. Power, R. Thuppal, V. Vujjeni, and A. M. Zeiner.

# Contents

|   | Abs  | tract                                        | i   |

|---|------|----------------------------------------------|-----|

|   | Ack  | nowledgments                                 | iii |

|   | Tab  | le of Contents                               | iv  |

|   | List | of Figures                                   | vii |

|   | List | of Tables                                    | xi  |

|   | Not  | ation and List of Abbreviations x            | iii |

| 1 | Int  | oduction                                     | 1   |

|   | 1.1  | Background                                   | 1   |

|   | 1.2  | ATM Switching and IP Switching               | 2   |

|   | 1.3  | Motivation                                   | 7   |

|   | 1.4  | Thesis Organization                          | 8   |

| 2 | Fas  | t Packet Switching Networks                  | 10  |

|   | 2.1  | Introduction                                 | 10  |

|   | 2.2  | Classifications of Packet Switching Networks | 10  |

|   | 2.3  | Time Division Switch Fabrics                 | 13  |

|   |      | 2.3.1 Shared Medium Architectures            | 13  |

|   |     | 2.3.2 Shared Memory Architectures                 |  |

|---|-----|---------------------------------------------------|--|

|   | 2.4 | Space Division Switch Fabrics                     |  |

|   |     | 2.4.1 Single Stage Architectures                  |  |

|   |     | 2.4.2 Multistage Interconnection Networks 25      |  |

|   |     | 2.4.2.1 Single Path MINs                          |  |

|   |     | 2.4.2.2 Multipath MINs                            |  |

|   | 2.5 | Summary                                           |  |

| 3 | Bal | anced Gamma Network 42                            |  |

|   | 3.1 | Introduction                                      |  |

|   | 3.2 | Historical Background                             |  |

|   |     | 3.2.1 Topology                                    |  |

|   |     | 3.2.2 Routing Algorithm                           |  |

|   | 3.3 | Balanced Gamma New Structure                      |  |

|   | 3.4 | Summary                                           |  |

| 4 | Per | formance Under Uniform and Non Uniform Traffic 49 |  |

|   | 4.1 | Introduction                                      |  |

|   | 4.2 | Buffering Strategies                              |  |

|   |     | 4.2.1 Input/Output Buffering 51                   |  |

|   |     | 4.2.2 Internal Buffering                          |  |

|   | 4.3 | Uniform Random Traffic                            |  |

|   |     | 4.3.1 Analytical Modelling 58                     |  |

|   |     | 4.3.2 Finite Output Buffer                        |  |

|   | 4.4 | Bursty Traffic                                    |  |

|   | 4.5 | Non-Uniform Traffic                               |  |

|   |     | 4.5.1 L = 1                                       |  |

|   |     | 4.5.2 L > 1                                                       |

|---|-----|-------------------------------------------------------------------|

|   | 4.6 | Summary                                                           |

| 5 | Des | sign of the Balanced Gamma Network 90                             |

|   | 5.1 | Introduction                                                      |

|   | 5.2 | Design Flow, Functional Test and Verification                     |

|   | 5.3 | Design for Testability                                            |

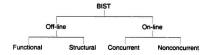

|   |     | 5.3.1 BIST Methods                                                |

|   |     | 5.3.2 Structural Off-Line Architectures and Stimulus Structures 9 |

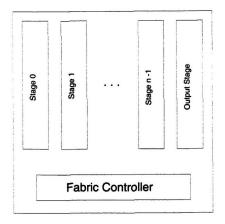

|   | 5.4 | Chip Architecture                                                 |

|   | 5.5 | System Components                                                 |

|   |     | 5.5.1 Switching Element 100                                       |

|   |     | 5.5.2 Output Port Controller                                      |

|   |     | 5.5.3 Network Main Controller                                     |

|   | 5.6 | Simulation and Test Results 12                                    |

|   | 5.7 | Summary                                                           |

| 6 | Fau | alt Tolerance and Reliability Properties 130                      |

|   | 6.1 | Introduction                                                      |

|   | 6.2 | Background                                                        |

|   | 6.3 | Fault Tolerance Properties of the BG Network                      |

|   | 6.4 | Reliability Analysis                                              |

|   |     | 6.4.1 Terminal Reliability                                        |

|   |     | 6.4.2 Broadcast Reliability                                       |

|   |     | 6.4.3 Network Reliability                                         |

|   |     | 6.4.4 Mean Time to Failure                                        |

|   | 6.5 | Summary                                                           |

| 7 Conclusion and Future Work |                                          | 149 |  |

|------------------------------|------------------------------------------|-----|--|

|                              | 7.1 Future Work                          | 152 |  |

|                              | References                               | 155 |  |

| A                            | Balanced Gamma Network Topology          | 166 |  |

| в                            | Balanced Gamma Network Routing Algorithm | 167 |  |

| с                            | Thoughput Under Uniform Random Traffic   | 174 |  |

| D                            | Calculation of $INF_i$ and $LNF_i$       | 176 |  |

# List of Figures

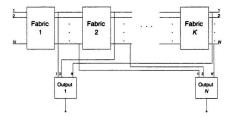

| 1.1  | A block diagram of a switch fabric                                     | 6  |

|------|------------------------------------------------------------------------|----|

| 2.1  | Classification of interconnection networks [1]                         | 12 |

| 2.2  | A basic bus-based switch fabric                                        | 13 |

| 2.3  | A basic ring-based switch fabric                                       | 14 |

| 2.4  | Memory capacity of AHQs versus shared buffer [2]                       | 17 |

| 2.5  | COM16M architecture [3]                                                | 19 |

| 2.6  | A crossbar switch fabric.                                              | 21 |

| 2.7  | Crossbar SE states.                                                    | 21 |

| 2.8  | Knockout switch architecture                                           | 23 |

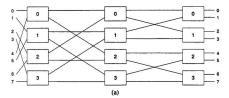

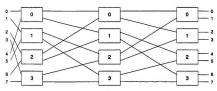

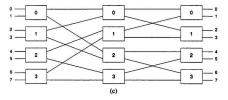

| 2.9  | Different banyan network topologies (a) banyan (b) omega (c) baseline. | 27 |

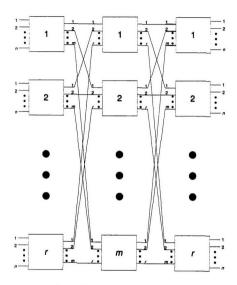

| 2.10 | Architecture of the Clos network.                                      | 30 |

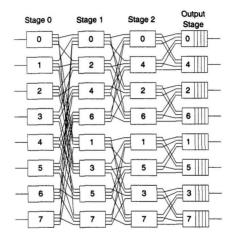

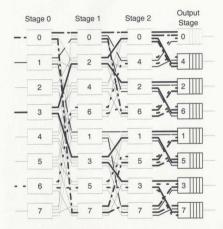

| 2.11 | Architecture of an $8 \times 8$ Kappa network [4]                      | 32 |

| 2.12 | Architecture of an $8 \times 8$ BB network [5]                         | 33 |

| 2.13 | The architecture of an $8\times 8$ Beneš network                       | 35 |

| 2.14 | A switching element in a 2-dilated banyan network                      | 36 |

| 2.15 | The tandem architecure                                                 | 37 |

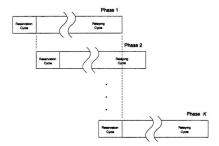

| 2.16 | Timing sequence of the different pipeline phases                       | 39 |

| 2.17 | The pipeline architecture.                                             | 40 |

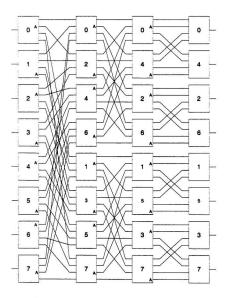

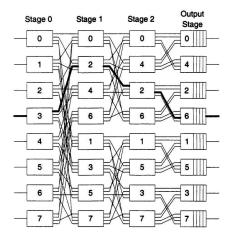

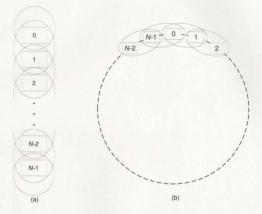

| 3.1  | Initial BG structure.                                                  | 44 |

| 3.2  | New BG structure.                                                                                                 | 47 |

|------|-------------------------------------------------------------------------------------------------------------------|----|

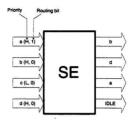

| 3.3  | A SE routing decision example.                                                                                    | 48 |

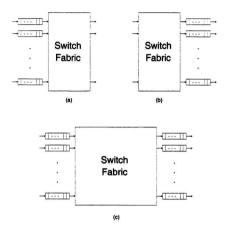

| 4.1  | Input-output buffer strategies (a) pure-input (b) pure-output (c) input-                                          |    |

|      | output buffering                                                                                                  | 52 |

| 4.2  | Behavior of $D_{in}$ and $D_{out}$                                                                                | 54 |

| 4.3  | Different internal buffering styles (a) input (b) output (c) crosspoint                                           |    |

|      | (d) shared buffering                                                                                              | 55 |

| 4.4  | Performance of $64 \times 64$ Banyan with internal shared buffering strategy                                      |    |

|      | [6]                                                                                                               | 56 |

| 4.5  | Discrete Markov chain of the input buffer status (a) at the beginning                                             |    |

|      | of every $T$ , and (b) after every $t_r$                                                                          | 59 |

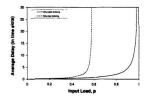

| 4.6  | Average cell delay under URT for different network types of $N \approx 256$ .                                     | 65 |

| 4.7  | Maximum cell delay under URT for different network types of $N = 256$ .                                           | 66 |

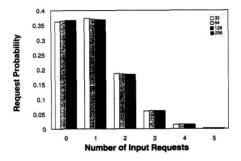

| 4.8  | Probability density for number of input requests for a single output port.                                        | 68 |

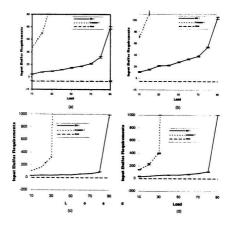

| 4.9  | Average cell delay for different average burst length (a) $L = 5$ , (b)                                           |    |

|      | L = 10, (c) $L = 15$ , (d) $L = 20$                                                                               | 72 |

| 4.10 | Maximum cell delay for different average burst length (a) $L = 5$ , (b)                                           |    |

|      | L = 10, (c) $L = 15$ , (d) $L = 20$                                                                               | 73 |

| 4.11 | Input buffer requirements for different average burst length (a) $L = 5$ ,                                        |    |

|      | (b) $L = 10$ , (c) $L = 15$ , (d) $L = 20$                                                                        | 74 |

| 4.12 | Output buffer requirements for different average burst length (a) $L = 5$ ,                                       |    |

|      | (b) $L = 10$ , (c) $L = 15$ , (d) $L = 20$                                                                        | 75 |

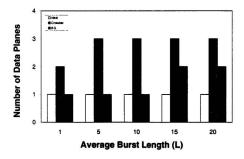

| 4.13 | Required number of planes to attain a $10^{-7}\ {\rm cell}\ {\rm loss}\ {\rm ratio}\ {\rm with}\ {\rm different}$ |    |

|      | average burst lengths                                                                                             | 76 |

| 4.14 | Average cell delay for different average burst length (a) $L = 5$ , (b)     |     |

|------|-----------------------------------------------------------------------------|-----|

|      | L = 10, (c) $L = 15$ , (d) $L = 20$                                         | 78  |

| 4.15 | Maximum cell delay for different average burst length (a) $L = 5$ , (b)     |     |

|      | L = 10, (c) $L = 15$ , (d) $L = 20$                                         | 79  |

| 4.16 | Input buffer requirements for different average burst length (a) $L = 5$ .  |     |

|      | (b) $L = 10$ , (c) $L = 15$ , (d) $L = 20$                                  | 80  |

| 4.17 | Output buffer requirements for different average burst length (a) $L = 5$ , |     |

|      | (b) $L = 10$ , (c) $L = 15$ , (d) $L = 20$                                  | 81  |

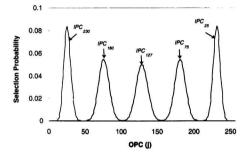

| 4.18 | OPCs selection probability for different IPCs according to the model        |     |

|      | in [7]                                                                      | 83  |

| 4.19 | Performance parameters of different configurations under different loads    |     |

|      | of non-uniform traffic.                                                     | 86  |

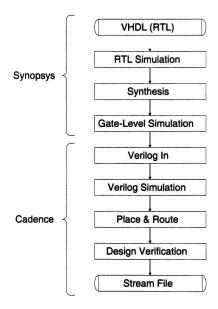

| 5.1  | Design flow recommended by CMC.                                             | 92  |

| 5.2  | BIST methods [8]                                                            | 94  |

| 5.3  | Different structural BIST architectures [9]                                 | 97  |

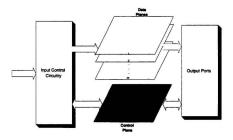

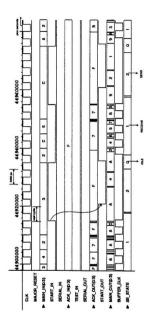

| 5.4  | Top level description of the BG network                                     | 99  |

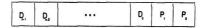

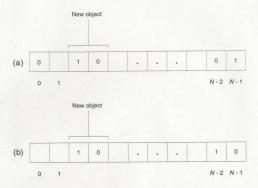

| 5.5  | Structure of the internal cell header.                                      | 102 |

| 5.6  | Broadcast requests at inputs 0, 1, 3, and 6 are fulfilled                   | 104 |

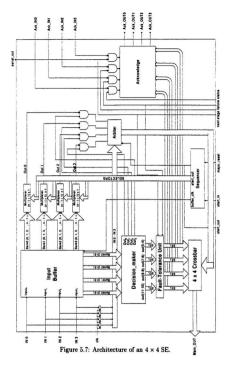

| 5.7  | Architecture of an $4 \times 4$ SE                                          | 105 |

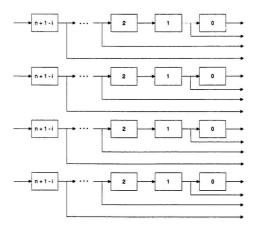

| 5.8  | Block diagram of the input buffer bank of an SE at $Stage_i$                | 107 |

| 5.9  | ASM chart of the SE sequencer                                               | 111 |

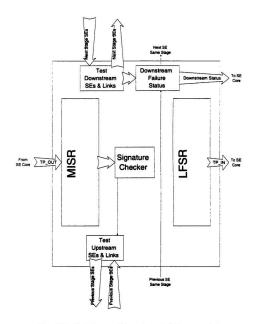

| 5.10 | Block diagram of the testing unit during test period                        | 113 |

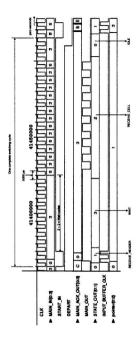

| 5.11 | Architecture of the OPC                                                     | 116 |

| 5.12 | ASM chart of the OPC sequencer                                              | 119 |

| 5.13 | Block diagram of the Buffer controllers                                     | 120 |

| 5.14 | The ASM chart of the network main controller                                | 122 |

|------|-----------------------------------------------------------------------------|-----|

| 5.15 | Simulation results for an $4 \times 4$ SE                                   | 126 |

| 5.16 | Simulation results for an OPC.                                              | 127 |

| 6.1  | All possible SEs that can be visited by a cell arriving at input port $i$ . | 133 |

| 6.2  | TR best case R-graph for $16 \times 16$ BG network                          | 138 |

| 6.3  | TR worst case <i>R</i> -graph for 16 × 16 BG network                        | 138 |

| 6.4  | $TR$ worst case <i>R</i> -graph for $N \times N$ BG network                 | 139 |

| 6.5  | BR R-graph for an 8 × 8 BG network.                                         | 141 |

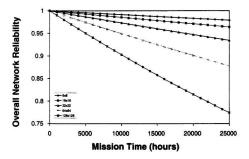

| 6.6  | (NR <sub>overall</sub> ) performance of the BG network.                     | 145 |

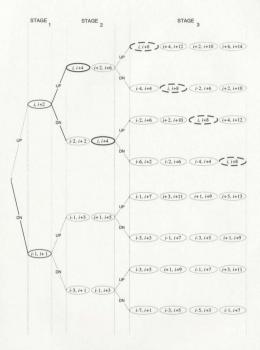

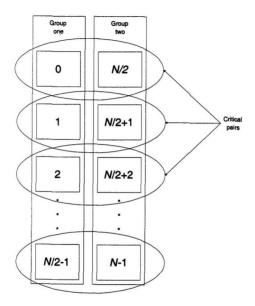

| D.1  | The model of the critical pairs for an intermediate stage                   | 177 |

| D.2  | Expansion of the problem into two queues                                    | 178 |

| D.3  | Dividing SEs in the last stage into two groups                              | 180 |

## List of Tables

| 2.1 | Control plane speed reduction ratio [10]                                        | 40  |

|-----|---------------------------------------------------------------------------------|-----|

| 4.1 | Analytical and simulation results for the BG network with zero input            |     |

|     | buffering                                                                       | 61  |

| 4.2 | Effect of input buffer size on the $TP_{max}$ of a single data plane BG network | 62  |

| 4.3 | Cell loss under URT for different network types of $N=256.$                     | 63  |

| 4.4 | Input-output buffering requirements under URT for different network             |     |

|     | types of $N = 256$                                                              | 67  |

| 4.5 | Cell loss ratio under bursty loads of various burst lengths. $\ldots$ .         | 70  |

| 4.6 | Number of planes followed to compare the multiple plane configura-              |     |

|     | tions of the architectures under test.                                          | 74  |

| 4.7 | Cell loss ratio for single plane architectures under non-uniform traffic        |     |

|     | load                                                                            | 84  |

| 4.8 | Input buffer requirements for BG-1 configuration under uniform and              |     |

|     | non-uniform bursty loads.                                                       | 87  |

| 4.9 | Output buffer requirements for BG-1 configuration under uniform and             |     |

|     | non-uniform bursty loads.                                                       | 88  |

| 5.1 | Stimulus design approaches [9]                                                  | 98  |

| 5.2 | Defined cell types                                                              | 102 |

|     |                                                                                 |     |

| 5.3 | Distribution of the hardware complexity of the SEs in a $16 \times 16$ (in                      |       |

|-----|-------------------------------------------------------------------------------------------------|-------|

|     | gates)                                                                                          | 115   |

| 5.4 | Delays of the SEs critical paths                                                                | 117   |

| 5.5 | Distribution of hardware complexity for OPC (in gates).                                         | 122   |

| 5.6 | Illustration of cell arrival in Figure 5.15.                                                    | 125   |

| 5.7 | Illustration of cell arrival in Figure 5.16.                                                    | 128   |

| 6.1 | SEs' complexities (in $\mu m^2$ ) for different sizes of the BG network                         | 135   |

| 6.2 | Failures/10 <sup>6</sup> hours ( $\lambda_f$ ) for the components of 128 × 128 BG network       |       |

|     | due to the first part of the model                                                              | 136   |

| 6.3 | Estimated failures/10 <sup>6</sup> hours ( $\lambda_{II}$ ) due to the second part of the model | . 136 |

| 6.4 | Behavior of the $TR$ for various sizes of the BG network                                        | 139   |

| 6.5 | Behavior of the $BR$ for various sizes of the BG network                                        | 142   |

| 6.6 | Behavior of the $BR$ for various sizes of the BG network by excluding                           |       |

|     | the $p_{OPC}^N$ term.                                                                           | 142   |

| 6.7 | Behavior of the $NR$ for various sizes of the BG network by excluding                           |       |

|     | both the FSR and OSR terms                                                                      | 145   |

| 6.8 | Estimated BG network failures/10 <sup>6</sup> hours.                                            | 146   |

## Notation and List of Abbreviations

| n        | : number of stages in a MIN                                   |

|----------|---------------------------------------------------------------|

| Bout     | : output buffer size                                          |

| BR       | : broadcast reliability                                       |

| $D_{in}$ | : delay in pure-input buffering strategy                      |

| Dout     | : delay in pure-output buffering strategy                     |

| $IL_i$   | : intput link i of an SE                                      |

| K        | : number of data planes is a switching network                |

| L        | : average burst length                                        |

| N        | : number of inputs/outputs in a rectangular switching network |

| NR       | : network reliability                                         |

| OL       | : output link i of an SE                                      |

| Ρ        | : number of service priorities                                |

| TP       | : Throughput                                                  |

| TR       | : terminal reliability                                        |

| α        | : switching parameter for the old routing decision of the     |

|          | BG network                                                    |

| λ        | : failure rate                                                |

| AHQ      | : Address Holding Queues                                      |

| ATE      | : Automatic Test Equipment                                    |

| ATM      | : Asynchronous Transfer Mode                                  |

| BB       | : Batcher Banyan                                              |

| BG       | : Balanced Gamma                                              |

| B-ISDN   | : Broadband Integrated Services Digital Network               |

| BIST     | : Built-In Self-Test                                          |

| BP       | : backpressure                                                |

| CAC      | : Connection Admission Control                                |

| CMC      | : Canadian Microelectronics Corporation                       |

| CMOS     | : Complementary Metal Oxide Semiconductor                     |

| CP       | : Control Port                                                |

| CUT      | : Circuit Under Test                                          |

| DPO      | : Delayed Pushout                                             |

| DSM      | : Deep Submicron                                              |

| ECL      | : Emitter Coupled Logic                                       |

| EFCI     | : Explicit Forward Congestion Indication                      |

| EXCON    | : Expand-Concentrate                                          |

| FIFO     | : First-In First-Out                                          |

| GFC      | : Generic Flow Control                                        |

| GN    | : Gamma Network                                             |

|-------|-------------------------------------------------------------|

| HOL   | : Head Of Line                                              |

| IETF  | : Internet Engineering Task Force                           |

| IP    | : Internet Protocol                                         |

| IPng  | : Internet Protocol next generation                         |

| IPv4  | : Internet Protocol version 4                               |

| IPv6  | : Internet Protocol version 6                               |

| ITU-T | : International Telecommunications Unit-Telecommunications  |

|       | Standardization Sector                                      |

| KN    | : Kappa Network                                             |

| LAN   | : Local Area Network                                        |

| LANE  | : LAN Emulation                                             |

| LFSR  | : Linear Feedback Shift Register                            |

| MIN   | : Multistage Interconnection Network                        |

| MISR  | : Multiple In Shift Register                                |

| MPOA  | : MultiProtocol Over ATM                                    |

| MTTF  | : Mean Time To Failure                                      |

| NC    | : No Controls                                               |

| NMC   | : Network Main Controller                                   |

| ORA   | : Output Response Analyzer                                  |

| PO    | : Pushout                                                   |

| QoS   | : Quality of Service                                        |

| RBP   | : Restricted Backpressure                                   |

| SE    | : Switching Element                                         |

| SIN   | : Single-stage Interconnection Network                      |

| SRN   | : Semi-Rearrangeably Nonblocking                            |

| STD   | : Synchronous Time Division                                 |

| RI    | : Ring Interface                                            |

| RTL   | : Register Transfer Level                                   |

| UPC   | : Usage Parameter Control                                   |

| URT   | : Uniform Random Traffic                                    |

| VCI   | : Virtual Channel Identifier                                |

| VHDL  | : Very high speed integrated circuit High Level Description |

|       | Language                                                    |

| VPI   | : Virtual Path Identifier                                   |

|       |                                                             |

# Chapter 1 Introduction

#### 1.1 Background

Currently, the telecommunications industry is split between two protocols; namely the asynchronous transfer mode (ATM) and the internet protocol (IP). ATM has been identified by the International Telecommunications Unit - Telecommunications Standardization Sector (ITU-T) as a comprehensive switching technique that is capable of meeting the requirements of B-ISDN: such as high throughput, low switching delay, low packet loss probability, expandability, testability, fault tolerance, low cost, and ability to achieve broadcasting as well as multicasting. B-ISDN (broadband integrated service digital network) is the extension of the ISDN (previously defined for telephone and data transmission services). B-ISDN will be capable of providing all services (audio, video, and data transfer applications) in a unified fashion to various places at varying speeds. The advantages are ease of installation and maintenance, better user access and economical service, and flexibility in the introduction and evolution of services. ATM is also expected to provide communication services with negotiable quality of service (QoS) levels. IP was invented to be the network laver (layer 3 in the OSI model) protocol running on the top of Ethernet and Token Ring local area networks (LANs). The original versions of IP, such as IP version 4 (IPv4),

are unreliable. Messages are dropped without retransmission and without warning the transmitting applications; i.e. it does not support QoS. A new IP standard has been proposed to support QoS and to solve the well known problem of address exhausion. The new standard is known as IP next generation (IPng) or IPv6 [11].

Both the MTM and IP are packet switching protocols; however, there are major differences between them:

- IP carries variable-length packets, with lengths varying from 12 up to 64k octets; ATM carries fixed-length cell of 53 octets.

- ATM is a connection-oriented protocol, i.e. a path should be established for each connection; IP is a connectionless protocol.

- IP is generally datagram; ATM is switched-path.

- IP is designed for broadcast media and many of the features of the IP rely on this broadcast nature; ATM is fundamentally a point-to-point protocol, having to simulate a broadcast by using point-to-multipoint or multiple point-to-point connections.

In this chapter, we will not discuss the ATM or the IP protocols in detail. They are discussed extensively in the literature [12, 13, 14, 15]. Here we will only concentrate on the switching aspects in both protocols.

#### gnidotiwe AI bas gnidotiwe MTA 2.1

ATM networks are based on the following concepts: 1) virtual circuits, 2) facet-size packets (cells), 3) small packet size, 4) statistical multiplexing, and 5) integrated services. The key to providing integrated services is for connections of each service rype to get a different QoS. This QoS is provided by the network resources auch type to get a different QoS. as end-systems, network controllers, and switch fabrics. With the diverse types of services expected in the ATM networks, the QoS requirements differ from one service to another. Some services are sensitive to delays, such as real time applications, and some other services are sensitive to cell loss, such as data transfer. Also, the sensitivity level differs from one end-user to another. The maximum cell rate, maximum cell delay, average cell delay, and cell loss probability are parameters used to characterize the QoS. If an end-system is requesting a certain level of QoS that the network resources can not furnish, then the network blocks this request. In some cases the network rejects a request of an end-system even if there are sufficient resources for that request [16]. This takes place when the request violates the initial QoS contract between the network and the end-system.

Congestion and flow control are among the most complex issues with the ATM technology. The reasons for this complexity are very evident [17]. Firstly, the diverse service classes that ATM promises to handle with acceptable QoS levels. Secondly, the ATM technology will appear in different network domains - LAN, MAN, and WAN - that have large differences in the field equipment such as speed and buffering. Thirdly, although the ATM switches can protect themselves from congestion by discarding cells, this may result in poorer overall throughput of the network especially for applications which employ encryption/compression where even losing one cell can lead to losing the whole message sent. There are nine mechanisms used by current ATM switches to handle congestion and flow control. These mechanisms are [17]:

- 1. Connection Admission Control (CAC);

- 2. Usage Parameter Control (UPC);

- 3. Selective Cell Discarding;

- 4. Traffic Shaping;

- 5. Explicit Forward Congestion Indication (EFCI);

- 6. Resource Management Using Virtual Paths;

- 7. Frame Discard;

- 8. Generic Flow Control (GFC);

- 9. ABR Flow Control.

The above mechanisms reduce congestion in the network by either impeding the traffic that enters the network until the resources become available, or dropping low priority traffic and allow the higher priority traffic instead. The performance of the above mechanisms is greatly affected by the availability of the network resources.

The IP protocol is a routed protocol which can easily scale up. However, routing is not as efficient as the switching process. Accordingly, the current trend is towards integrating the IP routing protocol in the ATM switching networks. There are classical methods which are proposed by the Internet Engineering Task Force (IETF) and label-based IP switching methods proposed by the industry [11]. The classical methods approaches were criticized by the industry because they separated IP on the top of ATM without taking any advantages of the ATM features. This leads to replication of functions and complications of the network management. Examples for the classical methods are the LAN emulation (LANE) and the multiprotocol over ATM (MPOA). In the label-based IP switching methods, companies such as Cisco and Ipsilon are integrating the IP layer with the ATM switching layer. Examples for the label-based IP switching methods are the Tag switching and IP switching.

Recently, the new Gigabit switched Ethernet networks are offering a good alternative by aggressively increasing the bandwidth to the gigabit range. Such a development might lead to the old protocol stack using IPv6, which features QoS, running on the top of gigabit switched Ethernet network at the LAN level. Such high speeds with the next generation IP seems to be an easy migration from the legacy LAN systems.

From the above discussion, it appears that the industry it trending towards switching rather than routing. Switch fabrics are the core of the switching process. Switch fabrics are placed in switching nodes scattered all over the network. The operation of any switching mechanism is directly (or indirectly) influenced by the performance of the switch fabrics. Less efficient switch fabrics result in poor performance of the whole network due to delays and retransmission of the lost traffic. Efficient switch fabrics are characterized by their high throughput and low delay.

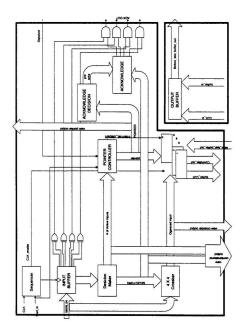

Figure 1.1 depicts a block diagram of a switch fabric. A switch fabric should feature some or all of the following functions:

- · Cell buffering;

- Traffic concentration and multiplexing;

- · Fault tolerance;

- Multicasting and broadcasting;

- · Cell scheduling based on delay priorities;

- · Selective cell discarding based on loss priorities;

- · Congestion monitoring.

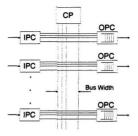

Indeed, building up a switch fabric which features all of the above functions is a challenging objective. Cell buffering is an essential function of the switch fabric, especially in case of congestion. Traffic concentration and multiplexing is a natural IPC = Input Port Controller

OPC = Output Port Controller

Figure 1.1: A block diagram of a switch fabric.

role of a switch fabric. A switch fabric concentrates and multiplexes the arriving traffic onto the OPCs. Fault tolerance has become a very important feature in today's communications equipment where the down time of the network is very expensive. A fault tolerance model is usually associated with the testability level of a system. Because the B-ISDN network will provide services such as video on-demand and video conferencing, multicasting and broadcasting are needed to support these services. Scheduling is necessary for the network to efficiently manipulate the different traffic types that arise from the various service classes. Cell discarding is essential in case of congestion. Switch fabrics drop cells that have lower priorities. For the success of the congestion and flow control mechanisms we discussed earlier, a switch fabric is required to monitor the amount of congestion it suffers and passes this to the network control plane. Hence, the congestion and flow control mechanisms take the proper decisions.

#### 1.3 Motivation

In this dissertation, we provide a comprehensive study of a promising switching architecture called the Balanced Gamma (BG) network. With infinite buffering resources. the BG network has shown good performance in terms of throughput. average cell delay, and reliability. To continue studying the BG network, we further investigate the performance of the network with realistic buffering resources. Realistic buffer resources are comprised of finite queues. We investigate the performance of the network under different payloads containing uniform and non uniform traffic. Uniform random and bursty are the traffic types used. Several simulation experiments are carried out to measure the cell loss, cell average delay, and buffering requirements of the BG network. In addition, we pursued an analytical model under uniform random traffic to verify our simulation results. The performance of the network is compared with both an ideal network and the crossbar network. The performance results of the ideal network are used as an upper bound and it is shown how the BG network relates to that bound. The selection of the crossbar network was essential to prove the efficient performance of the BG network. The crossbar network is recognized by many researchers as a suitable candidate for ATM switching because of its good internal blocking characteristics.

The reliability is a measure of the system's ability to operate without failures during a specified period of time. It also measures the system's ability to tolerate faults. Previously, the reliability models of the BG network were established and showed that the reliability of the BG network outperforms other competitive networks. However, the network reliability model for the BG network was incomplete due its complicated nature. In this dissertation, we introduce a complete network reliability model of the BG network. To emphasize the modularity and scalability of the BG network we decided to carry out a VLSI design for the network. We also wanted to prove that the BG network could be efficiently realized using the current available VLSI technologies. A  $0.35 \ \mu m$  was the technology available to us during the design phase.

#### 1.4 Thesis Organization

The thesis is divided into four parts. In the first part, which can be found in Chapter 2. we provide a survey of the switching architectures meant for broadband communications. The survey sheds light on the different classifications proposed by the researchers to classify the broadband architectures, emphasizing the differences and the similarities amongst them. In the survey, through examples we describe the advantages and the disadvantages of each class. We also discuss the recent techniques used to improve the performance the existing architectures.

In the second part, which can be found in Chapter 3, we briefly introduce the BG network and the previous efforts made to improve and simplify the network routing algorithm. We also emphasize our contribution in simplifying the routing algorithm and the necessary changes that had to be made to the network topology.

In the third part, which can be found in Chapter 4, we investigate the performance of the network with finite buffering resources in both the IPCs and the OPCs. We use both uniform and non uniform traffic loads. The load types we use are the uniform random traffic (URT) and bursty. The parameters used to measure the performance are the cell loss probability, maximum cell delay, average cell delay, input buffer requirements, and output buffer requirements. As we mentioned earlier, our investigation of the BG network will be compared with the performance of both the crossbar and ideal non blocking networks. In the fourth part, which is composed of both Chapters 5 and 6, we introduce the VLSI design and the exact network reliability modelling for the BG network. The VLSI design is carried out using Synopsys CAD tool supported by the Canadian Microelectronics Corporation (CMC). We also use the 0.35  $\mu m$  CMOS technology, also supported by CMC, to achieve a high speed design. Very high speed integrated circuit High Level Description Language (VHDL) is used to describe the design at the Register Transfer Level (RTL). We finally conclude our work in Chapter 7 and give some directions for future open problems in the area.

# Chapter 2 Fast Packet Switching Networks

#### 2.1 Introduction

Previously, the interest in fast packet switching networks was due to their use in fast parallel computing machines. Recently, more attention has been focused on these networks because of the evolving demands of broadband communications. Many classifications of these networks have been reported in the literature. In this chapter we shed some light on these classifications commenting on the similarities and differences amongst them. Our coverage will include the state-of-the-art of the architectures proposed for different subclasses showing the advantages and limitations of each. Since there is a great number of studies available in the literature that can not be covered in this chapter, we try only to focus on those architectures related to the scope of this dissertation.

#### 2.2 Classifications of Packet Switching Networks

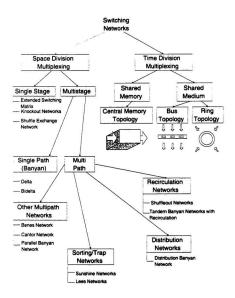

In the literature, many classifications of fast packet switching networks, also called switch fabrics, have been reported [1, 18, 19, 20, 21, 22]. Perhaps the classification model introduced in [1] is the simplest and the most comprehensive, because it has covered most of the well-known architectures. Figure 2.1 depicts the hierarchy of this classification. Similar, but less detailed, classifications are reported in [18] and [19]. Kyas [1] divides switching networks into two main classes, networks that use the time domain for switching, and networks that use the space domain for switching. In time division architectures, the physical resource is multiplexed among the input-output connections, based on discrete time slots. This physical resource can be a shared memory or a shared medium. Ring and bus topologies are typical examples for the shared medium case. In case of space division architectures, the connections rebased on the availability of nonconflicting physical paths within the fabric. Figure 2.1 shows that the family of space division architectures has more subclasses than the time division architectures. We will discuss each one of these subclasses in more detail, stressing on the space division lass because the proposed switch fabric in this discretation belongs to that subclass.

Turner and Yamanaka [20] grouped the architectures, in general. into three major categories: 1) single stage systems, 2) buffered multistage systems, and 3) unbuffered multistage systems. This classification is more directed to multistage interconnection networks (MINs), which is a subclass of the space division class in Kyas's classification model. The reason is conceivably due to the growing interest in these networks. MINs have many advantageous features over other interconnection networks as we will explain later. Turner and Yamanaka inherently assumed that all switch fabrics are space division architectures, whether single stage category. This assumption is acceptable because the traffic is relayed through one single shared medium in time division architectures. The classification also emphasizes the role of buffering in MINs.

Before we discuss the details of these architectures, we give a notation hint. Unless otherwise stated, all the architectures we discuss here are symmetric, i.e. the number of input ports equals the number of output ports and is represented as N.

Figure 2.1: Classification of interconnection networks [1].

Figure 2.2: A basic bus-based switch fabric.

#### 2.3 Time Division Switch Fabrics

#### 2.3.1 Shared Medium Architectures

In fact, the first commercial ATM switch that hit the market was a bus-based architecture (ASX-100) provided by Fore Systems [23]. A typical simple bus-based architecture is shown in Figure 2.2. The IPCs do the ATM layer functions associated with checking for ATM header errors, VCI and VPI translation and synchronization of the arriving data stream to the internal switch timing. To relay the data to the OPCs. IPCs contend for access to the bus using one of a variety of bus-contention techniques. The control port (CP) plays the role of controlling the bus. Each OPC checks the destination addresses in each cell to decide whether to buffer this cell or not. Each OPC contains an internal buffer queue to hold the arriving cells. Obviously, the bus rate should be at least N times as fast as the rate of any individual IPC to alleviate the internal blocking problem, where N is the number of IPCs. The

Figure 2.3: A basic ring-based switch fabric.

way to achieve such a rate is by increasing the width of the bus. For example, a system supporting 16 OC-3 links with internal bus rate of 40 MHz, requires a 64-bit bus width. Notice that as the number of the ports in the system increases, both the number of ports connected to the bus, as well as, the width of the bus must increase. This yields a quadratic growth characteristic, making it uneconomical to implement large switches. Another crucial problem with the bus systems is that as the number of I/O ports increases, the capacitive loading on the lines increases, reducing the internal bus rate.

A simplified ring-based system is depicted in Figure 2.3. The components of the system are similar to those in a bus-based system except that each pair of IPC and OPC are integrated in one unit and served by a ring interface (RJ). The token-ring protocol is the most common protocol running the ring-based networks. Ring systems have the same quadratic growth problem as bus systems. However, they do not suffer from the capacitive loading problem. That is a ring system can run at faster rates than a bus system if both are implemented using the same technology. This leads to smaller ring width than wide bus width in the bus systems.

Based on the above discussion, we conclude that both ring and bus systems have pros and cons. Both have the quadratic growth characteristic as the number of ports increases. Bus systems suffer from capacitance loading but they enjoy the simplicity of implementing multicasting (we will discuss multicasting property later in more detail). On the contrary, ring systems do not suffer from capacitance loading because they are direct point-to-point systems, but implementation of multicasting is more complicated than bus systems. Additionally, in ring systems extra latency is added to pass the cells amongst the RIs. In general, we can state that shared medium systems are not the promising solution for future B-ISDN due to their uneconomical implementation.

#### 2.3.2 Shared Memory Architectures

A multi I/O ports memory can represent a shared memory, also called shared buffer, switch. The IPCs write the arriving cells at the beginning of the switching cycle to the shared memory space and the OPCs read the cells that request them from the shared memory space. The OPCs identify the cells that request them with the aid of address holding queues (AHQs). The number of these queues is equal to the number of OPCs and each queue, which is associated with an OPC, holds the starting addresses of the cells in the shared memory that request this output. One bottleneck we can easily recognize in shared memory switches is that they should be centrally controlled to organize the process of reading/writing amongst I/O ports. Central control is one major obstacle towards building a large switch fabric. The main advantage of pure shared memory systems is that they have the lowest buffering requirements compared to any other switching architectures that have the same number of I/O ports. This is due to the complete sharing of the storage medium of the switch fabric, whereas in other architectures the buffering medium is partially or completely divided amongst system ports in the form of separate queues. Turner *et al.* [20] have discovered that shared memory systems reduce the memory buffering requirements by a factor of 5 to 8 less than shared medium systems. This is a crucial fact when the traffic load has a bursty nature. Another bottleneck is the memory access speed, which also declines as the memory size increases. Obviously, we have 2 N read/write operations have to be carried out in each switching cycle. That is, the memory access speed should be at least 2 N times as fast as any I/O port. This limit is twice the minimum limit of the bus rate in shared medium systems. That means for the previous example of the 16 OC-3 IPCs system, with internal bus rate of 40 MHz, we need a bus width of 128 for a pure shared memory system.

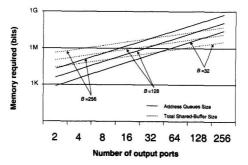

Shared memory systems suffer from similar problems we discussed above for shared medium systems. such as wide bus width and capacitance loading. Also, Yamanaka et al. [2] provided a quantitative discussion about the uneconomical implementation of the shared memory architectures. For a shared memory system of 2N input and output ports and total shared buffer size BN cells, the total memory space required for the AHOs in bits is given by [2]:

AHQs size =

$$PBN^2 \log_2(BN)$$

, (2.1)

where P is the number of service priorities. Figure 2.4 depicts the memory capacity requirements of the AHQs and the shared buffer. For a 32 × 32 switch with 1K cells buffers (when B = 32), no fewer than 320K bits are necessary in total for AHQs. Even with today's technology, this is too large to integrate into the same die

Figure 2.4: Memory capacity of AHQs versus shared buffer [2].

with the control parts of the system. Therefore, external RAMs or FIFOs have to be introduced, which often results in pin number bottleneck. The other interesting fact is that for only one service priority (P = 1), the memory capacity needed for the AHQs is greater than the shared buffer needed to store the cells themselves for network sizes > 32. One can visualize the added complexity if more than one service priority (P > 1) are provided. Several methods have been reported in the literature to manage the operation of the AHQs. A summary of these methods can be found in [24].

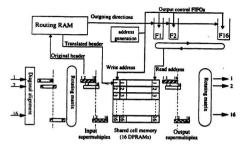

Perhaps, the PRELUDE architecture is the first trial to build a pure shared memory packet switch fabric [25]. The architecture of the 16  $\times$  16 PRELUDE switch is an asynchronous version of the classical synchronous time division (STD) switch used in telephone networks [3]. The switch has gone through many phases of development. As early as 1986, a throughput of 16  $\times$  280 Mb/s was achieved using emitter coupled logic (ECL) technology at the expense of a consumption of 400 W at 5 V. Progress in CMOS technology has led to the implementation of a second version of 24 CMOS chips in 1993 named COM16 [26]. The achieved throughput was 16  $\times$ 155.52 Mb/s while consumption was limited to 40 W at 5 V. The third version is a monochip COM16M that incorporate all the switch functions. Figure 2.5 depicts that architecture.

In [27], the authors reviewed the efforts by a research team at Bell Labs towards building an ATM switch. The group concluded that a pure shared memory switch has become a reality due to the advances in VLSI technology. The first prototype was an 8  $\times$  8 switch fabric that had a 2K cells storage static RAM of 10-nsec access time using a 0.8 BiCMOS technology. The port speed for each I/O line of the switch fabric is 2.5 Gb/s making the total switch capacity of up to 20 Gbps. Further improvements were made to reduce the area of the switch and to increase the capacity up to 160 Gb/s for a

Figure 2.5: COM16M architecture [3].

switch fabric. However, the new modified switch fabric is not a pure shared memory architecture due to the above mentioned limitations, but it is a mixture of shared memory and space division architectures. Every eight consecutive output ports are grouped in one set and served by the initially developed pure  $8 \times 8$  shared memory switch fabric. That is, there exist eight shared memory switch fabrics preceded by an expand-concentrate (EXCON) stage used to distribute the arriving traffic amongst the eight switch fabrics based on the requests made by the arriving cells. Generally, the switch performance is outstanding but the complexity of the switch is very obvious.

Another challenging shared memory switching module is proposed in [28] as well as a switch fabric based on that switching module. It is a clear example of how much complexity one contends with in designing centrally controlled architectures. The switch performance, although not provided, could be outstanding but a closer look at the switch architecture reveals that the cost/performance ratio is very high for this switch fabric. Additionally, the connections between the fabric central controller and different modules suggest that the implementation of the system has to be split over many boards making it a very difficult target for the system to attain high speeds.

It appears, due to the limitations we discussed above, researchers are tending towards hybrid systems. That is, networks are implemented as a mix of both shared memory and space division. Some newly reported examples that describe this trend can be found in [24] and [2]. In the subsequent sections we will discuss different buffering schemes adopted in space division architectures, showing that shared buffering scheme outperforms other buffering schemes.

## 2.4 Space Division Switch Fabrics

As mentioned earlier, the class of space division architectures has a larger collection when compared to the other class of time division architectures. As depicted in Figure 2.1, space division architectures can be divided into two main subclasses; namely single-stage interconnection networks (SINs) and multistage interconnection networks (MINs). Obviously, as both names of the subclasses indicate, architectures that belong to SINs are composed only of one stage, whereas architectures belonging to MINs are composed of multiple stages. In the next sections we discuss each subclass with the provision of some illustrative examples for each.

### 2.4.1 Single Stage Architectures

There are two well-known examples for SINs, the Crossbar (sometimes called Dot Matrix) switch and the Knockout switch. The crossbar switch is depicted in Figure 2.6. An SE is located at each crosspoint and takes one of two states, either cross state or bar state as illustrated in Figure 2.7. The crossbar switch outperforms several other switching networks. The main reason is that the switch does not suffer from any internal blocking. However, it suffers from output blocking because each main

Figure 2.6: A crossbar switch fabric.

Figure 2.7: Crossbar SE states.

output can not accept more than one cell in any switching cycle. Furthermore, the switch has two main disadvantages, which are intensified as the size of the network (N) increases. Firstly, the hardware complexity of the switch is  $O(N^2)$ , which is highly complex when compared to other space division architectures. However, recently Woo [29] has proposed a new design that reduced the switch complexity to  $O(N\sqrt{N})$  by adopting the theory of finite projective planes. Although the new idea has reduced the complexity by a factor of  $\sqrt{N}$ , the hardware complexity of the newly designed SEs to implement the new proposed switching protocol has significantly increased. Secondly, there is lack of fairness amongst the input links of the network. The problem takes place because the internal SEs may give priority to the input ports of the network in a descending or ascending order, depending on the routing decisions made within the SEs. A randomizing mechanism may be used to alleviate the problem but at the expense of larger hardware complexity of the SEs. In [30], under uniform random traffic a theoretical upper limit for a maximum throughput of 0.5858 has been reached for the crossbar switch of infinite size  $(N = \infty)$  and infinite input buffering. Further investigations of the crossbar performance under different buffer strategies can be found in [31, 32]. To conclude, the crossbar switch could be considered the proper choice for the circuit switching technique, but it has lost attraction with the new demands of the broadband packet switching where scenarios of output traffic concentration exist. In [20], a survey of different methods used to improve the crossbar network performance -such as introducing buffering within the crosspoints, having multiple buffer queues at each input port and speeding up the fabric switching- is conducted. Despite the complexity of the crossbar switch, recent implementations that are based on crossbar architecture can be found in [33] and [34].

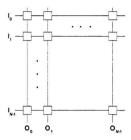

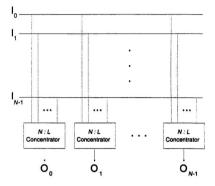

The architecture of the knockout switch is depicted in Figure 2.8. Each output link  $O_i$  is preceded by an N:L concentrator. The concentrator has three main parts,

Figure 2.8: Knockout switch architecture.

1) N address filters, 2) N:L multiplexer, and 3) a buffer space. The address filters pass only the proper cells and reject all other cells that request other output ports. The concentrators confine the arriving cells in a parallel stream of L cells. That is if more than L cells request the same output port, the multiplexer has to reject some of the excess cells, hence the name knockout. Finally, the buffer stores the arriving cells. If L = N, then the switch is called as a *perfect* switch. The reason is that no sort of blocking is experienced in the network. This does not mean that the network has a perfect performance, because the output queuing problem still exists. When the incoming traffic is more bursty, the output buffer needs to be larger to prevent buffer overflow. This problem, which we refer to as the output queuing problem, is a classical queuing theory issue. The network is sometimes called as a "Disjoint-path" network. because there is no intersection amongst input/output connections. Obviously, the knockout switch suffers from the capacitance loading problem discussed earlier for bus and shared memory architectures. In fact, the performance of the knockout switch is very similar to the performance of shared memory architectures because the knockout switch does not suffer from any internal blocking. Note that the complexity of the concentrator grows drastically as N or L increases. In [5], a survey of some tradeoffs to implement the knockout switch is conducted. Throughout this dissertation, we selected both the crossbar and knockout switches to compare their performances with the architecture we propose. We call the version of the knockout switch we use a perfect switch because we set L = N.

At this stage, the different blocking definitions for interconnection networks are worth mentioning. These definitions describe the ability of any switching network to make different permutation connections. Clearly, a nonblocking  $N \times N$  can realize N! permutations. The definitions are as follows [5]:

- A network is said to be nonblocking in the strict sense or strictly nonblocking if it is capable of immediately establishing a connection between any input-output pair without interference from any arbitrary existing connections.

- A network is said to be nonblocking in the wide sense or wide-sense nonblocking if any desired connection between an input-output pair can be established immediately, provided that the existing connections have been inserted using some routing algorithm. If the algorithm is not followed, some attempted connections may get blocked.

- A network is said to be rearrangeable or rearrangeably nonblocking if a desired connection between any input-output pair can be established if one or more of the existing connections are rerouted or rearranged.

- A network is said to be *blocking* if some connection sets can prevent some desired connections from being established.

Although, these definitions are standard and used by many researchers to classify switching architectures, they may provide a misleading picture about the performance of a switching architecture. The fact is, permutation traffic is not the traffic type anticipated in the broadband communication systems. In the broadband traffic scenarios, multicast and broadcast connections, as well as output concentrations, are expected. These traffic loads degrade the performance of many existing switching architectures significantly. A typical example, as we will see later, is the *Batcher bangan* switch.

### 2.4.2 Multistage Interconnection Networks

Recently, the interest in MINs has grown very fast. This is because of two main reasons. Firstly, in MINs no central control is needed to supervise the switching process as the case in shared memory and shared medium systems. That is, the control is distributed amongst the SEs. This property is called self-routing. Secondly, the architectures of these networks are modular making them attractive for VLSI implementation. We first discuss the single path and then the multipath MINS in the next two sections.

#### 2.4.2.1 Single Path MINs

Goke and Lipovski [35] defined that, a network with a unique path from each input to each output is called a *banyan* network. Also, another definition by *Patel* [36] is:

A delta network is an  $a^n \times b^n$  switching network with n stages, consisting of  $a \times b$  crossbar modules. The link pattern between stages is such that there exists a unique path of constant length from any source to any destination.

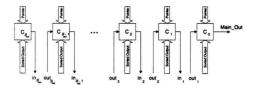

Obviously, the two definitions are close and they are used interchangeably in the literature. In general, we will limit our discussion only for rectangular MINs. A rectangular MIN is of size  $N \times N$ . Several well-known MINs belong to delta class such as banyan [35], baseline [37], reverse baseline [37], omega [38], modified data manipulator [37], and indirect binary n-cube [39]. Some of these networks are shown in Figure 2.9. A rectangular banyan network based on  $2 \times 2$  SEs has  $log_2N$  stages. Each stage has  $\frac{N}{2}$  SEs. In addition to the above mentioned advantages of MINs, banyan networks based on  $2 \times 2$  SEs enjoy the privilege of the simple structure of their SEs. A  $2 \times 2$  SE is very simple to implement because the number of decisions needed to be taken are smaller compared to higher order SEs.

In [40], it has been shown that the performance under uniform random traffic is the same for all banyan configurations. Despite all the advantages, the performance of a banyan network is extremely poor even under simple traffic loads, such as uniform

Figure 2.9: Different banyan network topologies (a) banyan (b) omega (c) baseline.

random traffic. Several methods were proposed to improve the performance but this is achieved at the expense of the network complexity. The most well-known method is using buffers. We will provide a detailed discussion of the buffering techniques in Chapter 4.

#### 2.4.2.2 Multipath MINs

The subclass of multipath MINs has a huge collection, because all single path MINs are inherently included. Later we will provide discussions about some methods used to build multipath MINs from single path ones. Prior to that, we first discuss the structures of standalone multipath MINs.

#### Clos network

The Clos network [41] has been in the research focus for decades. The reason is that it is a nonblocking network with fewer crossconnects than the crossbar switch. This fact made the Clos network a strong candidate for circuit switching networks. However, the Clos switch was also considered for packet switched networks as in Memphis switch built for IBM GF-11 parallel computer [42]. The Clos network is a three-stage network that can be built in asymmetric or symmetric fashion. The first stage of the network has  $r_1$   $(n_1 \times m)$  SEs, the middle stage has m  $(r_1 \times r_2)$ SEs, and the third stage has  $r_2$   $(m \times n_2)$  SEs. In a symmetric clos network  $r_1 = r_2 = r$ and  $n_1 = n_2 = n$ . Figure 2.10 depicts the architecture of a symmetric Clos network. Clos networks can be designed to either operate in rearrangeable nonblocking mode or nonblocking mode. It has been shown for a symmetric Clos network [43]:

- if  $m \ge n$  then the network can operate in rearrangeable nonblocking mode,

- if  $m \ge \lfloor \frac{3n}{2} \rfloor$  then the network can operate in the wide-sense nonblocking mode,

- and if  $m \ge 2n 1$  then the network can operate in the strictly nonblocking

mode.

Obviously, the hardware requirement for a Clos network to operate in a strictly nonblocking mode or wide-sense nonblocking mode is higher than that to operate in a rearrangeable nonblocking mode. Accordingly, a symmetric semi-rearrangeably nonblocking (SRN) Clos network has been provided [44]. Similar to a nonblocking network, an SRN network does not allow any arrangement of the existing connections in order to establish a new connection; however, unlike a nonblocking switch, an SRN switch allows at most one rearrangement to take place when an existing connection is disconnected. Thus the overhead of realizing a new connection under SRN mode of operation is the same as that under the nonblocking operation. However, the overhead of disconnection in the SRN mode is slightly higher than that in the nonblocking mode of operation. Nevertheless, this increase in the overhead is justified because the hardware required for SRN are much lower than those required for nonblocking mode of operation [44]. Recently, a similar approach was proposed for asymmetric Clos networks [45].

In [46], an optical implementation and a performance analysis of a symmetric Clos network were proposed. The performance was studied under uniform random traffic. It was discovered that the performance is acceptable under low traffic loads, but as the load increases the amount of internal buffering increases. One drawback of internal buffering within MINs is the emergence of the so called *out-of-sequence* problem, where cells reach the destinations not in the order they arrived at the input ports. In the literature, there are two schemes used to control switching in Clos network to overcome the out-of-sequence problem but at high cost of complexity. The first scheme, which is used in [45], is called *multirate circuit switching* [47]. In the second is a dynamic routing scheme called *cell switching* [48]. In the former scheme, a path

Figure 2.10: Architecture of the Clos network.

is established for each connection such that the peak capacity is reserved along the path and it is sufficient to carry the connection at any time. Clearly, this scheme will result in low utilization of the network capacity because it does not take advantage of the statistical multiplexing offered by the ATM protocol. But, it provides a guarantee of QoS for each connection. The latter scheme is more dynamic, thus it has better utilization, but extra overhead is needed to overcome the out-of-sequence problem. A recent scheme, which lies in the region between both previous schemes, has been proposed in [49]. Obviously, there are too many concerns that have to be taken into account when designing a switch based on the Clos network. These concerns result in complicated implementation of the switch and high overhead processing time, that makes it difficult to implement switches with large sizes based on the Clos network can be found in [50].

#### Kappa Network

Kappa network (KN) [4] is a variation of the Gamma network (GN) [51]. Both GN and KN were proposed as fault-tolerant MINs. The GN is derived from the modified baseline network. Both KN and GN have  $\log_2 N + 1$  stages, but with different SE sizes. The first stage of the GN has  $N 1 \times 3$  SEs, whereas the first stage of the KN is composed of  $N 1 \times 4$  SEs. Each middle stage in the GN is composed of  $N 3 \times 3$ SEs, whereas it is composed of  $N 4 \times 4$  SEs in the KN. The last stage of the GN has  $N 3 \times 1$  SEs, whereas the last stage of the KN has  $N 4 \times 1$  SEs. Figure 2.11 depicts the architecture of an  $8 \times 8$  Kappa network. If we remove the links denoted by 'A' in Figure 2.11, we obtain the GN. Each link in the Kappa network has an alternate one. In case of a fault, the traffic is directed to the alternate link. Obviously, the family of banyan networks does not have any fault tolerance features. However, there are several methods to improve their fault tolerance properties by replicating the network

Figure 2.11: Architecture of an  $8 \times 8$  Kappa network [4].

Figure 2.12: Architecture of an 8 × 8 BB network [5].

or dilation of the links. We will explain these concepts in the following sections.

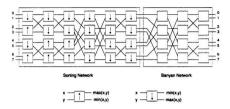

#### Batcher banyan Network

Banyan networks become nonblocking under permutation traffic if the arriving cells are sorted in ascending or descending order; provided that no gaps exist between active inputs [52]. A Batcher banyan (BB) network is composed of a sorting (Batcher) network followed by a banyan network. Figure 2.12 depicts the architecture of an  $8 \times 8$ BB network. The BB network is a multipath network because the path from any source to any destination depends on the sorting order in the sorting network. The sorting network [53] has  $\frac{49\pi_2 + 1}{2} \log_2 N$  stages, with N/2 sorting elements in each stage. In total,  $\frac{N}{2} (\frac{49\pi_2 + 1}{2} \log_2 N)$  sorting elements and  $\frac{N}{2} \log_2 N$  SEs exist in the BB network. Obviously, the BB network has less crosspoints for large N if compared with the crossbar switch, however it is an expensive alternative to improve the performance of the banyan network. Despite that complexity, several switches that have been reported in the literature are based on the BB network [5]: Starlite switch, Sunshine switch, 3-phase BB switch, and 2-phase BB switch. Although the performance of the BB network is outstanding (100% throughput) under permutation traffic, it has poor performance under other traffic loads which are closer to the real ATM traffic. This can be rationalized due to the limited performance of the banyan network which constitutes the output part of the BB network. It is worth mentioning at this step that permutation traffic, which is used as the basis for defining the blocking properties of the different network architectures, does not really represent the real ATM traffic which is expected to be bursty and have multicast properties [54]. That is why it was reported in [55] that the BB network is more popular in the research communities than for commercial applications.

#### Extended Banyan Networks

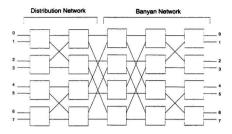

Beneš [43] first introduced the concept of extended networks, hence these networks are called Beneš networks. The Beneš network is another example for a multipath network obtained from the banyan network. The network has  $2log_2N-1$  stages, and is composed of two halves. Each half is a mirror image of the other as shown in Figure 2.13. The first half, which is composed of the first  $log_2N - 1$  stages, is called the *distribution* network and the second half, which is composed of the last  $log_2N$  stages, is called the *routing* network. Notice that we can still obtain a multipath network even with a distribution network that has number of stages less than  $log_2N - 1$ . However, such networks have poorer nonblocking properties when compared to the generic Beneš network. Beneš has proved that such networks are rearrangeably nonblocking [43].

Benes networks suffer from two drawbacks. Firstly, the control is centralized in the distribution network, which leads to losing the distributed control advantage that MINs enjoy. Secondly, the architecture does not overcome the out-of-sequence problem encountered if the SEs contain buffers because it is a multipath architecture. Recently De Marco and Pattavina [56] have defined a new distributed control algorithm, which is suitable for ATM cell switching, to control the switching operation in

Figure 2.13: The architecture of an  $8 \times 8$  Benes network.

the extended banyan network. Despite this improvement, the complexity of the SEs in the distribution network increases drastically. This is caused by the complicated algorithm implemented in each SE. The functions of that algorithm include gathering information about the buffers in the same pool (see [56]), manipulating this information, and then taking the routing decision. Additionally, the output port controllers have to guarantee the sequence of the arriving cells because this algorithm does not obviate the out of sequence problem if the network is internally buffered. This scenario has to be repeated in every switching cycle. Indeed, the extended banyan network is attractive for circuit switching systems, as the case for Clos network, but is less efficient view nused in packet switching systems.

#### **Dilated Networks**

A dilated banyan network has the same topology and the same number of SEs as the banyan network except that each link in the network is replicated many times. For example, the building SE for a 2-dilated banyan is shown in Figure 2.14. The up-

Figure 2.14: A switching element in a 2-dilated banyan network.

per/lower inputs(outputs) are connected to the same SE in the previous(next) stage. Importantly, we should not mix the network dilation with increasing the internal bandwidth of the network. The latter is similar to using wide bus for speeding up, discussed earlier in section 2.3, whereas in the former the number of ports per SE is increased. In fact, both concepts could be adopted in the same architecture. Note that the concept of dilation is not restricted only to the banyan networks, but indeed, it can be adopted with any other MIN architecture.

In the literature, the idea of dilated networks has been studied [57, 58]. As would be expected, The performance is shown to be better than the regular banyan network. That is because of the increased number of paths that a cell can go through. In [59], Alimuddin *et al.* have discovered that using fixed dilation, i.e., using the same dilation degree, for all SEs result in underutilization in the initial stages and overutilization in the last stages. They have proposed a structure where the degree of dilation is not the same in all stages. It increases towards the last stages of the network. That way

Figure 2.15: The tandem architecure.

scenarios of output port contention can be relaxed with the availability of more paths. Finally, we should be aware of the increased hardware complexity when incorporating dilation.

## Tandem Networks

The first tandem architecture was first introduced by Tobagi *et al.* [60], and it was based on the banyan network. A tandem structure is composed of K fabrics connected in cascade as shown in 2.15. Each fabric can belong to any of the switching architectures we discussed above. The arriving cells are switched through fabric 1. If an internal conflict exists, some cells win contention and the others are routed to the other unused output links. After the first fabric, cells are checked and those have not reached their destinations are sent to fabric 2 and the other successful cells are received by the output ports. The process is repeated till reaching fabric K and then unsuccessful cells are dropped, or in some other architectures they could be recirculated back. Note that switching is taking place in all fabrics simultaneously, which may lead to the out-of-sequence problem. For example, if a cell loses contention in consecutive stages and the cells arriving later in the same logical connection win contention, then cells will arrive out-of-sequence at the destination.

The performance of the tandem banyan is definitely better than an ordinary banyan network as K increases. However, a tandem architecture is a very expensive solution especially if a low cell loss ratio and minimum number of out-of-sequence cells are two objectives. Because these two objectives translate to higher K and a complicated resequencing mechanism at the main output ports controllers of the network. The authors in [60] reported that, on average, the tandem banyan network of size N = 32 with recirculation needs at least 4 fabrics under uniform random traffic. Parallel and Parallel-Like Networks