# A VLSI SYNTHESIS OF A REED-SOLOMON PROCESSOR FOR DIGITAL COMMUNICATION SYSTEMS

CENTRE FOR NEWFOUNDLAND STUDIES

TOTAL OF 10 PAGES ONLY MAY BE XEROXED

(Without Author's Permission)

PHILEMON JOHN CHOSE

#### INFORMATION TO USERS

This manuscript has been reproduced from the microfilm master. UMI films the text directly from the original or copy submitted. Thus, some thesis and dissertation copies are in typewriter face, while others may be from any type of computer printer.

The quality of this reproduction is dependent upon the quality of the copy submitted. Broken or indistinct print, colored or poor quality illustrations and photographs, print bleedthrough, substandard margins, and improper alignment can adversely affect reproduction.

In the unlikely event that the author did not send UMI a complete manuscript and there are missing pages, these will be noted. Also, if unauthorized copyright material had to be removed, a note will indicate the deletion.

Oversize materials (e.g., maps, drawings, charts) are reproduced by sectioning the original, beginning at the upper left-hand corner and continuing from left to right in equal sections with small overlaps.

Photographs included in the original manuscript have been reproduced xerographically in this copy. Higher quality  $6^{\circ} \times 9^{\circ}$  black and white photographic prints are available for any photographs or illustrations appearing in this copy for an additional charge. Contact UMI directly to order.

> Bell & Howell Information and Learning 300 North Zeeb Road, Ann Arbor, MI 48106-1346 USA 800-521-0600

National Library of Canada

> Acquisitions and Bibliographic Services 395 Wellington Street Ottawa ON K1A 0N4

Bibliothèque nationale du Canada

Acquisitions et services bibliographiques 395, rue Wellington Ottawa ON K1A 0N4

Your file Votre rélérence

Our file Notre rétérance

The author has granted a nonexclusive licence allowing the National Library of Canada to reproduce, loan, distribute or sell copies of this thesis in microform, paper or electronic formats.

vendre des copies de cette thèse sous la forme de microfiche/film, de reproduction sur papier ou sur format électronique.

The author retains ownership of the copyright in this thesis. Neither the thesis nor substantial extracts from it may be printed or otherwise reproduced without the author's permission.

L'auteur conserve la propriété du droit d'auteur qui protège cette thèse. Ni la thèse ni des extraits substantiels de celle-ci ne doivent être imprimés ou autrement reproduits sans son autorisation.

L'auteur a accordé une licence non

Bibliothèque nationale du Canada de

reproduire, prêter, distribuer ou

exclusive permettant à la

0-612-54889-9

# A VLSI Synthesis of a Reed-Solomon Processor for Digital Communication Systems

By

©Philemon John Chose, B.Eng.

A thesis submitted to the School of Graduate Studies in partial fulfillment of the requirements for the degree of Master of Engineering

Faculty of Engineering and Applied Science

Memorial University of Newfoundland

July, 1998

St. John's Newfoundland Canada

#### Abstract

The Reed-Solomon codes have been widely used in digital communication systems such as computer networks, satellites, VCRs, mobile communications and highdefinition television (HDTV), in order to protect digital data against erasures, random and burst errors during transmission. Since the encoding and decoding algorithms for such codes are computationally intensive, special purpose hardware implementations are often required to meet the real time requirements.

One motivation for this thesis is to investigate and introduce reconfigurable Galois field arithmetic structures which exploit the symmetric properties of available architectures. Another is to design and implement an RS encoder/decoder ASIC which can support a wide family of RS codes.

An m-programmable Galois field multiplier which uses the standard basis representation of the elements is first introduced. It is then demonstrated that the exponentiator can be used to implement a fast inverter which outperforms the available inverters in  $GF(2^m)$ . Using these basic structures, an ASIC design and synthesis of a reconfigurable Reed-Solomon encoder/decoder processor which implements a large family of RS codes is proposed. The design is parameterized in terms of the block length n, Galois field symbol size m, and error correction capability t for the various RS codes. The design has been captured using the VHDL hardware description language and mapped onto CMOS standard cells available in the 0.8- $\mu$ m BiCMOS design kits for Cadence and Synopsys tools. The experimental chip contains 218,206 logic gates and supports values of the Galois field symbol size m = 3, 4, 5, 6, 7, 8 and error correction capability t = 1, 2, 3, ..., 16. Thus, the block length n is variable from T to 255. Error correction t and Galois field symbol size

m are pin-selectable.

Since low design complexity and high throughput are desired in the VLSI chip, the algebraic decoding technique has been investigated instead of the time or transform domain. The encoder uses a self-reciprocal generator polynomial which structures the codewords in a systematic form. At the beginning of the decoding process, received words are initially stored in the first-in-first-out (FIFO) buffer as they enter the syndrome module. The Berlekemp-Massey algorithm is used to determine both the error locator and error evaluator polynomials. The Chien Search and Forney's algorithms operate sequentially to solve for the error locations and error values respectively. The error values are exclusive or-ed with the buffered messages in order to correct the errors, as the processed data leave the chip.

# Acknowledgements

I would like to take this opportunity to thank my supervisors Dr. P. Gillard, Dr. R. Venkatesan and Dr. R. Donnelly whose constant encouragement and suggestions kept me on the right track.

The enthusiastic support from Dr. J.J. Sharp, Associate Dean of Graduate Studies and Research, and Dr. R. Seshadri, Dean of Engineering and Applied Science, is greatly appreciated. I would also like to thank Mr. Michael Rendell of the Computer Science Department and Mr. Brent Veitch of the Canadian Microelectronics Corporation for their help with the Synopsys and Cadence suite of software tools.

The financial support of the Faculty of Engineering and Applied Science of Memorial University of Newfoundland, and Natural Sciences and Engineering Research Council of Canada is gratefully acknowledged.

I am especially indebted to my wife, Michele, for her love and emotional support during my graduate studies.

# Contents

| Abstract                                                        |     |      |   | i    |

|-----------------------------------------------------------------|-----|------|---|------|

| Acknowledgments                                                 |     |      |   | iii  |

| Table of Contents                                               |     |      |   | iv   |

| List of Figures                                                 |     |      |   | vi   |

| List of Tables                                                  |     |      |   | viii |

| List of Symbols and Acronyms                                    |     |      |   | ix   |

| Introduction                                                    |     |      |   | 1    |

| 1.1 Statement of the Problem                                    |     |      | ě | 1    |

| 1.2 VLSI Architectures for Implementing Galois Field Arithmetic |     |      |   | 3    |

| 1.2.1 An Overview of Galois Field Arithmetic                    |     |      |   | 3    |

| 1.2.2 Multipliers                                               |     |      |   | 6    |

| 1.2.3 Dividers and Inverters                                    |     |      |   | 10   |

| 1.2.4 Exponentiators                                            |     |      | × | 13   |

| 1.2.5 Summary                                                   |     |      |   | 16   |

| 1.3 Scope of the Work                                           | 3 8 | 8 10 |   | 16   |

|   | 1.4 | Organization of the Thesis                      | 17 |

|---|-----|-------------------------------------------------|----|

| 2 | The | eoretical Background on Reed-Solomon Codes      | 19 |

|   | 2.1 | General RS Code Definition                      | 19 |

|   | 2.2 | Encoding                                        | 21 |

|   | 2.3 | Algebraic Decoding                              | 23 |

|   |     | 2.3.1 Berlekamp-Massey Algorithm                | 27 |

|   |     | 2.3.2 Euclid's Algorithm                        | 29 |

|   |     | 2.3.3 Chien Search                              | 31 |

|   |     | 2.3.4 The Forney Algorithm                      | 31 |

|   | 2.4 | Time-Domain Decoding                            | 34 |

|   |     | 2.4.1 Error Locator and Evaluator Polynomials   | 34 |

|   |     | 2.4.2 Error Evaluation                          | 34 |

|   | 2.5 | Error Correction                                | 35 |

|   | 2.6 | Algebraic vs. Time-Domain Decoding Algorithms   | 35 |

|   | 2.7 | RS Encoder/Decoder Architectures                | 36 |

|   | 2.8 | Summary                                         | 41 |

| 3 | Pro | posed VLSI Arithmetic Architectures             | 42 |

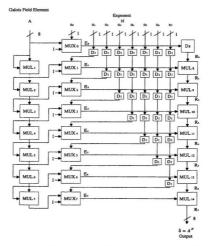

|   | 3.1 | m-Programmable Galois Field Multiplier          | 43 |

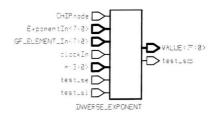

|   | 3.2 | m-Programmable Exponentiator/Inverter           | 58 |

|   | 3.3 | Discussion and Summary                          | 67 |

| 1 | Syn | thesis of the Reed-Solomon Encoder/Decoder ASIC | 68 |

|   | 4.1 | Design Flow, Functional Verification and Test   | 68 |

|   | 12  | Chin Architecture                               | 71 |

|   | 4.0  |        |           |         |      |      |      |      |     |    | • | • | • |      | • | • | • | • | • |     |

|---|------|--------|-----------|---------|------|------|------|------|-----|----|---|---|---|------|---|---|---|---|---|-----|

|   |      | 4.3.1  | Encoder   |         |      |      |      |      |     |    |   |   |   |      |   |   |   |   |   | 7   |

|   |      | 4.3.2  | Syndron   | ne      |      |      |      |      |     |    |   |   |   |      |   |   |   |   |   | 7   |

|   |      | 4.3.3  | Berleka   | mp      |      |      |      |      |     |    |   |   |   | <br> |   |   |   |   |   | 8   |

|   |      | 4.3.4  | Error M   | agnitu  | de E | val  | uati | on   |     |    |   |   |   |      |   |   |   |   |   | 8   |

|   |      |        | 4.3.4.1   | The     | Chie | n Se | earc | h.   |     |    |   |   |   | <br> |   |   |   |   |   | 8   |

|   |      |        | 4.3.4.2   | The l   | Forn | ey A | Algo | rit  | hm  | ١. |   |   |   | <br> |   |   |   |   |   | 8   |

|   |      | 4.3.5  | Error C   | orrecti | on a | nd 1 | Veri | fica | tic | n  |   |   |   | <br> |   | ٠ |   |   |   | 9:  |

|   |      | 4.3.6  | First-In- | First-  | Out  | Buf  | fer  |      |     |    |   |   |   | <br> |   |   |   |   |   | 94  |

|   |      | 4.3.7  | Finite S  | tate M  | achi | ne   |      |      |     |    |   |   |   |      |   |   |   |   |   | 96  |

|   | 4.4  | Testin | g and Re  | sults . |      |      |      |      |     |    |   |   |   |      |   |   |   |   |   | 10  |

|   | 4.5  | Discus | ssion and | Summ    | ary  |      |      |      |     |    |   |   |   |      |   |   |   |   |   | 108 |

| 5 | Con  | clusio | n and F   | iture   | Wor  | k    |      |      |     |    |   |   |   |      |   |   |   |   |   | 111 |

|   | 5.1  | Galois | Field Ar  | ithmet  | ic A | rchi | tect | ure  | s . |    |   |   |   |      |   |   |   |   |   | 111 |

|   | 5.2  | VLSI   | Reed-Solo | mon E   | nco  | der/ | De   | cod  | er  |    |   |   |   |      |   |   |   |   |   | 112 |

|   | 5.3  | Future | Work .    |         |      |      |      |      |     |    |   |   |   |      |   |   |   |   |   | 114 |

|   | Refe | erence | s         |         |      |      |      |      |     |    |   |   |   |      |   |   |   |   |   | 116 |

# List of Figures

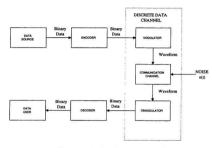

| 2.1 | A Digital Communication System                                      | 2(  |

|-----|---------------------------------------------------------------------|-----|

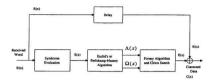

| 2.2 | Algebraic Decoder                                                   | 33  |

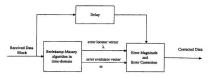

| 2.3 | Time-Domain Decoder                                                 | 1   |

| 3.1 | A Parallel-In-Parallel-Out Multiplier for $GF(2^8)$                 |     |

| 3.2 | Symbolic Architecture of the Programmable Multiplier                | i   |

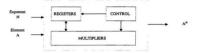

| 3.3 | A General Exponentiation Architecture                               | ij  |

| 3.4 | Exponentiation/Inverse Architecture for $GF(2^8)$                   | 52  |

| 3.5 | Symbolic Architecture of the Programmable Exponentiator/Inverter $$ | 14  |

| 4.1 | Design Flow                                                         | 9   |

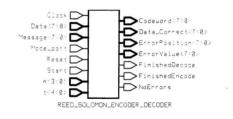

| 4.2 | Symbolic diagram of the RS Encoder/Decoder                          | 573 |

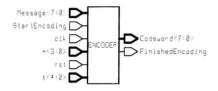

| 4.3 | RS Encoder                                                          | 6   |

| 4.4 | Symbolic diagram of the RS encoder                                  | 7   |

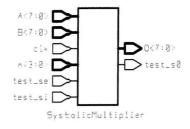

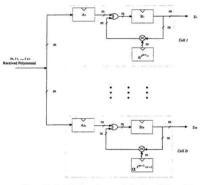

| 4.5 | Systolic Array to compute Syndrome Polynomial                       | 9   |

| 4.6 | Symbolic diagram of the Syndrome Module                             | 1   |

| 4.7 | Symbolic diagram of the Berlekamp Module                            | 5   |

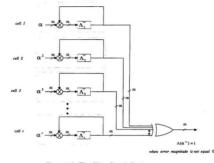

| 4.8 | The Chien Search Hardware                                           | 7   |

| 4.9 | Error Evaluation Polynomial Circuit                                 | 9   |

|     |                                                                     |     |

| 4.10 | Derivative Circuit                                            |  |  | 90  |

|------|---------------------------------------------------------------|--|--|-----|

| 4.11 | Block Diagram of the Error Magnitude Evaluation               |  |  | 91  |

| 4.12 | Symbolic diagram of the Error Magnitude Evaluation $ \ldots $ |  |  | 93  |

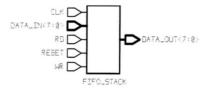

| 4.13 | Symbolic diagram of FIFO                                      |  |  | 95  |

| 4.14 | RS Encoder/Decoder Finite State Machine                       |  |  | 98  |

| 4.15 | Symbolic diagram of the Finite State Machine                  |  |  | 100 |

| 4.16 | Gate Level Simulations of the RS Encoder                      |  |  | 103 |

| 4.17 | Gate Level Simulations of the Syndrome Module                 |  |  | 104 |

| 4.18 | Gate Level Simulations of the overall RS ASIC (Encoding)      |  |  | 105 |

| 4.19 | Gate Level Simulations of the overall RS ASIC (Decoding)      |  |  | 106 |

| 4.20 | Gate Level Simulations of the RS ASIC (Decoding Failure)      |  |  | 107 |

# List of Tables

| 1.1  | Elements generated by $P(x) = 1 + x + x^3 \dots \dots$              | 6   |

|------|---------------------------------------------------------------------|-----|

| 3.1  | Comparison of the programmable Unpipelined and Pipelined Multiplier | 58  |

| 3.2  | Features of the programmable Exponentiator/Inverter                 | 63  |

| 3.3  | Comparison of Exponentiator/Inverter with other Inverters for fixed |     |

|      | m                                                                   | 66  |

| 4.1  | RS Encoder/Decoder Characteristics                                  | 72  |

| 4.2  | RS Encoder/Decoder I/O Pins                                         | 74  |

| 4.3  | Encoder I/O Pins                                                    | 78  |

| 4.4  | Syndrome I/O Pins                                                   | 82  |

| 4.5  | Berlekamp Module I/O Pins                                           | 86  |

| 4.6  | I/O Pins of the Error Magnitude Evaluation                          | 92  |

| 4.7  | I/O Pins of the FIFO Module                                         | 94  |

| 4.8  | I/O Pins of the FSM Module                                          | 99  |

| 4.9  | RS Encoder/Decoder Data Rates                                       | 109 |

| 4.10 | RS Encoder/Decoder Modules and Equivalent Gate Count                | 10  |

| 5.1  | Projected RS Encoder/Decoder Data Rates                             | 15  |

# List of Symbols and Acronyms

ASIC Application specific integrated circuit

BCH Bose-Chaudhuri-Hocquenghem

BiCMOS Bipolar complementary metal oxide semiconductor

BJT Bipolar junction transistor

C(x)Codeword polynomial

CAD Computer aided design

CMOS Complementary metal oxide semiconductor

CMC Canadian Microelectronics Corporation

CODEC Coding and decoding

DDA Division-and-accumulation Error polynomial

FEC Forward error correction First-in first-out

FSM Finite state machine

GFGalois field

E(x)

FIFO

G(x)Generator polynomial

HDTV High-definition television

I/O Input output

IC Integrated circuit k Number of message symbols

m Symbol size of a Galois field element

M(x) Message polynomial

MUX Multiplexer

n Code length of an RS code

NASA National Aeronautics and Space Administration

NMOS n - type metal oxide semiconductor

p(x) Primitive polynomial

ROM Read-only memory

RS Reed-Solomon

RTL Register transfer level

S(x) Syndrome polynomial

t Error correcting capability of an RS code

VHDL Very high speed integrated circuit hardware description language

VLSI Very large scale integration

$\Lambda(x)$  Error locator polynomial

$\Lambda'(x)$  First derivative of the error locator polynomial

$\sigma(x)$  Error locator polynomial

$\Omega(x)$  Error locator polynomial

# Chapter 1

# Introduction

#### 1.1 Statement of the Problem

The Reed Solomon (RS) codes are widely used in digital communication systems to increase the reliability and efficiency of the communication channel. They work in finite or Galois field arithmetic and have the ability to efficiently protect digital data against erasures, random, and burst errors during transmission. The interest in the RS codes was primarily theoretical until the concept of concatenated coding which uses a convolutional code/RS code channel system, was formulated and first introduced in [1]. Their success is now reflected in modern day digital audio or compact discs, computer networks, deep space telecommunication systems, spread-spectrum systems, computer memories, VCRs and high-definition television (HDTV) applications [2][3][4].

Since the encoding and decoding algorithms for such codes are computationally intensive, special purpose hardware implementations are often required to meet the real-time processing requirements. The choice of a specific RS code depends on the characteristics of the communication channel. As such, RS encoders and decoders are traditionally designed with fixed values of the error correction capability t, block

length n and symbol size m. The reason for choosing fixed design parameters is that the exponentiator, multiplier, divider and inverter have different designs for different values of m [2][5][6]. Such an approach is evidently inflexible and hence inefficient because the system has to be redesigned if the channel characteristics ultimately change. Moreover, the design complexity increases with the error correction capability of the code, thus making it impractical to implement the system using off-the-shelf discrete integrated circuit components. However, rapid advances in VLSI technologies may offer attractive solutions because of higher reliability, better performance, smaller area, lighter weight and lower power consumption [7].

Hence, there is a direct need for fast finite field arithmetic circuits which operate in  $GF(2^m)$ , where m is variable. The ability to operate with different symbol sizes of m-bits has been a limiting factor in past efforts to implement universal and possibly reconfigurable RS hardware. If such arithmetic circuits could be developed, it would be possible to design highly efficient single chip encoders/decoders whose total design cost is amortized over a wide application base. Hence, the motivations for this thesis are:

- to investigate and introduce programmable Galois field arithmetic structures

which exploit the symmetric properties of available architectures. It appears that

very little work has been done in the literature to develop reconfigurable hardware

which can operate in finite fields.

- (2) to design and implement an RS encoder/decoder ASIC which can support a wide family of RS codes whose symbol size m and error correction capability t can be varied directly in hardware. Such a general-purpose ASIC would be suitable for a wide variety of digital communication systems which require different RS codes.

The choice of m and t depends on the application and is usually based on the overall correction performance and throughput of the code. The specific Galois field symbol size m=8 has been standardized by the European Space Agency and the National Aeronautics and Space Administration for satellite communication [2]. The error correction circuits for advanced train control systems, mobile radio systems, magnetic recording systems, data communications and digital signal processing based modems use m=5 [2][5].

## 1.2 VLSI Architectures for Implementing Galois Field Arithmetic

The following subsections present an overview of Galois field arithmetic and a literature review of the various arithmetic operations.

## 1.2.1 An Overview of Galois Field Arithmetic

Recently, Galois fields or finite fields have received great attention because of their widespread applications in error control coding using linear block codes. They have also been extensively used in digital signal processing, pseudo-random number generation, encryption and decryption protocols in cryptography. The design of efficient multiplier, inverter and exponentiation circuits for Galois field arithmetic is needed for these applications. These circuits should have low complexity, short computation delay and low latency when used in high-performance systems [2].

A finite field or a Galois field designated GF(p), is a finite set of elements which has defined rules for arithmetic. These rules are not algebraically different from those used in arithmetic with ordinary numbers except that there is only a finite set of elements involved. All finite fields have the following properties:

- Multiplication and addition are the two operations defined for combining the elements.

- The result of adding or multiplying two elements is always a third element contained in the field.

- The field always contains the multiplicative identity element 1 and the additive identity element 0 such that a + 0 = a and a · 1 = a for any element a.

- 4. Every element a has an additive inverse element (-a) and a multiplicative inverse element a<sup>-1</sup> such that a+(-a) = 0 and a·a<sup>-1</sup> = 1. The existence of these elements permits subtraction and division to be performed.

- 5. The associative [a + (b + c) = (a + b) + c and a · (b · c) = (a · b) · c], commutative [a + b = b + a and a · b = b · a], and distributive [a · (b + c) = a · b + a · c] laws apply.

$GF(p^n)$  is an extension field of the ground field GF(p), where m is a positive integer. For p = 2,  $GF(2^m)$  is an extension field of the ground field GF(2) of two elements  $\{0,1\}$ .  $GF(2^m)$  is a vector space of dimension m over GF(2) and hence is represented using a basis of m linearly independent vectors. The finite field  $GF(2^m)$ contains  $2^m - 1$  non-zero elements. All finite fields contain a zero element and an element, called a generator or primitive element, such that every non-zero element in the field can be expressed as a power of this element.

In order to introduce the mathematical concepts of the trace and dual basis, the following definitions are necessary [8][9].

Definition 1: The trace of an element  $\beta$  which belongs to  $GF(2^m)$  is defined as

$$Tr(\beta) = \sum_{k=0}^{m-1} (\beta)^{2^k}$$

(1.1)

Definition 2: A basis  $\{\mu_i\}$  in  $GF(2^m)$  is a set of m linearly independent elements

in  $GF(2^m)$ , where  $0 \le j \le m-1$ .

Definition 3: Two bases  $\{\mu_j\}$  and  $\{\lambda_k\}$  are the dual of one another if

$$Tr(\mu_j \lambda_k) = 1$$

, if  $j = k$

= 0, if  $j \neq k$  (1.2)

where  $0 \le j \le m-1$  and  $0 \le k \le m-1$ .

The elements of  $GF(2^m)$  are usually expressed as powers of the primitive element  $\alpha$ , where  $\alpha$  is defined as the root of the primitive polynomial  $P(x) = x^m + f_{m-1}x^{m-1} + f_{m-2}x^{m-2} \dots + f_1x + 1$  where  $f_i \in \{0,1\}$ . Each element x of  $GF(2^m)$  can also be written in [8][9][10]

- the standard basis as  $z = a_{m-1}\alpha^{m-1} + ... + a_2\alpha^2 + a_1\alpha^1 + a_0$ .

- $\bullet$  the normal basis as  $z=a_{m-1}\alpha^{2^{m-1}}+\ldots+a_2\alpha^{2^2}+a_1\alpha^{2^1}+a_0\alpha$

- the dual basis  $\lambda_k$  as  $z = \sum_{k=0}^{m-1} z_k \lambda_k = \sum_{k=0}^{m-1} Tr(z\mu_k) \lambda_k$ . where

$a_i \in GF(2)$  and  $z_k = Tr(z\mu_k)$  is the k-th coefficient of the dual basis.

The standard basis is commonly used in implementing algebraic Reed-Solomon decoders in hardware. Since multiplication is the most dominant arithmetic operation, the standard basis multiplier is often preferred for its lowest design complexition of the total and dual based multipliers [6][11]. It does not require basis conversion and thus can be more easily matched to any input/output system.

As an example, the power, polynomial and 3-tuple representations of the Galois field elements generated by the primitive polynomial  $P(x) = 1 + x + x^3$  are tabulated in Table 1.1. The non-zero elements are generated using a 3-stage linear feedback shift register initialized to 001, with taps defined by the coefficients of the primitive polynomial P(x).

| Power                            | Polynomial                       | 3-Tuple |

|----------------------------------|----------------------------------|---------|

| 0                                | 0                                | 000     |

| $\alpha^0$                       | $\alpha^0$                       | 001     |

| $\alpha^1$ $\alpha^2$ $\alpha^3$ | $\alpha^1$                       | 010     |

| $\alpha^2$                       | $\alpha^2$                       | 100     |

| $\alpha^3$                       | $\alpha^1 + \alpha^0$            | 011     |

| $\alpha^4$                       | $\alpha^2 + \alpha^1$            | 110     |

| $\alpha^5$ $\alpha^6$            | $\alpha^2 + \alpha^1 + \alpha^0$ | 111     |

| $\alpha^6$                       | $\alpha^2 + \alpha^0$            | 101     |

| $\alpha^7$                       | $\alpha^0$                       | 001     |

Table 1.1: Elements generated by  $P(x) = 1 + x + x^3$

```

Examples: \alpha^1 + \alpha^2 = \alpha^4

Multiplication: \alpha^2 \cdot \alpha^3 = \alpha^5

Division: \frac{\alpha^2}{\alpha^2} = \alpha^3 = \alpha^5

Exponentiation: (\alpha^0)^3 = \alpha^{10} = \alpha^4

Inversion: \frac{\alpha^0}{\alpha^2} = \alpha^{-2} = \alpha^{7-2} = \alpha^5

since \alpha^7 = \alpha^0 = 1

```

Addition and subtraction in finite fields are relatively straightforward, but multiplication, division, exponentiation and inversion are not. Using a symbol size m, addition and subtraction can be realized using m-bit exclusive-or gates. However, since the more complex operations are extensively used in RS encoding and decoding algorithms, the development of their hardware structures have received considerable attention.

## 1.2.2 Multipliers

For arbitrary elements  $A(x) = \sum_{k=0}^{m-1} a_k x^k$ ,  $B(x) = \sum_{k=0}^{m-1} b_k x^k$  in  $GF(2^m)$ , and the primitive polynomial  $P(x) = \sum_{k=0}^{m-1} p_k x^k$ , the product C(x) of A(x) and B(x) is

given by

$$C(x) = A(x)B(x) \mod P(x)$$

$$= \left[\sum_{a=-1}^{n} A(x)b_{x}x^{b}\right] \mod P(x)$$

$$= \left(...(A(x)b_{m-1}x + A(x)b_{m-2})x + ...)x + A(x)b_{0}$$

$$= c_{m-1}x^{m-1} + c_{m-2}x^{m-2} + ... + c_{1}x + c_{0}$$

(1.3)

A direct implementation of multiplication by combinational logic was proposed by Bartee and Schneider [12]. A canonical basis is used to represent the elements of the field. Depending on the primitive element, this implementation requires as many as  $(m^3 - m)$  two-input adders over GF(2). This approach has a high circuit complexity and also lacks regularity suited for full custom VLSI designs.

A cellular array multiplier was originally conceived by Laws and Rushforth in 1971 [13]. The array requires approximately 2m gate delays, a considerable improvement over the traditional linear feedback register type multiplier which computes the desired product sequentially in m clock cycles. A simple parity check circuit is incorporated in the design.

In 1984, Yeh et al [14] presented systolic multipliers for performing multiplication of arbitrary elements in  $GF(2^m)$  in O(m) time and area suitable for VLSI implementation. In the design, the elements in the field are represented in the conventional manner. The throughput rate for the serial-in serial-out one-dimensional systolic array is m clock cycles and the parallel-in parallel-out two-dimensional systolic array, one clock cycle. Both designs have a latency of 2m clock cycles.

In 1985, Wang et al [10] developed a pipeline structure to implement the multiplication algorithm proposed by Massey and Omura for Galois fields based on the normal basis representation. By taking advantage of the squaring property of the normal basis representation, the same pipeline structure is reconfigured to compute the inverse elements in  $GF(2^m)$ . The throughput rate for the multiplier is one product per clock cycle after an initial delay of m clock cycles. Since the design is dependent on the primitive polynomial used to generate the field elements, the number of XOR gates in the product function increases enormously for large m. Hence, the pipeline structure is only practical for small m.

In 1986, Scott et al [15] presented a bit-slice architecture of a serial-in serial-our multiplier well suited for VLSI implementation. The multiplier has a latency of m clock cycles and yields a computation time and implementation area of O(m). It is shown that the architecture is attractive for use in data encryption systems where data are segmented into long blocks to achieve high security and maximum throughput.

A parallel-in parallel-out systolic array and a serial-in serial-out systolic array proposed for fast multiplication in the finite fields  $GF(2^m)$  with the standard basis representation were presented by Wang and Lin in 1991 [11]. The architectures are regular, concurrent and have unidirectional data flow. A system with unidirectional data flow is highly desirable when designing high-speed VLSI systems. It is further shown that the proposed parallel implementation can more easily incorporate fault-tolerance compared to previously published designs. The serial-in serial-out array only requires one control signal instead of two as in [14]. If the input data pass in continuously, the parallel-in parallel-out array yields output results at a rate of one output per clock cycle after a latency of 3m cycles. It is worth noting that the minimum clock period is governed by the propagation delay of an AND gate in series with an XOR gate. All the operations of each basic cell are pipelined in such a manner that each cell performs a small fraction of the multiplication and passes the data to the neighbouring cells for further processing. Under the same

operating conditions, the serial-in serial-out array yields output results at a rate of one per m cycles after an initial delay of 3m cycles.

A bit-serial systolic divider circuit and multiplier over  $GF(2^m)$  was presented by Hasan and Bhargava in 1992 [16]. The design is based on the Gauss-Jordan Elimination algorithm and completely eliminates global data communications and dependency of the time step duration on m. The division algorithm requires the formulation of the supporting elements and the corresponding coefficient matrix by using a one-dimensional systolic array. The resulting system of 2m-1 simultaneous linear equations in 2m-1 unknowns are solved using a two-dimensional systolic array. With minor modifications, the same structure is used to perform multiplication over  $GF(2^m)$  in a computational time of 3m-1 time steps. The proposed inverter/divider requires three processors and a control signal consisting of  $2.5m^2 + 11.5m - 6$  registers,  $4m^2 + 12m - 5$  AND gates,  $1.5m^2 + 7.5m - 2$  OR gates, and  $0.5m^2 + 1.5m - 1$  XOR gates. The structure has a computational time of 5m-1 time steps and is independent of the irreducible polynomial.

A division and bit-serial multiplication algorithm were presented by Hasan and Bhargava in 1992 [17]. Using the coordinates of supporting elements, division over  $GF(q^m)$  is performed by solving a system of m linear equations over GF(q) when the field elements are represented by polynomials. It is further shown that division can be performed with a lower order of computational complexity by solving a Wiener-Hopf equation of degree m. The discrete-time Wiener-Hopf equation is defined as a system of m linear inhomogeneous equations, with m unknowns [17].

Structures for parallel multipliers derived from irreducible all-one and equally spaced polynomials were developed by Hasan et al in 1992 [18]. It is shown that the three basis modules of an all-one polynomial based parallel multiplier of a small field can be used to construct all the corresponding equally spaced polynomials of larger fields. A normal basis parallel-type multiplier for finite fields  $GF(2^m)$ generated by the irreducible all-one polynomials was recently presented by Hasan et al in 1993 [19]. It is a modified version of the Massey-Omura multiplier.

A systolic power-sum circuit designed to implement the function  $AB^2+C$  where A,B and C are elements of the field was presented by Wei in 1994 [20]. By adding one multiplexer and one demultiplexer, the power-sum circuit is configured to compute eight different types of computations viz  $AB,AB+C,A^2,A^2+C,AB^3,AB^2+C,A^3$  and  $A^3+C$ . All these computations are needed in decoding multiple error correcting BCH and Reed-Solomon codes in cases where the coefficients of the error locator polynomial are solved algebraically.

A bit-serial multiplier which has the same hardware requirements as the traditional Berlekamp multiplier was recently presented by Fenn et al in 1995 [21]. In the design, the variable multiplier is represented over the dual basis and the constant multiplicand is represented over the polynomial basis. The reverse is true with a constant traditional Berlekamp multiplier. It is shown that constant multipliers based on the proposed approach can operate at a higher frequency than those based on the traditional Berlekamp multiplier.

#### 1.2.3 Dividers and Inverters

Finding the inverse of an element over  $GF(2^m)$  is computationally intensive in hardware and still remains an active area of research. Finite field inversion and division are critical in decoding Reed-Solomon and BCH codes. During the decoding process, the Berlekamp-Massey and Forney algorithms often employ these arithmetic operations. The derived algorithms for decoding double error-correcting Reed-Solomon codes require the same functions as well. Thus, the latency and throughput of the inverters and dividers may dictate the overall speed of the decoder.

The traditional method for computing the inverse of elements in  $GF(2^m)$  uses read-only memory (ROM), Fermat's theorem or Euclid's algorithm. The size of the ROM is  $m2^m$  bits. The coordinates of an element are used as the address of the location in the ROM where the corresponding inverse is stored. The value of m can range from 3 to infinity. These methods are inefficient for VLSI implementation if large values of m are required. In recent years, several algorithms and their corresponding VLSI architectures for computing the inverse elements have been presented in the literature. For an arbitrary element A in the finite field  $GF(2^m)$ , the inverse operation of an element A is denoted by  $A^{-1} = A^{2^m-2}$ . Rewriting the exponent  $2^m - 2$  as  $2^1 + 2^2 + 2^3 + ... + 2^{m-1}$ , allows the inverse operation to be expressed as [10]

$$A^{-1} = (A^2) \cdot (A^{2^2}) \cdot (A^{2^3}) \cdot \cdot \cdot (A^{2^{m-1}})$$

(1.4)

In 1985, Wang et al [10] invented a parallel-in serial-out circuit for solving Equation (1.4) based on the Massey-Omura multiplier. In their design, the normal basis representation of the elements in the form  $(\alpha^{2^2}, \alpha^{2^1}, \alpha^{2^2}, \dots, \alpha^{2^{n-1}})$  is used. The method is impractical for large values of m since the number of XOR gates in the product function correspondingly becomes large. Since squaring is a cyclic shift operation in the normal basis, the inverse function is found in m clock cycles. In 1989, Feng [22] developed a serial-in parallel-out architecture based on the normal basis representation of the finite elements. The algorithm requires a computational complexity of  $O(m \log_2 m)$ . A throughput rate and latency of m(q + p)clock cycles, where p is the number of ones in the binary expression of m - 1 and q is the lower bound on  $\log_5 m$ , are needed to compute the inverse elements.

In 1993, Wang and Li [23] presented a serial-in serial-out systolic array architecture for performing the inverse element in  $GF(2^m)$ . In the analysis, the standard basis representation of the field elements is used. The design for  $GF(2^m)$  mimics the systolic array based on the Gauss-Jordan elimination algorithm for solving a system of  $2^m-1$  linear equations over GF(2) [24]. The proposed inversion circuitry has a latency of  $7^m-3$  clock cycles and a maximum throughput rate of  $2^m-1$  clock cycles. Without any modifications in hardware, the multiply-and-divide operation can easily be performed. The logic design of the architecture is independent of the primitive polynomials used to generate the field elements. All the operations of the serial-in serial-out systolic array are pipelined in such a manner that each cell completes a small fraction of the computations and passes the data to the neighbouring cells. The entire systolic array is made up of  $\frac{(m^2+m)}{2}$  main array cells and m boundary cells, where m is the size of the Galois field.

A fast normal basis inversion circuitry was presented by Fenn et al in 1996 [25]. The hardware scheme uses two registers, a multiplier, a squarer and a generator device in  $GF(2^m)$ . It exploits the properties of Fermat's theorem in order to progressively generate the solution in approximately  $\frac{m}{2}$  clock cycles. The inverter is shown to be more efficient for odd values of m and its features make it suitable for double error-correcting Reed-Solomon codes. The same design was recently reexamined and improved by Yen in 1997 [26]. It is demonstrated that the number of clock cycles per iteration can be further reduced to around  $\frac{m}{2}$ . Yen's algorithm clearly outperforms the algorithm by Fenn et al for large values of m. Another modification to the algorithm by Fenn et al was reported by Calvo and Torres in 1997 [27]. The generator and squarer devices have been totally eliminated from the original circuit.

In 1997, Hasan [28] presented an algorithm to perform sequential computation of division-and-accumulation (DDA) over  $GF(2^m)$ . The algorithm can also be used for the conventional rational numbers. It is shown that in the cases where nmultiplications and n inversions are required in the DDA, the new algorithm only requires 3n+1 multiplications and one inversion. Such a proposition is advantageous to fields where a division operation is at least three times more complex than a multiplication. The DDA structure is suitable for the systolic Reed-Solomon encoder [29] to efficiently compute the parity symbols during the encoding process.

## 1.2.4 Exponentiators

Exponentiation is extensively used in cryptosystems and error-correcting codes. The conventional approach for finding the exponent of an element in  $GF(2^m)$  uses read-only memory or table lookup. The value of m can range from 3 to infinity, which would require storing  $2^m$  elements of m-bit wide. This method is inefficient when m becomes too large. In recent years, several exponentiation algorithms and their corresponding VLSI architectures have been proposed.

For an arbitrary element  $\beta$  in the finite field  $GF(2^m)$  and an integer  $N(1 \le N \le 2^m - 1)$ , the exponentiation function is defined as  $\delta = \beta^N$ . Clearly,  $\delta$  is in  $GF(2^m)$ .

If N is represented in binary form as  $n_0, n_1, n_2, ..., n_{m-1}$  such that  $N = \sum_{i=0}^{m-1} n_i \cdot 2^i$ , then  $\delta = \beta^N$  can be expressed as follows [30][31]

$$\delta = \beta^{N} = \beta^{\sum_{i=1}^{m-1} n_i, 2^i}$$

$$= (\beta)^{n_0} \cdot (\beta^2)^{n_1} \cdot (\beta^{2^2})^{n_2} \cdot \cdots (\beta^{2^{m-1}})^{n_{m-1}}$$

$$= \prod_{i=1}^{m-1} E_i$$

(1.5)

where

$$E_i = \beta^{2^i}$$

if  $n_i = 1$  (1.6)

$$E_i = 1$$

if  $n_i = 0$  (1.7)

In 1988, Scott et al [32] proposed several sequential and parallel VLSI architectures for computing the product terms of the exponent in  $GF(2^m)$ . As described in the reference [32], the designs are targeted for applications that use Galois fields  $GF(2^m)$  for large values of m. Both the standard and normal based exponentiations are considered. The sequential exponentiation unit requires  $O(m^2)$  clock cycles assuming repeated use of a multiplier which possesses a throughput rate of one multiplication every m clock cycles. The fully parallel computation of the product terms yields one exponentiation per m clock cycles, assuming the use of (m-1) multipliers whose combined minimum latency is  $m+2m\log_2 m$  clock cycles. A multiplier latency of 2m clock cycles is assumed.

A VLSI design and implementation of an exponentiation circuit was also presented by Wang and Pei in 1990 [30]. The architecture can be used to generate pseudorandom number sequences in spread spectrum, cryptographic systems and digital signal processing applications such as noise generation. Elements in the finite field are represented in the normal basis. In this design, the exponentiation of an element is found in m clock cycles. The architectural details and VLSI layout of the chip for  $GF(2^4)$  are extensively illustrated.

In 1993, Arazi [33] presented two efficient exponentiation circuits which can be adopted for smartcard applications. They operate over the standard basis representation of elements in  $GF(2^m)$ . In one scheme, the algorithm is completed in 2mclock cycles instead of m. The shift registers can be implemented with dynamic instead of static registers, owing to the limited space in a smartcard-mounted chip. The second scheme is simpler and uses duplicates of the same cell to compute exponentiation in  $6m^2$  clock cycles.

A parallel-in-parallel-out bit-level systolic array architecture with unidirectional dataflow for computing exponentiation was first presented by Wang in 1994 [31]. Using the systolic multiplier proposed by Wang and Li in the reference [11], two-level pipelining is employed to achieve a maximum throughput of one output every clock cycle after an initial delay of  $2m^2+m$  cycles. Unidirectional dataflow is highly desirable in designing high-speed systems. The design can easily incorporate fault-tolerance.

An exponentiation algorithm based on a pattern matching and recognition technique was recently presented by Kovač and Rangathathan in 1996 [34]. Unlike the conventional methods which use repeated multiplications, the algorithm can perform the exponentiation operation on-the-fly. In the analysis, the nonzero elements of the Galois field  $GF(2^m)$  are represented in the standard basis. The elements are divided into subsets, where each subset corresponds to a pattern. More details on the related theorems and proofs are given in the reference [34]. In an effort to obtain high speed and maximum throughput, a systolic architecture which uses a

multistage linear pipeline and parallelism is proposed by the authors. Once the pipe is filled, a new result is obtained every clock cycle following a latency of  $2^m$  clock cycles. Thus, the architecture is recommended for applications that use  $GF(2^m)$ for values of m less than or equal to eight. The hardware allows the programming of different primitive irreducible polynomials of degree m less than or equal to eight. The design issues related to the CMOS VLSI implementation of the chip which performs the exponentiation operation over Galois field  $GF(2^4)$  are extensively enumerated. A maximum computational rate of 40 million exponentiations per second at a clock frequency of 40 MHz is possible.

#### 1.2.5 Summary

An overview of Galois field arithmetic operations has been presented. The multiplication, inverse, division, and exponentiation operations in  $GF(2^m)$  have been extensively described. The traditional method for evaluating these functions uses ROM, Fermat's theorem or Euclid's algorithm. However, these techniques are inefficient for VLSI implementation if large values of m are required. Thus, the latency and throughtput of the arithmetic units may dictate the overall speed of the global system. The development of more efficient algorithms and their corresponding VLSI architectures still remains an active area of research.

## 1.3 Scope of the Work

In this thesis I propose an m-programmable Galois field multiplier which uses the standard basis representation of the elements. A structure is also designed to implement both the exponent and inverse functions over  $GF(2^m)$ , where m is variable. The ability to operate with different symbol sizes of m-bits wide has been a limiting factor in past attempts to implement universal and reconfigurable encoders/decoders [2][5][6].

By using the proposed arithmetic circuits, coupled with a multiplexing technique to select different RS code parameters m and t, an ASIC synthesis of a testable RS encoder/decoder which implements a wide family of RS codes in  $GF(2^m)$  is developed. Unlike the chips which are customized for a specific m and t as reported in [35]-[31], it is reconfigurable and supports values of the Galois field symbol size m=3,4,5,6,7,8 and error correction capability t ranging from 1 to 16. This means the total cost of such a design is amortized over a wide application base. Since low design complexity and high throughput are desired in the experimental VLSI chip, the algebraic decoding technique is preferred over the time or transform domain methods.

Gate arrays, standard cells and full-custom are three potential VLSI technologies that could have been used to implement the RS encoder/decoder chip. However, a CMOS standard cell based design methodology, which uses hardware description language (HDL) logic synthesis, is found suitable because it allows easy mapping and optimization of the logic level design into integrated circuit (IC) layout using the state-of-the-art VLSI CAD tools. The design has been simulated at a frequency of 50 MHz and contains 218,206 logic gates.

## 1.4 Organization of the Thesis

The remaining chapters of the thesis are organized as follows:

In Chapter 2, the mathematical background and necessary theoretical details

are described for understanding Reed-Solomon codes.

Chapter 3 proposes an m-programmable Galois field multiplier which uses the standard basis representation of the elements. Using this multiplier, it is shown that the exponentiation and inverse operations can be both performed using the same reconfigurable hardware.

Chapter 4 discusses the design methodology, VLSI synthesis and operational features of a new programmable Reed-Solomon encoder/decoder processor.

Chapter 5 highlights the major conclusions of this research and recommendations for possible future work.

# Chapter 2

# Theoretical Background on Reed-Solomon Codes

In this chapter, the RS encoding and decoding algorithms are first explained. A survey on the existing RS encoder and decoder architectures usually designed for a fixed m is given.

### 2.1 General RS Code Definition

Discovered by I.S. Reed and G.S. Solomon in 1960, Reed-Solomon codes are an important subclass of nonbinary BCH codes. They are among the most versatile and powerful error control codes commonly used to correct both random and burst errors in digital communications and magnetic storage systems ranging from the digital audio disc to the Voyager spacecraft. A general block diagram of a digital communication system is shown in Figure 2.1.

The interest in RS codes was primarily theoretical until the concept of concatenated codes was formulated and first introduced by Forney in 1966 [1]. Concatenated coding has since been adopted by the U.S. National Aeronautics and Space Administration (NASA) for interplanetary space missions. It uses the con-

Figure 2.1: A Digital Communication System

volutional/RS channel encoding and decoding system.

For any positive integer  $m \ge 3$  and error correcting capability  $t \ge 1$ , there exists a t-error correcting RS code from the Galois field  $GF(2^m)$  with the following parameters [52]-[57]

Block Length  $n = 2^m - 1$  symbols

Number of Parity Check 2t = n - k symbols

Minimum Distance  $d_{min} = 2t + 1$

where k is the data message in symbols.

An (n,k,t) RS code has a generator polynomial G(x) of degree n-k often written as  $G(x) = (x + \alpha)(x + \alpha^2)...(x + \alpha^{2t})$ .

### 2.2 Encoding

The generator polynomial G(x) of an RS code has the form

$$\begin{array}{ll} G(x) = & \sum_{i=0}^{2t+b-1} (x-\alpha^i) \\ = & \sum_{i=0}^{2t} g_i x^i \\ = & g_0 + g_1 x + \ldots + g_{2t} x^{2t} \end{array} \tag{2.1}$$

where b is a nonnegative integer often chosen to be 1. The number of distinct coefficients of G(x) can be reduced by almost half by carefully choosing  $b = 2^{m-1} - t$ satisfying the relationship [8]

$$2b + 2t = 2^m (2.2)$$

There are two ways to encode the message M(x). In nonsystematic encoding, the codeword C(x) is generated simply as

$$C(x) = M(x)G(x) (2.3)$$

Thus the message M(x) is not explicitly present in the codeword C(x).

In systematic encoding, given a message polynomial M(x) and generator polynomial G(x), the codeword C(x) is generated as follows:

- (1) multiply the message M(x) by  $x^{2t}$  to obtain  $M(x)x^{2t}$

- (2) divide  $M(x)x^{2t}$  by G(x) to obtain the remainder polynomial  $\tilde{R}(x)$  and form the codeword C(x)

$$C(x) = x^{2t}M(x) + \hat{R}(x) = Q(x)G(x)$$

(2.4)

where Q(x) is the quotient and  $\tilde{R}(x) = \hat{r}_0 + \hat{r}_1 x + \hat{r}_2 x^2 + ... + \hat{r}_{2t-1} x^{2t-1}$  is the remainder or parity polynomial.

Circuits for performing division by G(x) or any arbitrary polynomial are available. The number of distinct multipliers  $g_0, g_1, ..., g_{2t}$  can be reduced almost by half by choosing  $b = 2^{m-1} - t$ .

Maki and Owsley [58] presented the VLSI design and implementation of the parallel Berlekamp architecture which has the speed performance equivalent to the conventional, but at a hardware cost 8 times the serial Berlekamp architecture. The serial and parallel VLSI architectures by Berlekamp perform encoding in the dual or trace orthogonal basis representation of the field elements.

A transmitted codeword C(x) may be corrupted in a noisy channel. The received polynomial R(x) can be expressed as the sum of the transmitted codeword C(x)and error polynomial E(x) as

$$R(x) = C(x) + E(x) = r_{n-1}x^{n-1} + ... + r_1x + r_0$$

(2.5)

The following sections describe available techniques which can be used to find and correct the errors in the received polynomial R(x).

## 2.3 Algebraic Decoding

The first task of an algebraic decoder is to determine the syndrome polynomial S(x) based on R(x). The coefficients of the syndrome polynomial are given by [54]

$$S_j = R(\alpha^j) = E(\alpha^j) = \sum_{i=0}^{n-1} r_i \alpha^{ij}$$

(2.6)

$1 \le j \le 2t$  for nonsymmetric coefficients of G(x)

or

$$2^{m-1} - t \le j \le 2^{m-1} + t - 1$$

for symmetric coefficients of  $G(x)$

After the evaluation of the syndromes, the error values  $e_0, e_1, ..., e_{n-1}$  can be found. If v errors actually occur in R(x), at the unknown locations  $i_1, i_2, ..., i_v$ , the error polynomial can be expressed as

$$E(x) = Y_1 x^{i_1} + Y_2 x^{i_2} + ... + Y_v x^{i_v}$$

(2.7)

where  $Y_l$  is the magnitude of the lth error at location  $i_l$ .

Prior to decoding, the values of v,  $i_1, ..., i_v$  and  $Y_1, ..., Y_v$  are initially unknown.

If  $X_l$  is the field element associated with the error location  $i_l$ , then the syndrome coefficients are given by

$$S_j = \sum_{i=1}^{v} Y_i X_i^i$$

(2.8)

for

$$j = 1, 2, ..., 2t$$

or  $j = 2^{m-1} - t, ..., 2^{m-1} + t - 1$

where  $Y_l$  is the error value and  $X_l$  is the error location of the lth error symbol.

An expansion of Equation (2.8) gives the following set of 2t simultaneous equations in v unknown error locations  $X_1, ..., X_v$  and v unknown error magnitudes  $Y_1, ..., Y_v$

$$\begin{split} S_1(x) &= Y_1X_1 + Y_2X_2 + \ldots + Y_vX_v \\ S_2(x) &= Y_1X_1^2 + Y_2X_2^2 + \ldots + Y_vX_v^2 \\ S_3(x) &= Y_1X_1^3 + Y_2X_2^3 + \ldots + Y_vX_v^3 \\ &\cdot \\ \cdot \\ \cdot \end{split}$$

$$S_{2t}(x) = Y_1 X_1^{2t} + Y_2 X_2^{2t} + \dots + Y_v X_v^{2t}$$

The above set of equations must have at least one solution because of the way the syndromes are defined. This solution is unique. Thus, the decoder's task is to find the unknowns, given the syndromes. This is equivalent to a problem in solving a system of nonlinear equations.

Clearly, the direct solution of the system of nonlinear equations is too difficult for large values of v. Instead, intermediate variables can be computed using the syndrome coefficients  $S_j$  from which the error locations  $X_1, ..., X_v$  can be determined. The error-locator polynomial is introduced as

$$\sum_{v} (x) = \Lambda(x) = \Lambda_{v}x^{v} + \Lambda_{v-1}x^{v-1} + ... + \Lambda_{1}x + 1 \qquad (2.9)$$

The polynomial is defined with roots at the error locations  $X_l^{-1}$  for l=1,2,...,v. The error location numbers  $X_l$  indicate errors at locations  $i_l$  for l=1,2,...,v. That is to say.

$$\Lambda(x) = \sum_{l=1}^{v} (1 - xX_l) = (1 - xX_1)(1 - xX_2)...(1 - xX_v) \qquad (2.10)$$

where  $X_t = \alpha^{i_t}$ .

To determine the coefficients of  $\Lambda(x)$  from the syndromes, equate Equations (2.9) and (2.10) and multiply both sides by  $Y_lX^{j+v}$  and set  $x = X_l^{-1}$ , i.e.,

$$Y_l X^{j+v}(\Lambda(x) = \sum_{l=1}^{v} (1 - xX_l) = \Lambda_v x^v + \Lambda_{v-1} x^{v-1} + ... + \Lambda_1 x + 1)$$

(2.11)

Then the left side becomes zero, giving

$$0 = Y_l X_l^{j+v} (1 + \Lambda_1 X_l^{-1} + \Lambda_2 X_l^{-2} + \ldots + \Lambda_{v-1} X_l^{-(v-1)} + \Lambda_v X_l^{-v})$$

$$Y_i(X_i^{j+v} + \Lambda_1 X_i^{j+v-1} + ... + \Lambda_v X_i^j) = 0$$

Such an equation holds for each l and each j. Summing up these equations from l = 1 to l = v, for each j, gives,

$$\textstyle \sum_{i=1}^v Y_i(X_i^{j+v} + \Lambda_1 X_i^{j+v-1} + \ldots + \Lambda_v X_i^j) = 0$$

OI

$$\sum_{l=1}^{v} Y_{l} X_{l}^{j+v} + \Lambda_{1} \sum_{l=1}^{v} Y_{l} X_{l}^{j+v-1} + ... + \Lambda_{v} \sum_{l=1}^{v} Y_{l} X_{l}^{j} = 0$$

The individual sums seem to be the syndromes and thus the equation becomes

$$\Lambda_1 S_{i+v-1} + \Lambda_2 S_{i+v-2} + ... + \Lambda_v S_i = -S_{i+v}$$

where

$$j = 1, 2, ..., v$$

This set of linear equations relates the syndromes to the coefficients of the error-location polynomial  $\Lambda(x)$ . It can also be expressed in matrix form as

The above system of equations has a unique solution for  $\Lambda$  which can be obtained by inverting the matrix A, if A is nonsingular. The matrix A is nonsingular if  $v \le t$ [54].

Peterson's direct-solution algorithm solves for the error locator polynomial  $\Lambda(x)$ in Equation (2.12) as follows [54]: as a trial value, v is set to the error correction capability of the code t and the determinant of the matrix computed. If the determinant is nonzero, it can be shown that this is the correct value of v. Otherwise, if it is zero, then the trial value of v is reduced by 1 and the process is repeated until a nonzero determinant is obtained. After the determinant has been obtained, the coefficients of  $\Lambda(x)$  are determined using the value of v in Equation (2.12) by standard techniques of linear algebra.

Peterson's direct-solution algorithm is inefficient for codes with a large error correcting capability t. The number of computations necessary to invert a v by vmatrix is directly proportional to  $v^3$ . In most applications, designers often prefer to use codes that correct a large number of errors. The following subsections detail two efficient decoding methods: the Berlekamp-Massey algorithm and Euclid's algorithm.

### 2.3.1 Berlekamp-Massey Algorithm

The Berlekamp-Massey algorithm relies on the fact that the matrix equation of Equation (2.12) is not arbitrary in its form, rather, the matrix is highly structured. This structure is used to obtain the vector Λ by a method that is conceptually more complicated but computationally much simpler [54][59][60].

If the vector  $\Lambda$  is known, then the first row of the above matrix equation defines  $S_{v+1}$  in terms of  $S_1, ..., S_v$ . The second row defines  $S_{v+2}$  in terms of  $S_2, ..., S_{v+1}$  and so forth. This sequential process can be summarized by the recursive relation

$$S_j = -\sum_{i=1}^{v} \Lambda_i S_{j-i}, \quad j = v + 1, ..., 2v$$

(2.13)

For fixed  $\Lambda$ , this is equivalent to the equation of an autoregressive filter. It can be implemented as a linear-feedback shift register with taps given by the coefficients of  $\Lambda$ .

Using this argument, the problem has been reduced to the design of a linear-feedback shift register that will consequently generate the known sequences of syndromes. Many such shift registers exist, but it is desirable to find the smaller linear-feedback shift register with this property. This will give the least-weight error pattern with a polynomial  $\Lambda(x)$  of smallest degree v. The polynomial of smallest degree v is unique, since the  $v \times v$  matrix of the original problem is invertible.

Any procedure for designing the autoregressive filter is also a method for solving the matrix equation for the  $\Lambda$  vector. The procedure applies in any field and does not assume any special properties for the sequence  $S_1, S_2, ..., S_2$ . To design the required shift register, the shift register length L and feedback connection polynomial  $\Lambda(x)$  must be determined.  $\Lambda(x)$  has the form

$$\Lambda(x) = \Lambda_v x^v + \Lambda_{v-1} x^{v-1} + ... + \Lambda_1 x + 1$$

(2.14)

where  $\deg \Lambda(x) \leq L$ .

The Berlekamp-Massey Algorithm uses the initial conditions  $\Lambda^{(0)}(x) = 1$ ,  $B^{(0)} = 1$ , and  $L_0 = 0$ , to compute  $\Lambda^{(2t)}(x)$  as follows:

$$\Delta_r = \sum_{j=0}^{n-1} \Lambda_j^{(r-1)} S_{r-j} \qquad (2.15)$$

$$L_r = \delta_r(r - L_{r-1}) + (1 - \delta_r)L_{r-1} \qquad (2.16)$$

$$\begin{bmatrix} \Lambda^{(r)}(x) \\ B^{(r)}(x) \end{bmatrix} = \begin{bmatrix} 1 & -\Delta_r x \\ \Delta_r^{-1} \delta_r & (1 - \delta_r) x \end{bmatrix} \begin{bmatrix} \Lambda^{(r-1)}(x) \\ B^{(r-1)}(x) \end{bmatrix}$$

(2.17)

for r = 1, ..., 2t

$$\delta_r = 1$$

, if both  $\Delta_r \neq 0$  and  $2L_{r-1} \leq r - 1$ ; and  $\delta_r = 0$ , otherwise. (2.18)

At the end of the 2t iterations, the smallest-degree polynomial  $\Lambda^{(2t)}(x)$  with  $\Lambda_0^{(2t)} = 1$  satisfying the relation

$$S_r + \sum_{i=1}^{n-1} \Lambda_j^{(2t)} S_{r-j} = 0$$

where  $r = L_{2t} + 1, ..., 2t$  will be obtained.

Then if we define the error evaluation polynomial  $\Omega(x)$  by the relation

$$S(x)\Lambda(x) = \Omega(x) \mod x^{2t}$$

(2.19)

then we can use  $\Omega(x)$  to solve for the error magnitudes  $Y_1, ..., Y_v$ .

### 2.3.2 Euclid's Algorithm

Euclid's algorithm is a recursive procedure for calculating the greatest common divisor (GCD) of two polynomials [61]. In a slightly expanded version, the algorithm will always produce the polynomials a(x) and b(x) satisfying

$$GCD[s(x), t(x)] = a(x)s(x) + b(x)t(x)$$

(2.20)

Euclid's algorithm uses the initial conditions  $R^{(0)}(x)=x^{2t},\,T^{(0)}(x)=\textstyle\sum_{j=1}^{2t}S_jx^{j-1},\,\text{and}$

$$A^{(0)} = \left[ \begin{array}{cc} 1 & 0 \\ 0 & 1 \end{array} \right]$$

to compute  $\Lambda^{(2t)}(x)$  as follows:

$$Q^{(r)}(x) = \left| \begin{array}{c} R^{(r)}(x) \\ \overline{T}^{(r)}(x) \end{array} \right|$$

(2.21)

$$A^{(r+1)}(x) = \begin{bmatrix} 1 & 0 \\ 0 & Q^{(r)}(x) \end{bmatrix} A^{(r)}(x)$$

(2.22)

$$\begin{bmatrix} R^{r+1}(x) \\ T^{(r+1)}(x) \end{bmatrix} = \begin{bmatrix} 0 & 1 \\ 1 & Q^{(r)}(x) \end{bmatrix} \begin{bmatrix} R^r(x) \\ T^{(r)}(x) \end{bmatrix}$$

(2.23)

The algorithm stops when the degree of  $T^{(r)}$  is less than t.

At the end of the iteration, the error evaluator and error locator polynomials are found using

$$Ω(x) = Δ^{-1}T^{(r)}(x)$$

(2.24)

$$\Lambda(x) = \Delta^{-1}A_{22}^{(r)}(x)$$

(2.25)

respectively, where  $\Delta = A_{22}^{(r)}(0)$  and  $A_{22}$  is the element of the matrix  $A^{(r)}$  in the second row and second column.

This algorithm has been modified by Shao et al to avoid the computation of the inverse elements of the Galois field [36][62]. The modified Euclid's algorithm recursively finds the i-th remainder  $R_i(x)$  and the quantities  $\gamma_i(x)$  and  $\lambda_i(x)$  that satisfy the relation

$$\gamma_i(x)A(x) + \lambda_i(x)S(x) = R_i(x)$$

and stops when the degree of the remainder polynomial  $R_t(x)$  is less than t, where  $A(x) = x^{2t}$  and  $S(x) = \sum_{k=1}^{2t} S_k x^{2t-k}$ .

Using the initial conditions  $R_0(x) = A(x)$ ,  $Q_0(x) = S(x)$ ,  $\lambda_0(x) = 0$ ,  $\mu_0(x) = 1$ ,  $\gamma_0(x) = 1$ ,  $\gamma_0(x) = 0$ , it computes  $R_i(x)$ ,  $\lambda_i(x)$  and  $\gamma_i(x)$  as follows:

$$R_{i}(x) = [\sigma_{i-1}b_{i-1}R_{i-1}(x) + \hat{\sigma}_{i-1}a_{i-1}Q_{i-1}(x)] \\ -x^{|l_{i-1}|}[\sigma_{i-1}a_{i-1}Q_{i-1}(x) + \hat{\sigma}_{i-1}b_{i-1}R_{i-1}(x)]$$

(2.26)

$$\lambda_{i}(x) = [\sigma_{i-1}b_{i-1}\lambda_{i-1}(x) + \hat{\sigma}_{i-1}a_{i-1}\mu_{i-1}(x)] \\ -x^{[l_{i-1}[}[\sigma_{i-1}a_{i-1}\mu_{i-1}(x) + \hat{\sigma}_{i-1}b_{i-1}\lambda_{i-1}(x)]$$

(2.27)

$$\gamma_{i}(x) = \begin{bmatrix} \sigma_{i-1}b_{i-1}\gamma_{i-1}(x) + \hat{\sigma}_{i-1}a_{i-1}\eta_{i-1}(x) \end{bmatrix} \\ -x^{|l_{i-1}|}[\sigma_{i-1}a_{i-1}\mu_{i-1}(x) + \hat{\sigma}_{i-1}b_{i-1}\gamma_{i-1}(x)] \tag{2.28}$$

$$Q_i(x) = \sigma_{i-1}Q_{i-1}(x) + \hat{\sigma}_{i-1}R_{i-1}(x)$$

(2.29)

$$\mu_i(x) = \sigma_{i-1}\mu_{i-1}(x) + \hat{\sigma}_{i-1}\lambda_{i-1}(x)$$

(2.30)

$$\eta_i(x) = \sigma_{i-1}\eta_{i-1}(x) + \hat{\sigma}_{i-1}\gamma_{i-1}(x)$$

(2.31)

where  $a_{i-1}$  and  $b_{i-1}$  are the leading coefficients of  $R_{i-1}(x)$  and  $Q_{i-1}$  respectively,  $l_{i-1} = \deg[R_{i-1}(x)] - [\deg(Q_{i-1}(x)], \ \sigma_{i-1} = 1 \text{ if } l_{i-1} \ge 0 \text{ and } \sigma_{i-1} = 0 \text{ if } l_{i-1} < 0.$

The iterations stop when  $\deg[R_i(x)] < t$ , after which the error locator polynomial  $\Lambda(x) = \lambda_i(x)$  and error evaluator polynomial  $\Omega(x) = R_i(x)$ .

Once the error locator  $\Lambda(x)$  and error evaluator  $\Omega(x)$  polynomials have been determined using the above techniques, the error locations and error values or magnitudes can be found using the Chien search and the Forney algorithm. These methods are described in the following subsections.

### 2.3.3 Chien Search

Once the coefficients of the error locator polynomial  $\Lambda_1, ..., \Lambda_{\theta}$  have been found, the roots of  $\Lambda(x)$  can be computed using the Chien search. The Chien search is a systematic means of evaluating the error locator polynomial at all elements in a field  $GF(2^m)$  [63]. The evaluation of each element is performed in

$$\Lambda(x) = \Lambda_v x^v + \Lambda_{v-1} x^{v-1} + ... + \Lambda_1 x + 1$$

(2.32)

to check for  $\Lambda(x) = 0$ .

### 2.3.4 The Forney Algorithm

The Forney algorithm is an efficient method often used to compute the error magnitudes. The error evaluator polynomial  $\Omega(x)$  is defined as [59]

$$\Omega(x) = S(x)\Lambda(x) \bmod x^{2t} \tag{2.33}$$

where

$$\Lambda(x) = \Lambda_v x^v + \Lambda_{v-1} x^{v-1} + ... + \Lambda_1 x + 1 = \prod_{l=1}^{v} (1 - xX_l)$$

and

$$S(x) = \sum_{j=1}^{2t} S_j x^j = \sum_{j=1}^{2t} \sum_{i=1}^{v} Y_i X_i^j x^j$$

Equation (2.33) can now be expanded as

$$\Omega(x) = x \sum_{i=1}^{v} Y_i X_i \prod_{l \neq i} (1 - X_l x)$$

(2.34)

Instead of using matrix inversion to find the error magnitudes, the Forney algorithm calculates them as

$$Y_{l} = \frac{\Omega(X_{l}^{-1})}{\prod_{j \neq l} (1 - X_{j}X_{l}^{-1})} = -\frac{\Omega(X_{l}^{-1})}{X_{l}^{-1}\Lambda'(X_{l}^{-1})} = -\frac{X_{l}\Omega(X_{l}^{-1})}{\Lambda'(X_{l}^{-1})} \tag{2.35}$$

where the derivative of  $\Lambda(x)$  is defined as

$$\Lambda'(x) = -\sum_{i=1}^{v} X_i \prod_{j \neq i} (1 - xX_j)$$

(2.36)

and hence

$$\Lambda'(X_t^{-1}) = -X_t \prod_{j \neq t} (1 - X_j X_t^{-1})$$

(2.37)

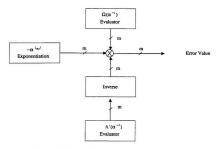

Figure 2.2: Algebraic Decoder

In summary, the algebraic decoding algorithm works as follows:

Step 1: Calculate the syndromes according to Equation (2.6).

Step 2: Perform the Berlekamp-Massey or Euclid's algorithm to obtain the error locator polynomial  $\Lambda(x)$ . Also find the error evaluator polynomial  $\Omega(x)$ .

Step 3: Perform the Chien Search to find the roots of  $\Lambda(x)$ .

Step 4: Find the error values Y(x) = E(x) according to Equation (2.35).

Step 5: Correct the received word C(x) = E(x) + R(x)

The structure of the algebraic decoder is shown in Figure 2.2.

### 2.4 Time-Domain Decoding

### 2.4.1 Error Locator and Evaluator Polynomials

The time-domain decoding algorithm was first proposed by Blahut [64]. It is explained in detail in the references [5][6][54] and is only summarized in this subsection.

The time-domain algorithm uses the initial conditions  $\lambda_i^{(0)} = b_i^{(0)} = \omega_i^{(0)} = 1$  and  $\lambda_i^{'(0)} = b_i^{'(0)} = a_i^{(0)} = 0$  for all i, to compute the following set of recursive equations:

$$\Delta_r = \sum_{i=1}^{n-1} \alpha^{ir} [\lambda_i^{(r-1)} r_i] \qquad (2.38)$$

$$L_r = \delta_r(r - L_{r-1}) + (1 - \delta_r)L_{r-1}$$

(2.39)

$$\begin{bmatrix} \lambda_{j}^{(r)} \\ b_{j}^{(r)} \\ \lambda_{j}^{(r)} \\ b_{j}^{(r)} \end{bmatrix} = \begin{bmatrix} 1 & -\Delta_{r}\alpha^{-i} & 0 & 0 \\ \Delta_{r}^{-1}\delta_{r} & (1-\delta_{r})\alpha^{-i} & 0 & 0 \\ 0 & -\Delta_{r} & 1 & -\Delta_{r}\alpha^{-i} \\ 0 & (1-\delta_{r}) & \Delta_{r}^{-1}\delta_{r} & (1-\delta_{r})\alpha^{-i} \end{bmatrix} \begin{bmatrix} \lambda_{j}^{(r-1)} \\ b_{j}^{(r-1)} \\ \lambda_{j}^{(r-1)} \\ b_{j}^{(r-1)} \end{bmatrix} (2.40)$$

$$\begin{bmatrix} \omega_i^{(r)} \\ a_i^{(r)} \end{bmatrix} = \begin{bmatrix} 1 & -\Delta_r \alpha^{-i} \\ \Delta_r^{-1} \delta_r & (1 - \delta_r) \alpha^{-i} \end{bmatrix} \begin{bmatrix} \omega_i^{(r-1)} \\ a_i^{(r-1)} \end{bmatrix}$$

(2.41)

for i = 0, ..., n - 1, r = 1, 2, ..., 2t.

L=0 and  $\delta=1$  if both  $\Delta_r\neq 0$  and  $2L\leq r-1$ , and  $\delta=0$  otherwise.

### 2.4.2 Error Evaluation

Using the error locator vector  $\lambda$ , the vector  $\lambda' = \lambda'^{(2t)}$ , the error evaluator vector

$$\omega = \omega^{(2t)}$$

, the error magnitudes are computed as  $e_i = -\frac{\alpha^i(w_i)}{V}$ , if  $\lambda_i = 0$

$$e_i = 0$$

if  $\lambda_i \neq 0$

The structure of the time-domain decoder is shown in Figure 2.3.

Figure 2.3: Time-Domain Decoder

### 2.5 Error Correction

Once E(x) is known, the corrected codeword C(x) can be obtained from C(x) = R(x) + E(x).

# 2.6 Algebraic vs. Time-Domain Decoding Algorithms

Based on the above discussion, the fundamental differences between the algebraic and time-domain decoding algorithms are listed below:

- The time-domain algorithm has one major computational step. Unlike the algebraic decoding algorithm, it does not compute the syndromes or perform the Chien search to find the error locations.

- (2) The time-domain algorithm deals with vectors which have n components while different length vectors and different degree polynomials are used in the various steps of the algebraic algorithms.

- (3) By changing the error correction capability of the code t, the operations in the

time-domain algorithms essentially remain the same, while those in the algebraic algorithm are dependent on t.

(4) Although complex to design, the algebraic decoding technique is recommended for high speed applications. The major drawback of the time-domain algorithm is its high computation count. This is brought about by the fact that it has to operate on the complete data sequence of length n, while the algebraic algorithm needs to work only on the syndrome sequence of length 2t = (n - k) m-bit symbols.

### 2.7 RS Encoder/Decoder Architectures

In 1984, Blahut [64] originally presented two architectures for universal RS decoders based on the time-domain algorithms. The decoders work directly on the received data to generate the error sequence. They are attractive for VLSI design since one major computational step is required. Unlike the algebraic decoders, neither the syndrome evaluation nor the Chien search is required. Such a decoder can be used to decode any RS or BCH codeword up to the limits of the storage registers associated with the chip. Within these limits, it can correct any number of random errors and erasures depending on the received data. Shayan et al restructured the time-domain algorithm to implement a versatile time-domain [5] and a cellular decoder [6] which can operate in a Galois field  $GF(2^m)$  with a fixed m.

Conceptual models for the logic structures of the RS encoder and decoder chips were presented in [65][66]. The encoder is constructed by cascading and interconnecting a group of VLSI chips. The decoder architecture is based on the repetitive and recursive properties of RS decoding procedures.

Truong et al [8][9] reported a single chip VLSI RS encoder implemented in

NMOS technology. The encoding algorithm is a bit-serial multiplication algorithm developed by Berlekamp for the encoding of RS codes using a dual basis over a Galois field. Compared to the conventional RS encoder for long codes, which often requires lookup tables to perform the multiplication of two field elements, Berlekamp's algorithm requires only shifting and exclusive-OR operations.

Shao et al [62] developed a pipeline structure of a transform decoder similar to a systolic array to decode RS codes. The error locator polynomial is computed by the modified Euclid's algorithm which avoids computing inverse elements. The modified Euclid's algorithm architecture is based on the pipeline architecture suggested by Brent and Kung [67] to compute the greatest common divisor of two polynomials.

A full-custom CMOS implementation of a RS encoder was proposed by Maki et al in 1986 [35]. In order to reduce the transistor count, domino logic was used. Its architecture is invariant in operational speed or silicon area to the field polynomial, generator polynomial or operation in the dual basis or normal field. With k encoder chips operating in parallel, a k - 1 fault tolerant system can be constructed.

A pipelined RS decoder based on the transform decoding algorithm presented earlier by the authors is described in [36][37]. The transform decoding technique is replaced by a time domain algorithm to permit efficient pipeline processing with reduced circuitry. By using multiplexing, the proposed Euclid's algorithm maintains the throughput rate with little additional complexity.

In 1990, Tong [38] presented an 8-error correcting RS encoder-decoder. The encoder and decoder can independently process 40 Mbytes of data per second. The chip was designed using a standard ASIC methodology and fabricated in a 1-µm CMOS compact-array technology. In 1991, Seroussi [29] presented a systolic architecture for a RS encoder. The architecture completely eliminates the global feedback signal found in the conventional encoder architectures which use the linear feedback shift register (LFSR). The encoding algorithm is based on the Cauchy representation of the generator matrix of the code. The architecture is suitable for very high speed applications, where global signals and the need for global synchronization may pose restrictions on the achievable switching speed of the encoder.

A full-custom CMOS VLSI implementation of a Reed-Solomon decoder for the Hubble Space Telescope and television applications was presented by Whitaker t al in 1991 [3][39]. The architecture is similar to others presented in the references [40][41]. It is implemented in a 1.6  $\mu$ m double metal CMOS technology and operates at a data rate of 80 Mbits/s using a 10 MHz system/data clock. In these designs, Euclid's algorithm is used to determine both the error location and error magnitude polynomials.

In order to solve the problem of multiple notations and multiple algorithms often faced by designers, high level synthesis is used to study the different BCH and RS decoding algorithms [42]. Special VHDL packages are created to describe the various operations on Galois fields. A VHDL synthesis tool consequently allows efficient exploration of various architectures in order to select an optimum one.

Methods for reducing the computation count in the time domain algorithm for RS decoding were presented by Choomchuang and Arambepola in 1993 [43]. An architecture for an error correction circuit suitable for high-rate data decoding of RS codes was proposed in [44]. The operational steps for multiple-error decoding are reduced by a 4-stage pipeline and a superscalar processor of a Galois field. The experimental chip achieves 16 Mbytes/s of data decoding sufficient for compressed video signals of high-definition as well as those of standard-definition TV's.

The use of high level synthesis techniques to realize a high-speed Reed-Solomon CODEC was reported by Cools et al in 1994 [45]. High level synthesis allows rapid design exploration over a large range of architectures. An error free transfer is guaranteed between all the levels of the design process. The design was captured using a combination of Mentor Graphics and a Cathedral- $\frac{1}{3}$  compiler. The architectural design phase concentrates on the composition of the data path and global cycle count; logic synthesis performs local optimizations in terms of hardware and timing: whereas the place-and-route tools compose the final layout.

A low circuit complexity architecture for a Reed-Solomon encoder suitable for satellites and pocket size wireless terminals was presented by Hasan and Bhargava in 1995 [46]. The encoder uses the triangular basis multiplication algorithm. Using pipeline and bit-serial operations the encoder is able to obtain code rates ranging from unity to a minimum value determined by the associated hardware circuitry.

In 1995, Chen et al [47] presented a three stage pipelined VLSI architecture of a Reed-Solomon decoder. The decoder has an erasure function and uses the modified Euclid's algorithm to solve the key equation. The block length is variable. The hardware complexity is shown to be only dependent on the number of parity check bytes. The modified Euclid's algorithm allows the error evaluator and error location vectors to be determined sequentially by using a smaller amount of hardware. The algorithm state machine and architecture were verified using Verilog hardware description language.

In 1995, Iwamura et al [48] proposed a class of systolic arrays to perform binary

RS decoding procedures including erasure correction. Such an RS decoder is suitable for VLSI implementation since the arrays consist of simple processing elements of the same type.

In 1997, Hsu and Wang [49] presented a pipelined VLSI architecture of a Reed-Solomon decoder which combines a modified-time domain Berlekamp-Massey algorithm with the remainder decoding concept. For a t-error correcting RS code with block length n, only 2t consecutive symbols, instead of n are required to determine the discrepancy value during the decoding process.

A VLSI architecture for an area efficient Reed-Solomon product-code encoder and decoder was published by Kwon and Shin in 1997 [4]. The architecture uses functional block sharing to implement the encoder, modified syndrome and erasure locator polynomial evaluations. The modified Euclid's algorithm is used to determine the error/erasure locator and error/erasure evaluator polynomials. The architecture is recommended for encoding/decoding audio and video signals over GF(256).