### Development of an FPGA and MCU based Stack-able Processing platform incorporated with on-board compute module for Real-time processing applications

by

©Teng Wang

A thesis submitted to the School of Graduate Studies in partial fulfillment of the requirements for the degree of

Master of Engineering Department of Engineering and Applied Science

> Memorial University of Newfoundland November 2017

St. John's  $% \left( {{{\rm{St}}_{\rm{s}}}} \right)$

Newfoundland

### Abstract

The focus of this thesis is to develop an FPGA and MCU-based stackable processing platform incorporated with an on-board computer module for real-time processing applications. The goal is to deliver a compact-sized hardware platform with extensible capabilities to provide high-speed, parallel computing with low power consumption. This hardware platform is named ioNeurons and consists of three module types: processing modules, sensing modules, and interface modules. The ioNeurons ecosystem design is based on combining individual strengths into highly adaptable and powerful solutions. The processing modules are stackable in no particular order, allowing the ability to match multiple modules' individual capabilities to the project's needs. Developers can assign tasks to multiple processing modules according to the different real-time requirements. The implementation of a small-scale quadrotor helicopter is introduced as an application of this hardware platform.

### Acknowledgements

I would like to express my sincere gratitude to my supervisor Dr. Nicholas Krouglicof for providing me this great opportunity to work on and develop such interesting and rewarding projects. With his outstanding guidance and support I learned and believes no detail is insignificant when designing. His guidance benefited me in the past, now and the rest of my life.

I would like to thank my parents, Mrs. Ping Li and Mr. Yanzhou Wang for their invaluable support, love and encouragement.

I would like to thank my wife, Mrs. Xin Huang. Without her continued understanding, moral support and love, this thesis would not have been possible.

I would like to thank Dr. Nicholas Krouglicof and Dr. Ralf Bachmayer for providing me a full time job which related to my researches and interest in Memorial University as a Research and Project Engineer between 2013 to 2016. I learned how to work with colleagues for a common goal, to be a qualified contributor in a harmonious team. Challenges in experiments, problems in a practical application, all those obstacles makes me stronger and smarter. When problems are solved, when we move forward even a small step, all those small things power me to go further. Even in a hard time, I won't forget the encouraged smiles were on their faces.

Facing difficulties, I believe that you have one less reason to hang back, when there is one more friend who unswervingly trusts you. Thanks for every friend who trusts me. Special thanks to my peers Mohammed Raju Hossain, Stephen Reddin, Michael Morgan, Dennis Fifield.

Lastly, I dedicate this thesis to my children Ayden Wang, and Olivia Wang. I love you.

# **Table of Contents**

| $\mathbf{A}$ | bstra  | let                                  | ii   |

|--------------|--------|--------------------------------------|------|

| A            | cknov  | wledgments                           | iii  |

| Ta           | able ( | of Contents                          | vii  |

| Li           | st of  | Tables                               | viii |

| Li           | st of  | Figures                              | xi   |

| 1            | Intr   | roduction                            | 1    |

|              | 1.1    | Literature Review                    | 1    |

|              |        | 1.1.1 FPGA                           | 1    |

|              |        | 1.1.2 MCU                            | 3    |

|              |        | 1.1.3 Applications of FPGAs and MCUs | 5    |

|              | 1.2    | Motivation and Scope of Work         | 8    |

| <b>2</b>     | Sys    | tem Description                      | 10   |

|              | 2.1    | Introduction                         | 10   |

|              | 2.2    | Platform Architecture                | 17   |

|              | 2.3    | Stack-able Interfaces                | 19   |

| 3 | Des | ign an  | d Implementation of the FPGA Module  | 25 |

|---|-----|---------|--------------------------------------|----|

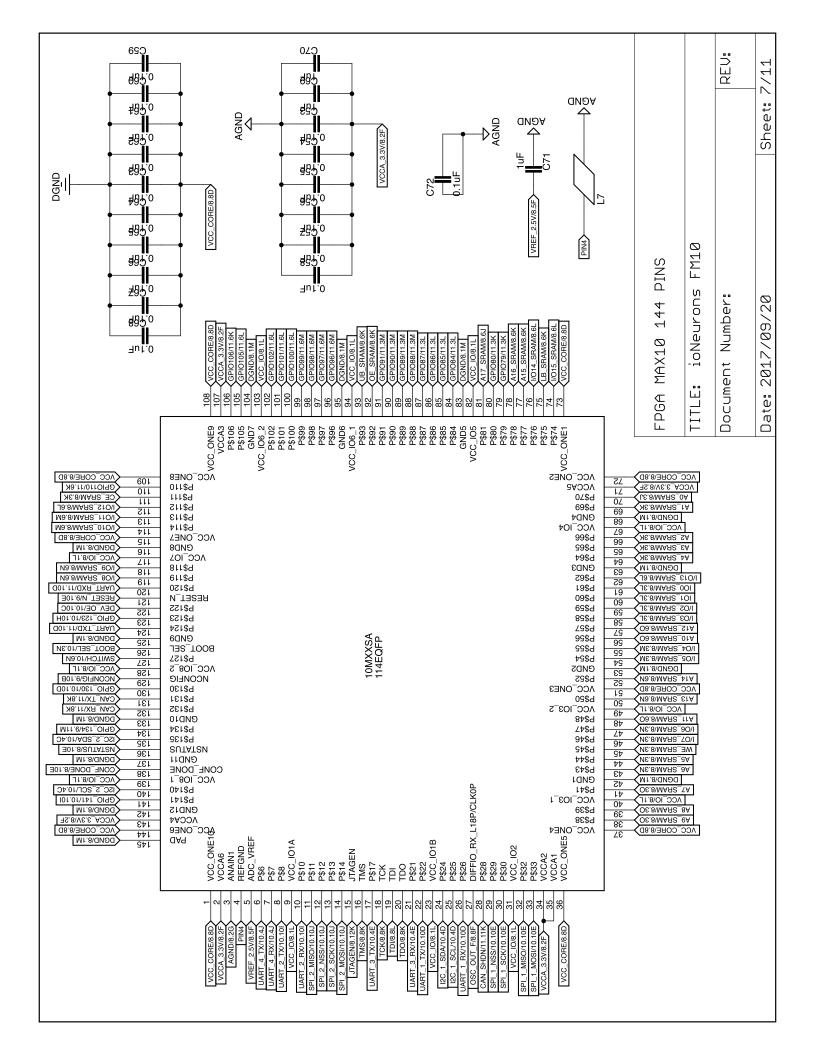

|   | 3.1 | FM10    | Board Overview                       | 25 |

|   | 3.2 | Layou   | t and Components                     | 27 |

|   |     | 3.2.1   | Power management and distribution    | 30 |

|   |     | 3.2.2   | FPGA: 10M25SAE114I7G                 | 33 |

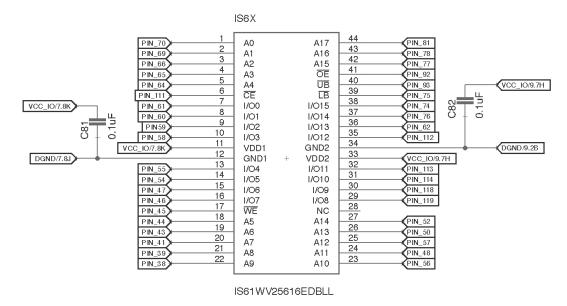

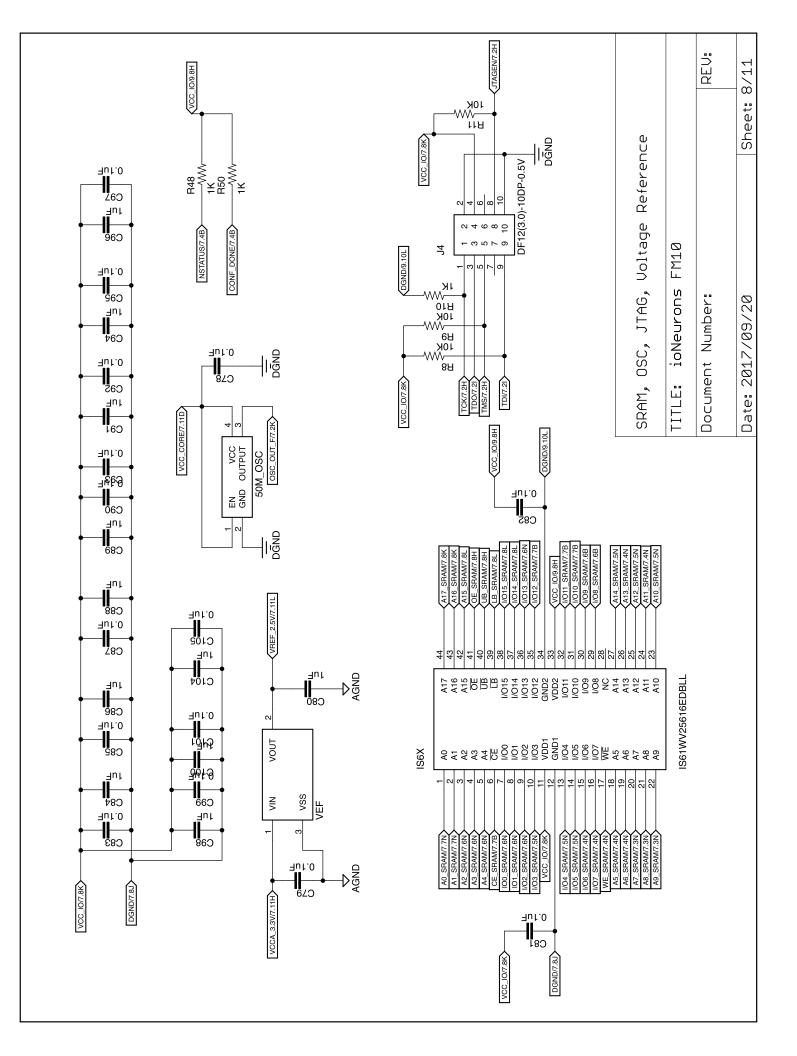

|   |     | 3.2.3   | SRAM: IS61WV25616EDBLL               | 34 |

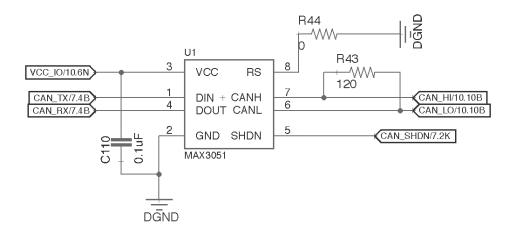

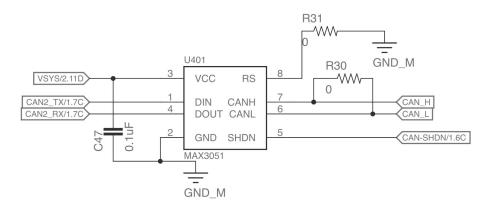

|   |     | 3.2.4   | CAN Transceiver                      | 35 |

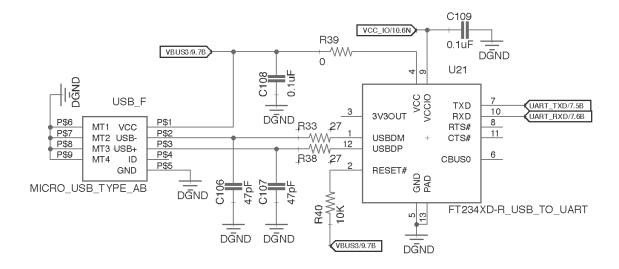

|   |     | 3.2.5   | FTDI                                 | 37 |

|   | 3.3 | Interfa | aces and pin mapping                 | 38 |

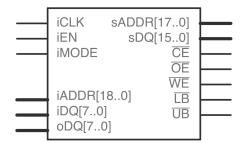

|   | 3.4 | FM10    | Firmware                             | 44 |

|   |     | 3.4.1   | SRAM Controller                      | 44 |

|   |     | 3.4.2   | UART                                 | 47 |

|   | 3.5 | Config  | guring FM10 with USB-Blaster         | 50 |

|   | 3.6 | Concl   | usions                               | 52 |

| 4 | Des | ign an  | d Implementation of the MCU Module   | 53 |

|   | 4.1 | EM4 ]   | Board Overview                       | 53 |

|   | 4.2 | Layou   | t and Components                     | 56 |

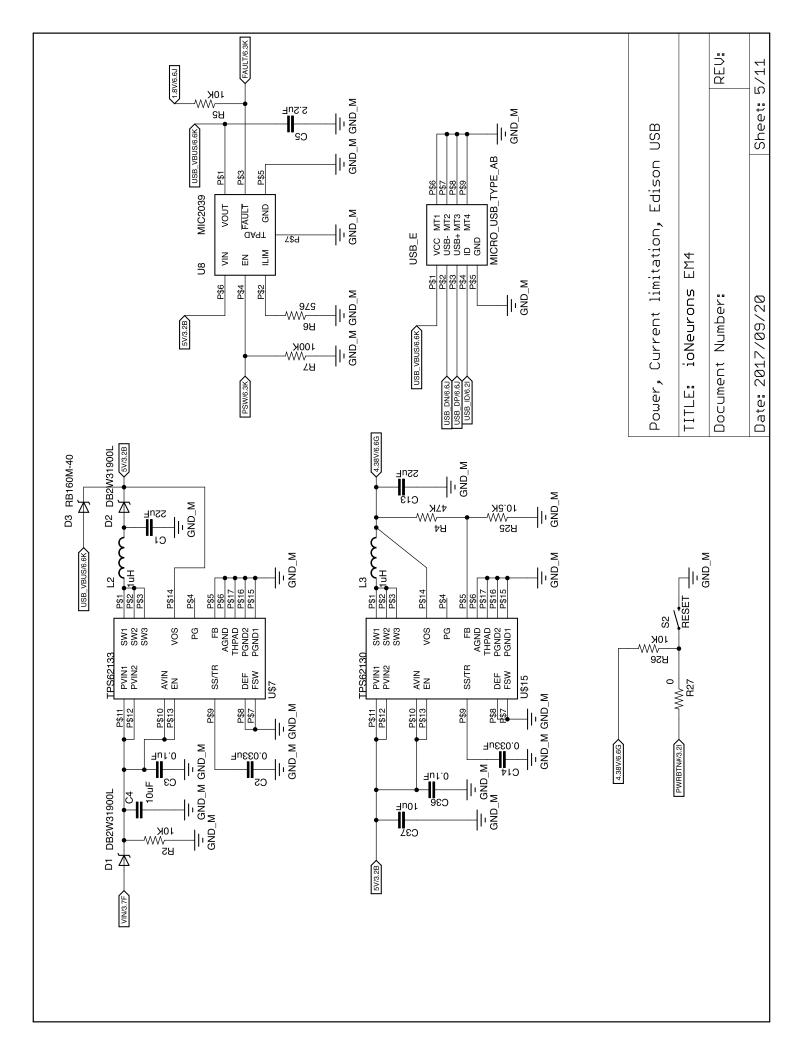

|   |     | 4.2.1   | Power management and distribution    | 60 |

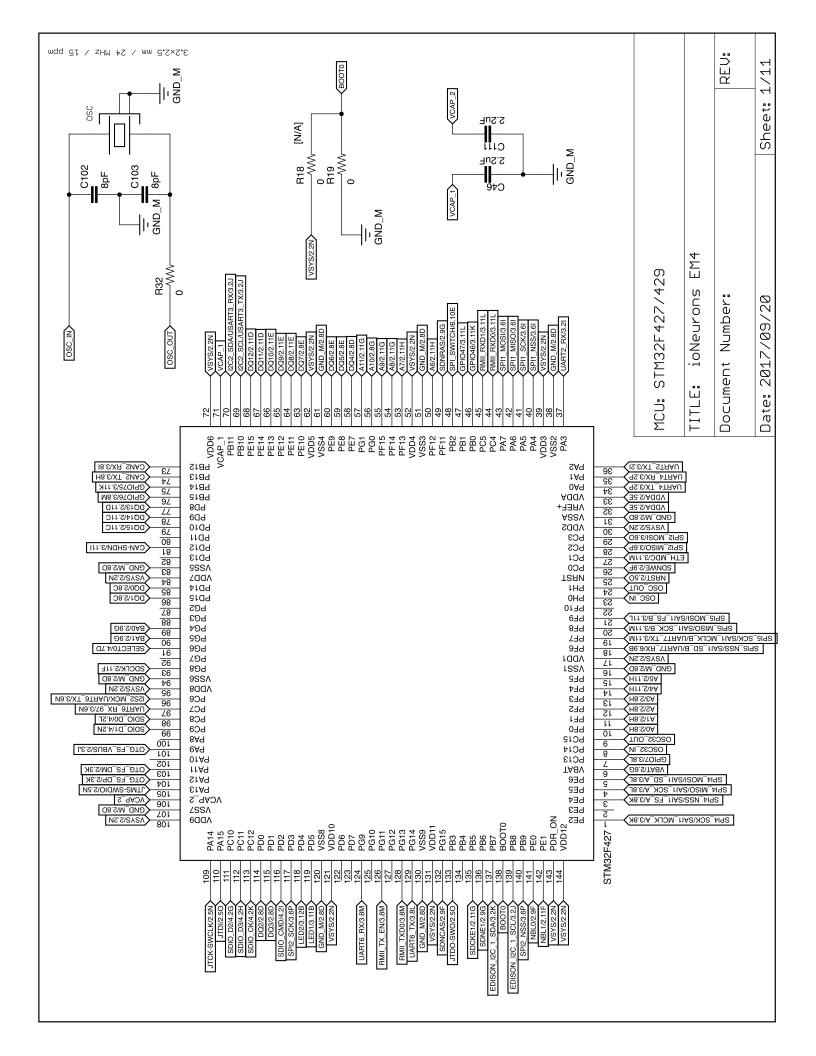

|   |     | 4.2.2   | MCU: STM32F427ZIT7                   | 63 |

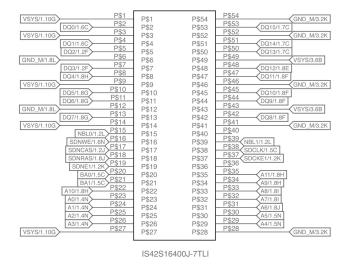

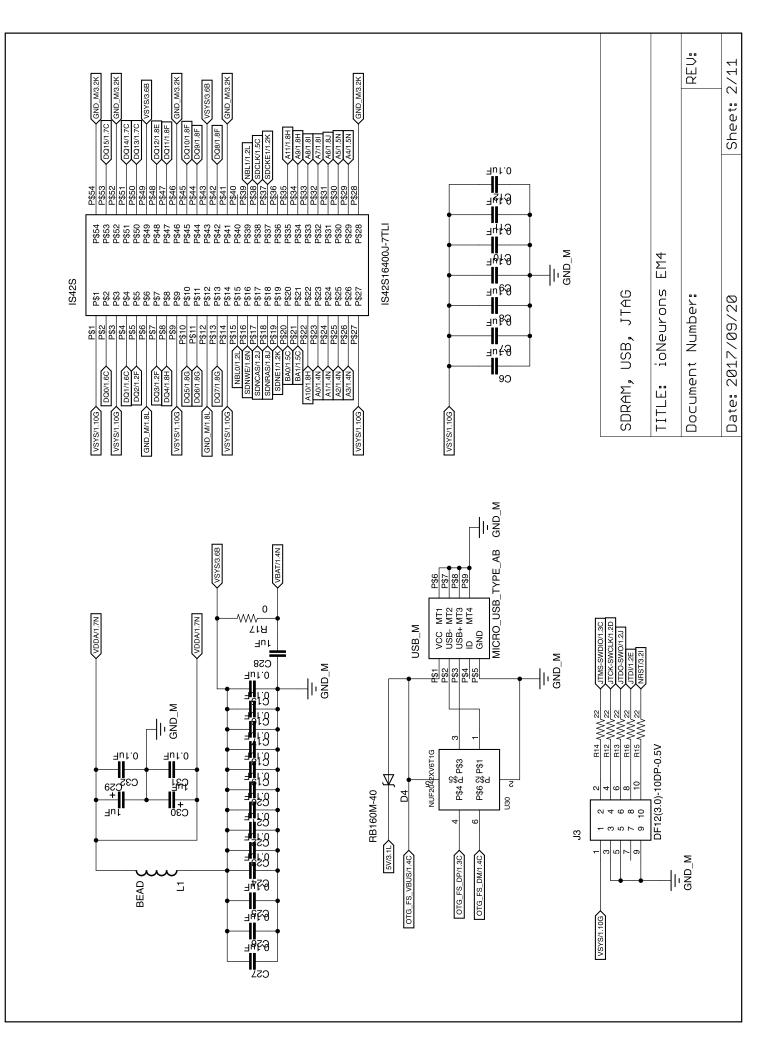

|   |     | 4.2.3   | SDRAM: IS42S16400J                   | 66 |

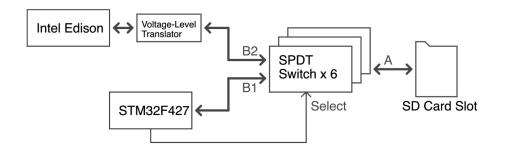

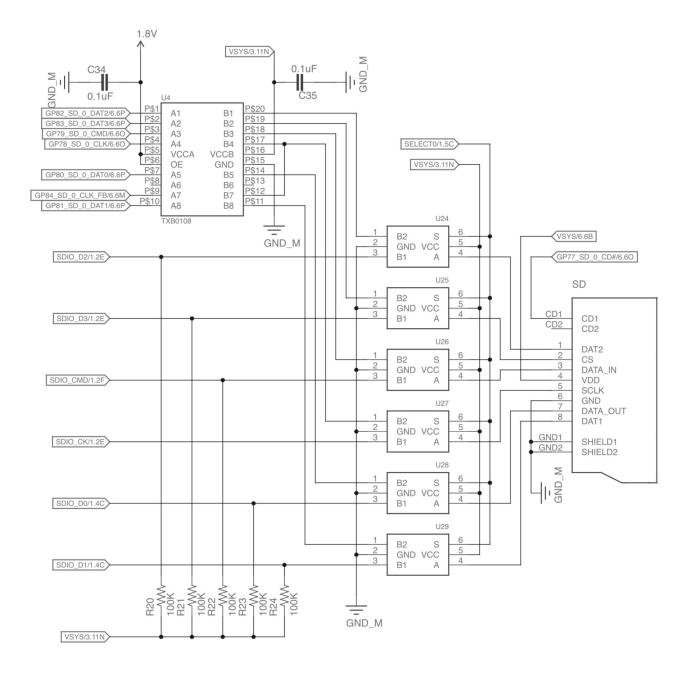

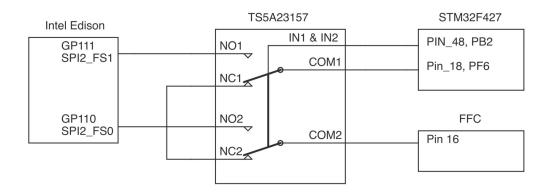

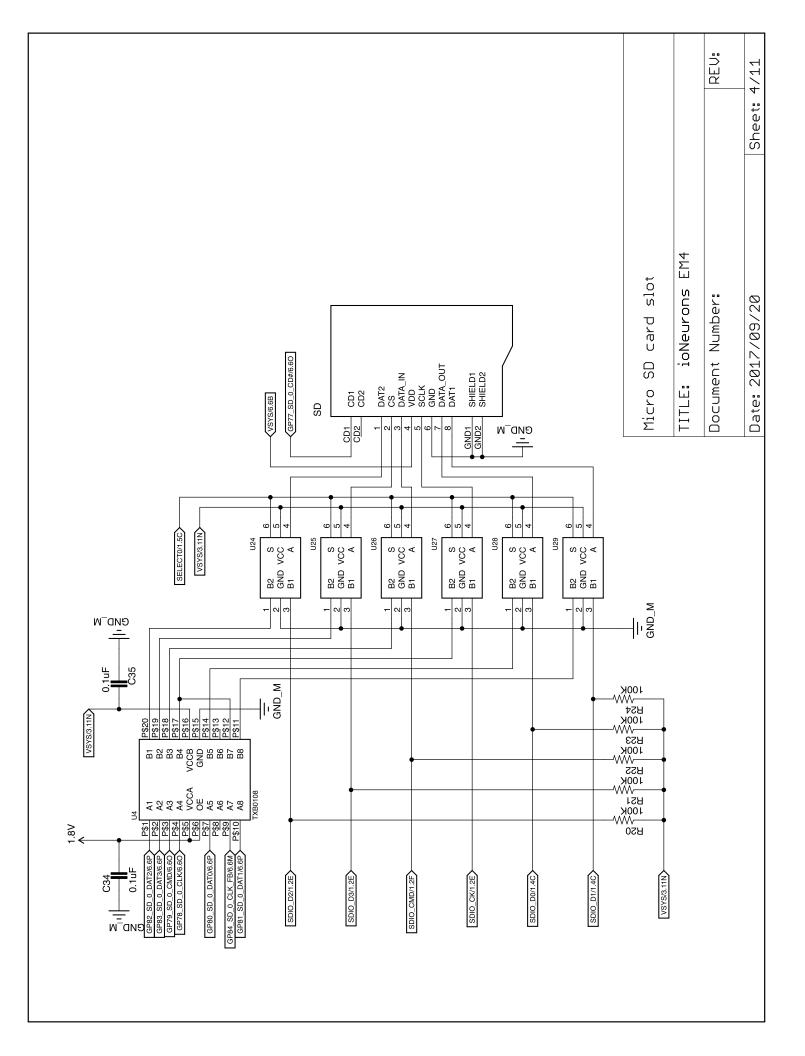

|   |     | 4.2.4   | On board external Micro SD card slot | 67 |

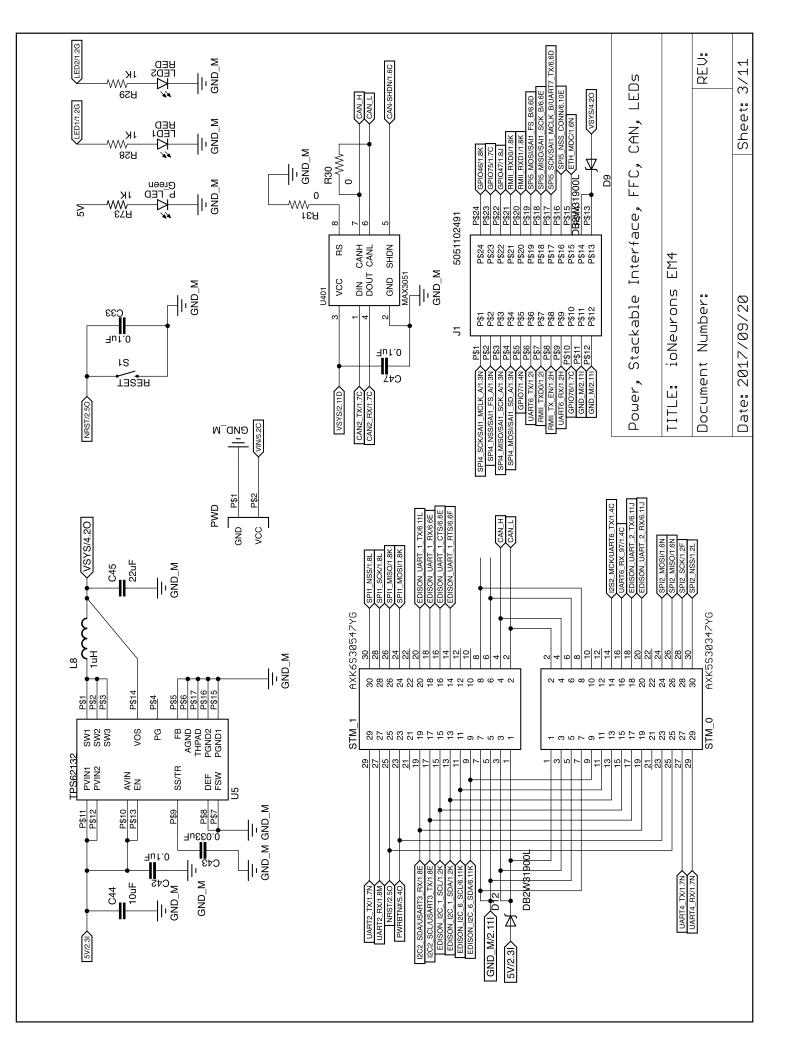

|   |     | 4.2.5   | CAN Transceiver                      | 70 |

|   | 4.3 | Interfa | aces and pin mapping                 | 72 |

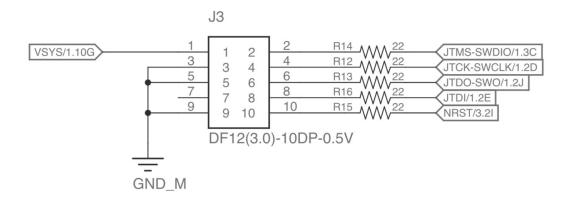

|   | 4.4 | Config  | guring EM4 with ST-LINK              | 81 |

|   | 4.5 | Concl   | usions                               | 82 |

| <b>5</b> | Des            | ign an  | d Impler   | mentation of the Camera Module                         | 84  |

|----------|----------------|---------|------------|--------------------------------------------------------|-----|

|          | 5.1            | C5M I   | Board Ov   | erview                                                 | 84  |

|          | 5.2            | Layou   | t and Cor  | nponents                                               | 86  |

|          |                | 5.2.1   | Power m    | nanagement and distribution                            | 89  |

|          |                | 5.2.2   | Applicat   | ion schematic                                          | 91  |

|          | 5.3            | C5M I   | Interfaces |                                                        | 93  |

|          | 5.4            | Conclu  | usions .   |                                                        | 94  |

| 6        | AS             | Small-S | cale Qu    | adrotor Helicopter Platform based on ioNeuron          | IS  |

|          | Mo             | dules   |            |                                                        | 96  |

|          | 6.1            | System  | n Overvie  | w                                                      | 96  |

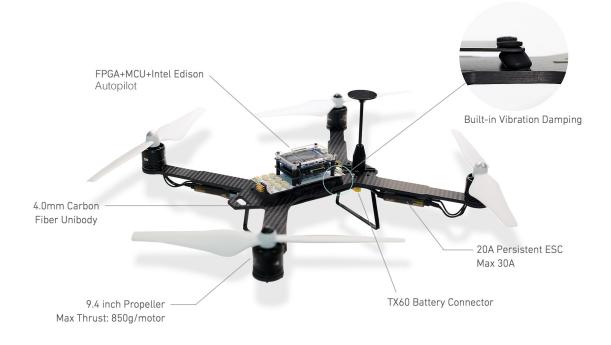

|          | 6.2            | Desigr  | and Con    | struction of a Performance Optimized Quadrotor         | 97  |

|          |                | 6.2.1   | Unibody    | <sup>7</sup> frame                                     | 98  |

|          |                | 6.2.2   | Propulsi   | on System                                              | 100 |

|          |                | 6.2.3   | Design o   | of the ioNeurons Autopilot platform based on FM10,     |     |

|          |                |         | EM4 and    | d C5M                                                  | 102 |

|          |                |         | 6.2.3.1    | Design of the inter-component communication            | 105 |

|          |                |         | 6.2.3.2    | Design of the interface board for ioNeurons processing |     |

|          |                |         |            | modules                                                | 106 |

|          | 6.3            | Result  | s and Co   | nclusion                                               | 110 |

| 7        | Cor            | nclusio | ns         |                                                        | 112 |

| A        | $\mathbf{Sch}$ | ematic  | :          |                                                        | 114 |

| Bi       | ibliog         | graphy  |            |                                                        | 126 |

## List of Tables

| 2.1 | Stackable 30-pin P5KS connector part numbers                           | 21  |

|-----|------------------------------------------------------------------------|-----|

| 3.1 | FM10 PCB Layer Stack                                                   | 29  |

| 3.2 | FM10 24-pin FFC pin-out and signal list                                | 40  |

| 3.3 | FM10 30-pin P5KS Header pin-out and signal list                        | 42  |

| 3.4 | FM10 30-pin P5KS Socket pin-out and signal list                        | 43  |

| 3.5 | Truth table of the SRAM controller address input A0 and UB, LB signals | 45  |

| 4 1 | EM4 DCD Lover Stack                                                    | EO  |

| 4.1 | EM4 PCB Layer Stack                                                    | 58  |

| 4.2 | EM4 24-pin FFC pin-out and signal list                                 | 73  |

| 4.3 | EM4 30-pin P5KS Header pin-out and signal list                         | 77  |

| 4.4 | EM4 30-pin P5KS Socket pin-out and signal list                         | 80  |

| F 1 |                                                                        | 0.0 |

| 5.1 | EM4 PCB Layer Stack                                                    | 88  |

| 5.2 | C5M 24-pin FFC pin-out and signal list                                 | 93  |

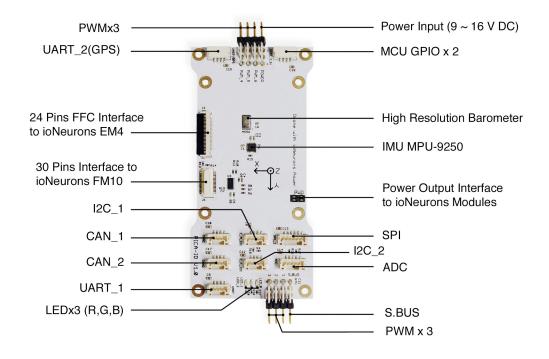

| 6.1 | The pinouts of connectors and sensors on the interface board           | 108 |

| 6 9 | Comparison between Divbards 1 and ioNeurone flight centraller          | 110 |

| 6.2 | Comparison between Pixhawk 1 and ioNeurons flight controller           | 110 |

# List of Figures

| 1.1 | Overview of FPGA architecture [1]                                                                                      | 2  |

|-----|------------------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Overview of MCU architecture [2]                                                                                       | 3  |

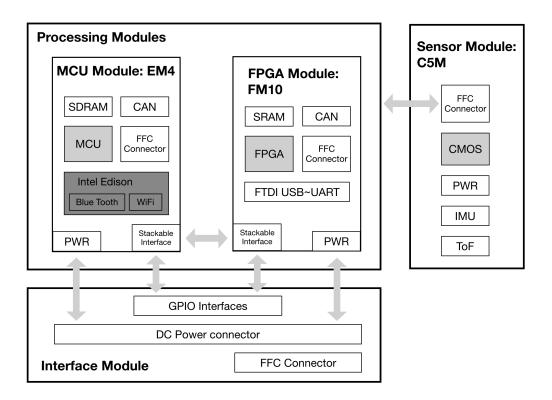

| 2.1 | ioNeurons <sup>TM</sup> platform overview $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$      | 12 |

| 2.2 | ioNeurons <sup>TM</sup> platform assembled by four processing modules $\ . \ . \ .$                                    | 13 |

| 2.3 | FPGA-based dual image sensor development platform                                                                      | 14 |

| 2.4 | RPi-IO interface module                                                                                                | 15 |

| 2.5 | ioNeurons <sup>TM</sup> modules incorporated with Raspberry Pi $\ldots\ldots\ldots\ldots$                              | 16 |

| 2.6 | ioNeurons <sup>TM</sup> system block diagram. $\dots \dots \dots \dots \dots \dots \dots \dots \dots \dots$            | 18 |

| 2.7 | ioNeurons <sup>TM</sup> stackable connectors $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$                 | 20 |

| 2.8 | Via Pins in the stackable connector                                                                                    | 22 |

| 2.9 | Types of Via Pins in the stackable connectors                                                                          | 24 |

| 3.1 | ioNeurons <sup>TM</sup> FM10 $\ldots$ | 26 |

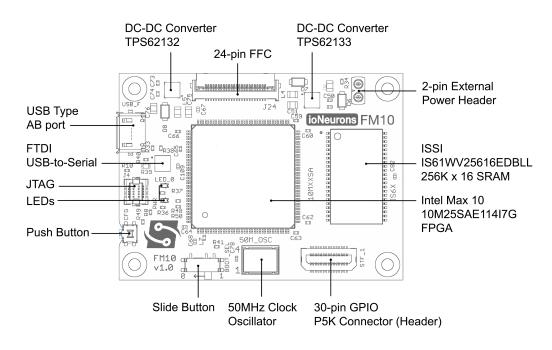

| 3.2 | FM10 module PCB and components (top view)                                                                              | 27 |

| 3.3 | FM10 module PCB and components (bottom view)                                                                           | 27 |

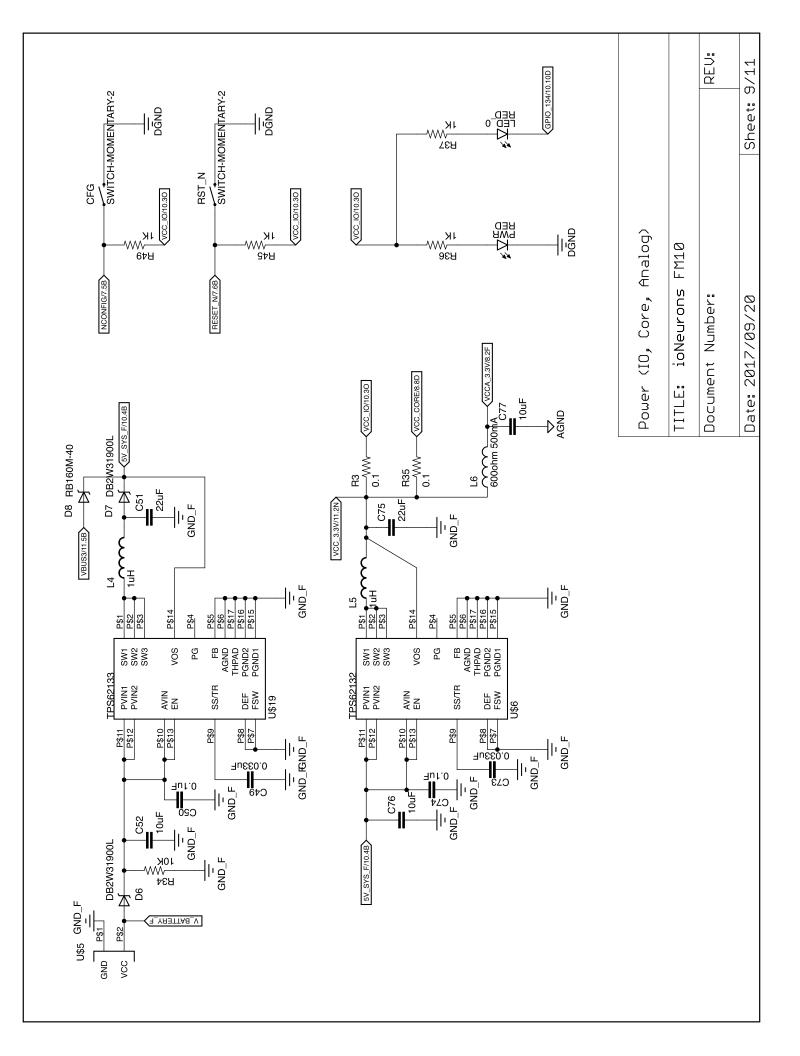

| 3.4 | FM10 module power schematic                                                                                            | 31 |

| 3.5 | Power layer design of FM10's PCB                                                                                       | 32 |

| 3.6 | The SRAM schematic of FM10 module                                                                                      | 34 |

| 3.7 | The CAN transistor schematic of FM10 module                                                                            | 36 |

| 3.8  | The FTDI schematic of FM10 module                                                                                                                             |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3.9  | SRAM Controller block diagram 45                                                                                                                              |

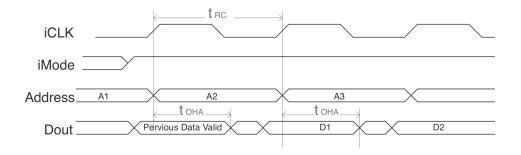

| 3.10 | SRAM Read switch                                                                                                                                              |

| 3.11 | SRAM Write switch                                                                                                                                             |

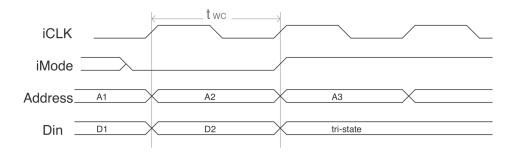

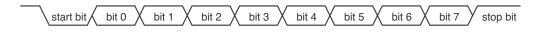

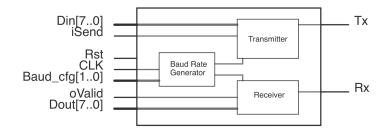

| 3.12 | UART Frame                                                                                                                                                    |

| 3.13 | UART block diagram                                                                                                                                            |

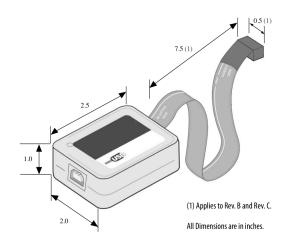

| 3.14 | USB Blaster                                                                                                                                                   |

| 3.15 | JTAG Adapter                                                                                                                                                  |

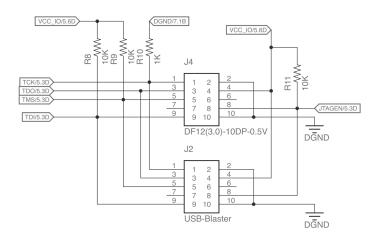

| 3.16 | The JTAG adapter schematic                                                                                                                                    |

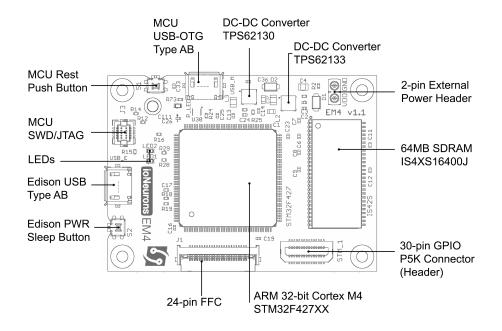

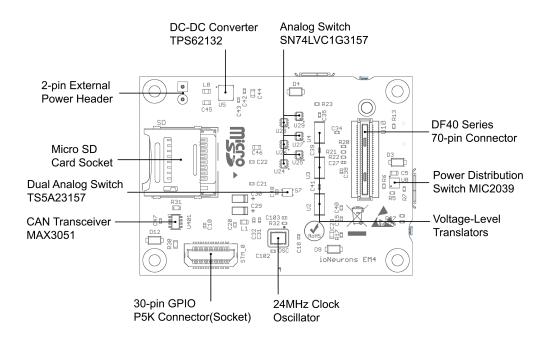

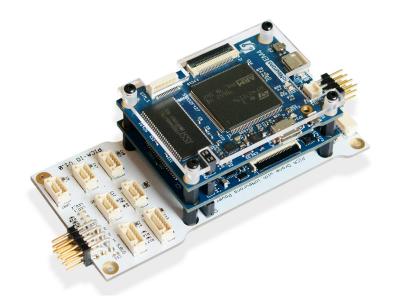

| 4.1  | Top view of ioNeurons <sup>TM</sup> EM4                                                                                                                       |

| 4.2  | Bottom view of ioNeurons <sup>TM</sup> EM4 with $Intel^{\textcircled{R}}$ Edison                                                                              |

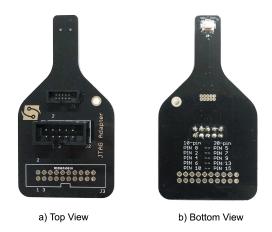

| 4.3  | EM4 Board PCB and component diagram (top view) 56                                                                                                             |

| 4.4  | EM4 Board PCB and component diagram (bottom view) 56                                                                                                          |

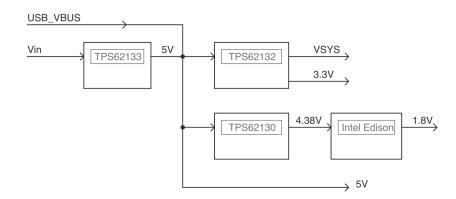

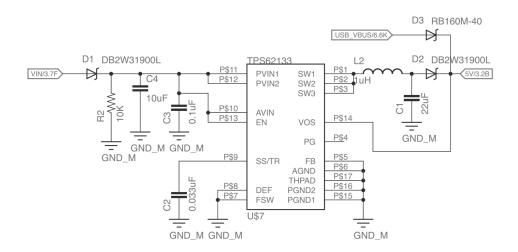

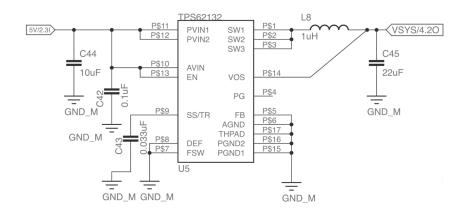

| 4.5  | The Power Tree of EM4 Module                                                                                                                                  |

| 4.6  | EM4 module power schematic: TPS62133 62                                                                                                                       |

| 4.7  | EM4 module power schematic: TPS62132 62                                                                                                                       |

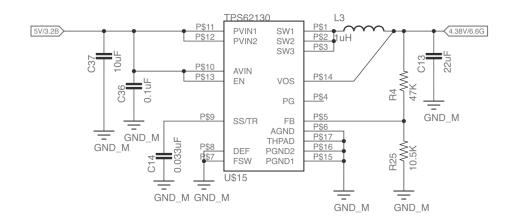

| 4.8  | EM4 module power schematic: TPS62130 63                                                                                                                       |

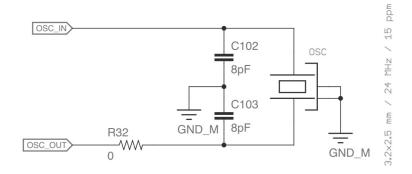

| 4.9  | EM4 OSC schematic: TPS62130                                                                                                                                   |

| 4.10 | EM4 SDRAM schematic: TPS62130 67                                                                                                                              |

| 4.11 | Block diagram of shared SD card slot                                                                                                                          |

| 4.12 | The schematic of EM4 shared SD card slot                                                                                                                      |

| 4.13 | The schematic of CAN transistor in EM4 module                                                                                                                 |

| 4.14 | Block diagram of shared SPI interface with FFC connector                                                                                                      |

| 4.15 | The SWD interface schematic in EM4                                                                                                                            |

| 5.1  | ioNeurons <sup>TM</sup> C5M sensor module $\dots \dots \dots$ |

| 5.2 | The front of the C5M's PCB and its components                                                             | 86  |

|-----|-----------------------------------------------------------------------------------------------------------|-----|

| 5.3 | The back of the C5M's PCB and its components                                                              | 86  |

| 5.4 | The schematic of 2.8 V LDO in C5M                                                                         | 90  |

| 5.5 | The schematic of 1.8 V LDO in C5M $\ldots$                                                                | 90  |

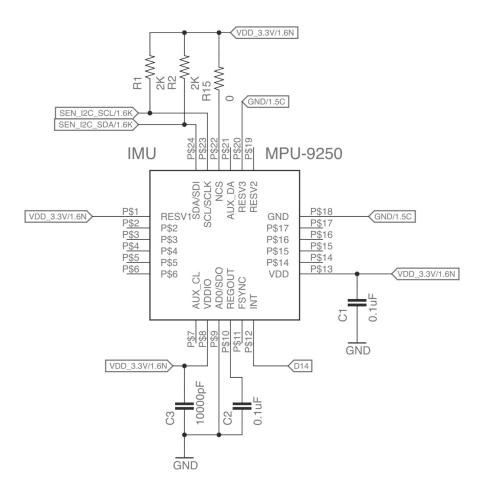

| 5.6 | The application schematic of MPU-9250 in C5M module $\ .$                                                 | 92  |

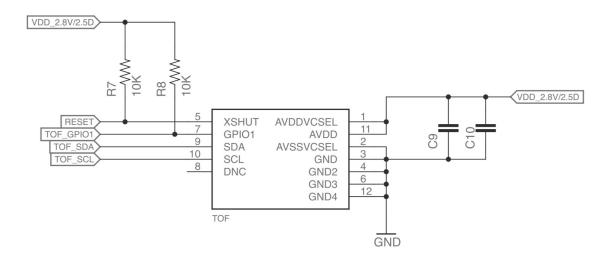

| 5.7 | The application schematic of VL53L0X in C5M module                                                        | 93  |

| 6.1 | The quadrotor built with ioNeurons <sup>TM</sup> modules $\ldots \ldots \ldots \ldots$ .                  | 97  |

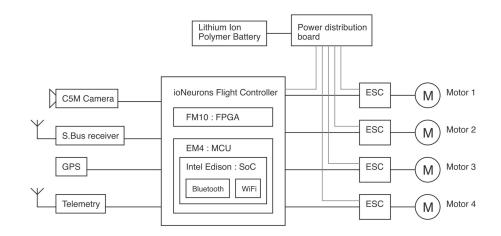

| 6.2 | Block diagram of the ioNeruons quadrotor helicopter                                                       | 98  |

| 6.3 | Basic structure of a quadrotor's frame                                                                    | 99  |

| 6.4 | ioNeurons <sup>TM</sup> Autopilot $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ | 103 |

| 6.5 | Tasks with different real-time requirements                                                               | 104 |

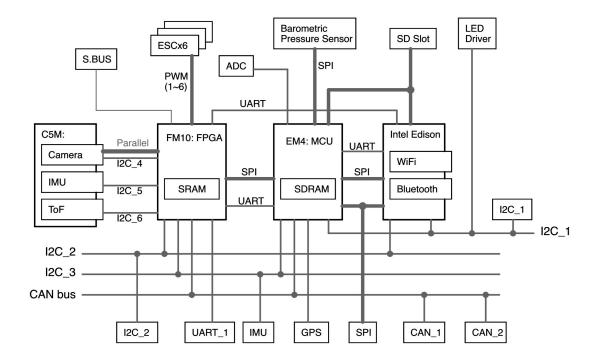

| 6.6 | The block diagram depicts connections and communication protocols                                         |     |

|     | of the flight controller                                                                                  | 106 |

| 6.7 | ioNeurons <sup>TM</sup> quadrotor interface board $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$   | 107 |

### Chapter 1

### Introduction

#### 1.1 Literature Review

#### 1.1.1 FPGA

A field programmable gate array (FPGA) is a kind of integrated circuit (IC) that can be electrically programmed using a hardware description language (HDL) to become almost any kind of digital circuit. In 1984, Altera offered its first programmablelogic chip, EP300 [3], and in 1985 Xilinx co-founders Ross Freeman and Bernard Vonderschmitt invented the first commercially available field programmable gate array, XC2064, which offered 800 gates [4]. FPGA technology has experienced rapid development. Today, the highest density FPGA fabric can have up to 5.5 million logic elements and FPGAs have become a popular implementation media for digital circuits. The development of manufacturing process technology and the continuous improvement of FPGA routing architectures have significantly improved the ability of FPGAs to handle logic operations, making it possible to implement large-scale and complex logic circuits. At the same time, embedded system developers use FPGAs to achieve more complex, large-scale designs based on project requirements. FPGAs provide solutions for embedded designs that offer faster processing speeds and lower power consumption [1].

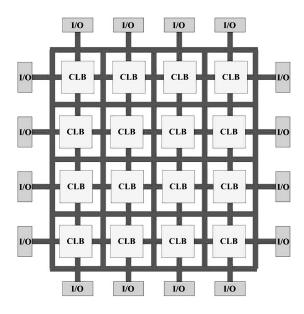

In an FPGA architecture, there are three component parts: configurable logic blocks (CLBs), programmable routings, and I/O blocks. The configurable programmable logic block is a basic logic and storage component which is used to implement logic functions. The programmable routings are used to connect these logic functions, and the I/O blocks connect the logic blocks to off-chip connections through routing interconnects [1]. Figure 1.1 shows a generalized example of FPGA architecture.

Figure 1.1: Overview of FPGA architecture [1]

Compared with Application Specific Integrated Circuits (ASICs), the most considerable advantage of FPGAs is that they provide a cheaper solution and faster time to market for low to medium volume productions. Once the ASIC is fabricated, its functions cannot be modified, but the FPGA can be re-programmed which demonstrates the flexible nature of FPGAs. However, this flexibility is at the expense of speed and size. About 90% of the internal area of FPGAs is the programmable routing interconnects. The flexible nature makes FPGAs larger, slower and more power consuming than ASICs [1]. With the continuous development of FPGA technology, this gap is gradually getting smaller. Compared to microcontrollers, FPGAs still have irreplaceable advantages.

#### 1.1.2 MCU

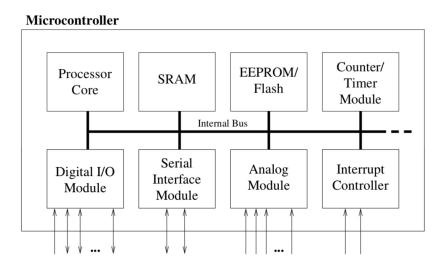

It has been more than 30 years since the first microcontroller TMS1000 was introduced in 1974. Initially, they were used for applications such as calculators, cash registers, watches and measuring instruments. The Intel 8048 was the first microcontroller that became widespread. Nowadays, billions of products are made every year which contain microcontrollers; they are found throughout daily life, industry, and science, in products including household appliances, telecommunication equipment, and the automotive industry. [2]. Figure 1.2 shows the block diagram of a typical microcontroller.

Figure 1.2: Overview of MCU architecture [2]

A microcontroller is a single integrated circuit that, at a minimum, contains a processor, memory, a clock oscillator and input & output interfaces. These are the fundamental elements of a complete computer system. All elements are connected via an internal bus [2] [5].

The processor core is the main part of a microcontroller and consists of an arithmetic logic unit, a control unit, and registers. Its primary function is to run the programme written in memory to perform specific tasks. The memory is an important part that provides storage for the software and data in embedded systems. It can be divided into two categories: non-volatile and volatile memory. The first type, non-volatile memory can retain its contents when power is removed. The Electrically Erasable Programmable Read Only Memory (EEPROM) is a kind of non-volatile memory which is used to save the complete program or an initialization routine. The second type, volatile memory, consists of Random Access Memory (RAM) which stores global variables and loses its entire contents when power is removed [2] [5] [6].

Microcontrollers execute the main program in the normal flow without any concerns, but sometimes higher priority external or internal events must be processed when an interrupt condition occurs. The interrupt controller takes the responsibility for this type of work to interrupt the normal flow operation and go to execute the prioritized task. As soon as the interrupt event is completed, the microcontroller comes back to the main program again and starts to run at the point that was interrupted [2].

The timer is, strictly speaking, a counter module which is another important part of every microcontroller. Most microcontrollers have at least one or more counters to capture and count events and measure intervals. The counter can also be used to trigger interrupts after a certain number of clock cycles, and generate pulse-width modulated (PWM) signals to control motor speed. In default mode, the timer is incremented by the system clock which can be an internal resistor-capacitor oscillator or a more accurate external quartz crystal oscillator. [2] [5].

The Input/Output (I/O) are divided into digital I/O and analog I/O, and both of

them can directly interact with peripheral equipment. The I/Os are the windows of a microcontroller to the outside world. Most I/Os are bidirectional, and can be used as an input and an output. The digital I/Os have two voltage states: logic HIGH and logic LOW. Apart from their digital I/O capabilities, most of them also have many alternate functions to provide more features and save pins. While digital signals on digital I/O take discrete values, analog signals on the analog I/O are the time-varying continuous signals. When using an analog sensor and reading the signal coming from it, the microcontroller must handle an analog signal that changes continuously with time. Analog signals are sampled by Analog Digital Converters (ADCs) through the analog I/Os, and finally converted to digital values inside the microprocessor [2].

#### 1.1.3 Applications of FPGAs and MCUs

Both FPGAs and MCUs have their irreplaceable advantages. In the past research and development, engineers and developers have used them together to implement excellent applications.

Mohammed Raju Hossain designed and implemented a high-performing quadrotor [7], and its flight controller contains an FPGA and an MCU. A proportionalintegral-derivative (PID) technology-based closed loop motor speed controller was also implemented in the same FPGA-based flight controller for precise speed control of the motors. The flight controller combines the powerful computing power of an FPGA and an MCU; however, it is difficult to add other peripherals and sensors to the flight controller because of its integration with the quadrotor frame.

As another example of the processing power of FPGAs, consider the following image processing application. A recent research-based project from Université Paris-Est implemented an IMU-aided image stacking algorithm in a digital camera for Unmanned Aerial Vehicles [8]. The aim of the project is to be able to acquire several images with short exposure time and use an image processing algorithm to produce a stacked image with an equivalent long exposure time. French National Mapping Agency designed the camera that Université Paris-Est used. The camera contains an FPGA and two ARM cortex A9 processors which is a dedicated design to provide powerful real-time image processing ability in a small device, usually such a device is expensive. In the future, they will implement a real-time version by accelerating the image resampling part in the FPGA.

Nicholas Krouglicof presented a method for rigid-body pose measurement from a single perspective view in 1993 [9]. In 2012, the thesis author Teng Wang implemented a computationally efficient contour tracking algorithm [10] with FPGAs; this algorithm can obtain the shape features and generalized moments which are needed for the next step calculation of pose estimation when completing the edge detection of objects. The FPGA can process 27 frames per second (FPS) with image resolution 1024 x 768. Then the MCU used the information provided by the FPGA to complete the rest of the calculations and obtained the pose information of the object. However, at that time the MCU was Atmel's MEGA32U4 8-bit Microcontroller which provides up to 16 MIPS throughput at 16 MHz. This processing speed cannot complete calculations for all 27 frames in a second. Its output is only 5 FPS. This example shows that, although a powerful FPGA is used for image processing, it is still difficult to obtain an ideal processing speed without support from a powerful MCU. The processing power of a system often depends on the weakest part.

Salcic described a microcontroller/FPGA-based prototyping system for embedded applications [11], which proposes an embedded system to make up for the drawbacks that a computer system has in satisfying specific functions of an application. The embedded system combines a standard microcontroller and an FPGA to come up with a new solution in prototyping systems that is called PROTOS. This environment allows the development of hardware and software, efficiently and flexibly, in embedded applications. Using an FPGA to implement the complicated digital system is one of the most popular methods; as well as using an FPGA as a coprocessor to speed up the processing time in some applications in which time is a critical factor [11] [12] [13]. In Salcic's paper, Motorola 68HC11 MCUs and FLEX 8000 FPGAs are used to implement the application. In the system, all other components are coordinated by the 68HC11 MCU that runs in expanded bus mode to deal with external memories and the FPGA. However, the FPGA is dynamically reconfigurable and can be programmed to have different functions as needed in various applications.

Most of the existing computing platforms on the market only contain one type of processing chip. For examples, Arduino and ARM mbed development boards only use MCU chips. And the Raspberry Pi platform only uses SoC chip. If developers need to use FPGAs and work with MUCs to complete tasks, developers usually need to establish the connections by themselves. A US company, Adafruit, developed the MOJO FPGA development board, which includes a Spartan 6 XC6SLX9 FPGA chip, and an ATmega32U4 microcontroller on the same board, however, the microcontroller is only used to configure the FPGA chip, USB communication and reading the analog pins, it cannot really participate in the computing work with the FPGA chip. Alorium Technology company developed an XLR8 FPGA-based Arduino compatible development board. It provides the ability to implement custom logic that accelerates specific functionality that is slow on a microcontroller. However, it only provides 8K logic gates, and cannot extend the number of logic gates through the stack structure.

#### **1.2** Motivation and Scope of Work

In the research and development of electronic robots or mobile devices, developers usually use computing platforms composed of FPGAs, MCUs, or SoCs. Choosing to design a customized computing platform on its own or purchase an existing development platform from the market is usually the first problem developers face.

Comparing the customized development platform and general development platform purchased from the market, they have their own advantages and disadvantages. The customized development platform can meet the requirements of developers in terms of size, performance and power consumption. However, graduate students and developers need to spend a lot of time and energy to complete the preparatory work for hardware design and create a hardware development platform that meets the requirements of the project. During the research and development, depending on the changes or upgrades of the design, the hardware will require making several versions, and each version of hardware will cost a lot of time to complete tests, which seriously affects the progress of the project. Purchasing an existing universal development platform or evaluation board from the market can save a lot of hardware development time, but these platforms are usually bulky and made with unoptimized power consumption. Usually, a development platform only contains one type of processing chips. For examples, Arduino and ARM mbed development boards only use MCU chips. And Raspberry Pi only uses the SoC chip. In a complex project with strict requirements for real-time computing, a single processing chip may restrict the development of programming and function implementation. If a single high-performance microcontroller handles all the tasks, the real-time performance of the calculation becomes worse and worse as the number of sensors and functions increases.

This thesis introduces an FPGA and MCU-based stackable processing platform that provides similar benefits as a customized designed platform without increasing the time of design and test hardware from developers. Based on author's years of work experience in university labs and start-ups, combined with literature reviews, it was concluded that the robots, whether traveling on land, in the water or in the air, all involved applications that were very similar but yet somewhat different. That's when the idea took hold to develop a computational ecosystem that can be easily tailored and adapted to the different application needs of individual developers. This computational ecosystem consists of different modules that allow a platform to contain multiple processors. Multiple communication channels between different processors and sensors are formed with the stackable interface design.

In a project with complex control calculation, developers can classify tasks and operations based on the different requirements of the real-time calculation, and ultimately execute different levels of tasks on different processing modules. The goal is to deliver a performance-optimized stackable hardware platform with a compact size, which has a variety of interfaces and scalable computing power, allowing people to focus on achieving their ideas and saving development time. Developers can mix and match a module's individual capabilities according to the project's needs, making every solution a custom tailored solution without the headache of a custom built platform.

### Chapter 2

### System Description

#### 2.1 Introduction

In the field of computers, the concept of stackable electronic hardware was initially motivated by the demand for memory size and computing power to obtain larger storage space and better computing performance by integrating the contribution of each device. This thesis presents a stack-able development platform with extensible peripherals. For this platform, the extension of computing power is not the only factor considered when designing the hardware stackability feature also allowing the collaboration between different chips provides distinguishing functionality. This platform offers the possibility of having multiple Field-Programmable Gate Arrays(FPGAs) and Micro-Controller Units(MCUs) work together in harmony. Based on the characteristics of FPGAs and MCUs, this collaboration integrates multiple advantages to fulfill the growing demand for applications, especially for hard real-time processing applications.

In the research and development of electronic robots or mobile devices, choosing to design a customized computing platform on its own or purchase an existing development platform from the market is usually the first problem developers face. Comparing the customized development platform and general development platform purchased from the market, they have their own advantages and disadvantages. The customized development platform can meet the requirements of developers in terms of size, performance and power consumption. However, graduate students and developers need to spend a lot of time and energy to complete the preparatory work for hardware design and create a hardware development platform that meets the requirements of the project. During the research and development, depending on the changes or upgrades of the design, the hardware will require making several versions, and each version of hardware will cost a lot of time to complete tests, which seriously affects the progress of the project. Purchasing an existing universal development platform or evaluation board from the market can save a lot of hardware development time, but these platforms are usually bulky and made with unoptimized power consumption.

Many development platforms only contain one type of processing chips. For examples, Arduino and ARM mbed development boards only use MCU chips. And Raspberry Pi only uses the SoC chip. In a complex project with strict requirements for real-time computing, a single processing chip may restrict the development of programming and function implementation. If a single high-performance microcontroller handles all the tasks, the real-time performance of the calculation becomes worse and worse as the number of sensors and functions increases.

An FPGA and MCU-based stackable development platform is introduced as ioNeurons<sup>TM</sup>, which also can integrate with an onboard computing module Intel<sup>®</sup> Edison that can run Linux. This stackable processing platform provides similar benefits as a customized designed platform without increasing the time of design and test hardware from developers. This concept is illustrated in Figure 2.1. FPGAs and MCUs have their own advantages, and the ioNeurons<sup>TM</sup> platform takes advantage of the FPGA, which provides parallelism and has far more capability under the same power requirements as a microprocessor. Without an Operating System(OS), FPGA circuitry is genuinely a hard implementation of program execution, which is more reliable. On the other hand, MCUs provide better portability of design. Generally, MCUs have shorter development iterations and better floating point operations capabilities. FPGA and MCU cooperation can offer better solutions not only in computing speed but also in power consumption and device size to meet size, weight, and power(SWaP) requirements.

Figure 2.1: ioNeurons<sup>TM</sup> platform overview

The ioNeurons<sup>TM</sup> platform includes three types of modules, a processing module, a sensing module, and an interface module. Based on a particular interface design of modules, ioNeurons<sup>TM</sup> processing modules are stackable in no specific order. The number of modules to be stacked is not limited by the power supply, because a power connector and an individual voltage regulator are embedded on each board. The integrated power management chips guarantee a stable power source to each module and ensure every component is working in well-built condition.

The combination of ioNeurons<sup>TM</sup> modules is flexible. A platform could contain one FPGA processing module, and one MCU processing module as shown in Figure 2.1.

However, it may contain two MCU processing modules, and two FPGA processing modules to provide more computing power to developers. This concept is illustrated in Figure 2.2.

Figure 2.2: ioNeurons<sup>TM</sup> platform assembled by four processing modules

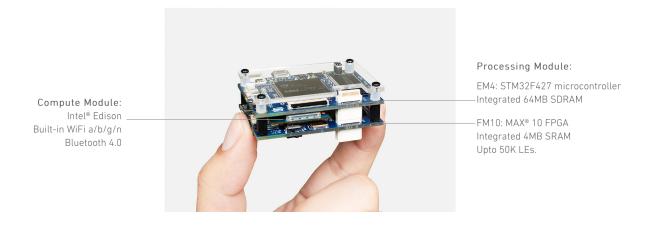

As of now, ioNeurons<sup>TM</sup> has two processing modules: FM10 and EM4. FM10 is a Field-programmable gate array(FPGA) processing module built with an Intel<sup>®</sup> MAX<sup>®</sup> 10 FPGA. The ioNeurons<sup>TM</sup> FM10 introduces a compact-sized FPGA development module suited for prototyping circuit designs such as robots and digital signal processing projects. FM10 can work standalone; however, with the design of stackable connectors, it can also integrate with multiple FM10 or EM4 modules.

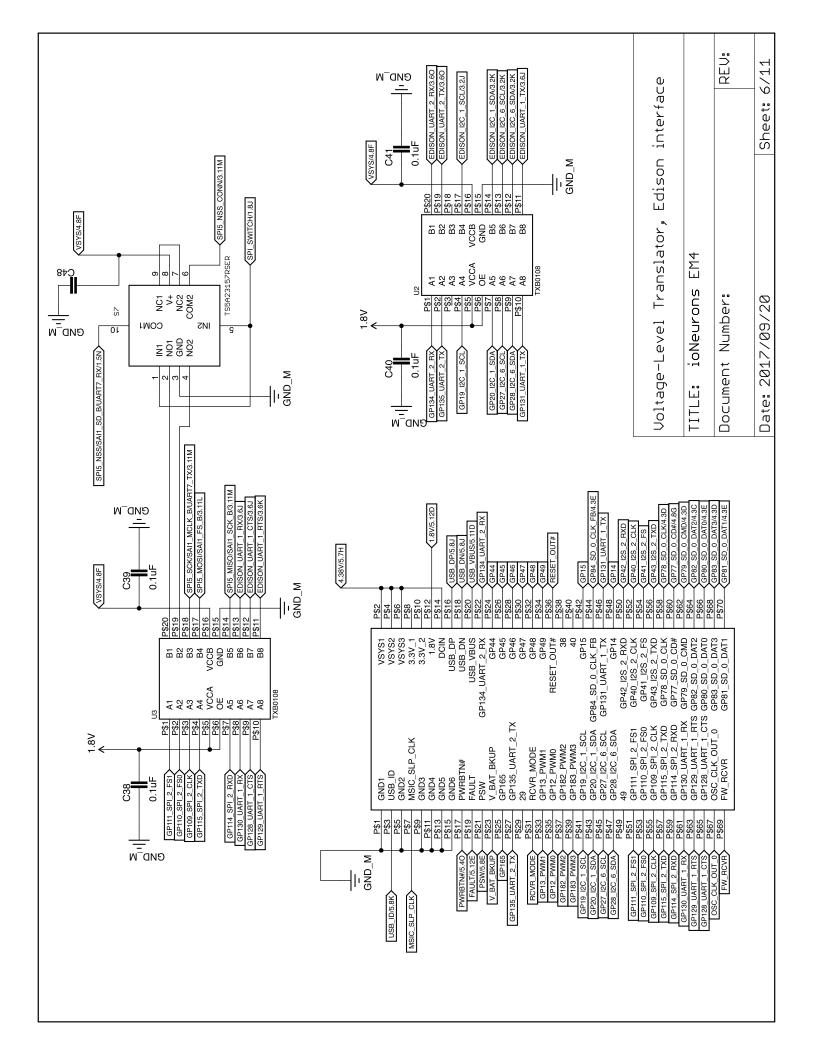

EM4 is a Micro-Controller Unit(MCU) processing module built with ARM<sup>®</sup> Cortex<sup>®</sup>-M4 core STM32 microcontroller in LQFP114 package and an Intel<sup>®</sup> Edison computing module. The ioNeurons<sup>TM</sup> EM4 allows users to easily develop embedded systems and Internet of Things(IoT) applications with a STM32F427XX high-performance MCU and the Edison computing module that interfaces with the EM4 via a 70-pin connector. The EM4 module also integrates a 64-Mbit high speed SDRAM.

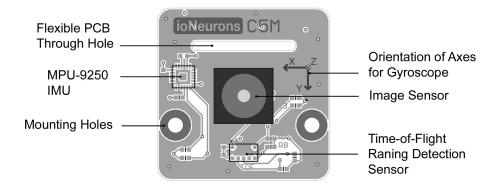

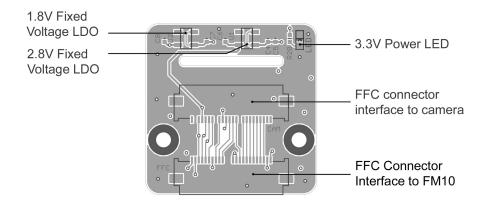

For the sensing module, ioNeurons<sup>TM</sup> C5M is a multi-sensors module that provides reliable color image data, motion data, and range data, which is used in the dual-sensor imaging platform as illustrated in Figure 2.3. It does not only include a 5M-pixel Complementary Metal-Oxide-Semiconductor (CMOS) image sensor, it also comes with an Inertial Measurement Unit (IMU), a magnetometer and an optical Time of Flight (ToF) range sensor. The design of the C5M sensing module will be introduced in detail in Chapter 5.

Figure 2.3: FPGA-based dual image sensor development platform

These modules are team players; developers can mix and match a module's individual capabilities according to the project's needs, making every solution a custom tailored solution without the headache of a custom built platform. As shown in Figure 2.3, it is a dual image sensor development platform built with ioNeurons<sup>TM</sup> modules, which have robust real-time image processing capability. It can be used to implement Simultaneous Localization And Mapping (SLAM) algorithms for robotic mapping and navigation. The platform has two FPGA processing modules and two 5 megapixel color cameras as sensing modules. Each of the cameras is deployed with an independent FPGA and SRAMs to process the raw image data, and the two FPGA modules can also communicate with each other. Comparing to an MCU-based platform, the ioNeurons<sup>TM</sup> based platform takes advantage of the FPGA which can implement image processing algorithms much faster with parallel computing power. Compared to using a PC graphics card to perform image processing, an ioNeurons<sup>TM</sup> modules based platform has a smaller volume and a lower power consumption. This dual image sensor development platform can evaluate algorithms fast, and also meet size, weight, and power (SWaP) requirements.

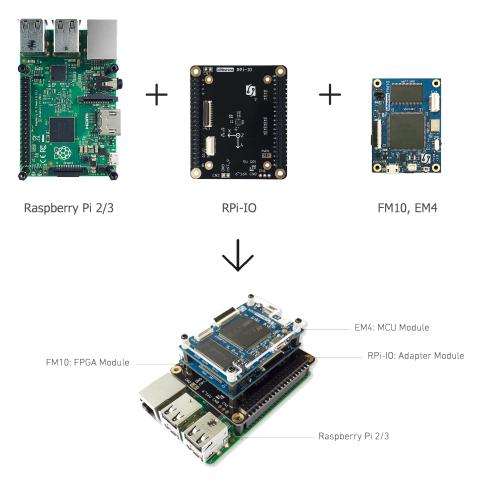

Interface modules can be used as expansion boards allowing ioNeurons<sup>TM</sup> modules to be applied in different application environments to meet various requirements, or to be used to evaluate ioNeurons<sup>TM</sup> modules directly. So far, there are two types of interface module: a general purpose IO module and an RPi-IO module. The general purpose IO module is at the bottom (shown in Figure 2.2), which connects to the processing modules and leads the GPIO out to the vias on the PCB so that users can access the processing modules and attach peripherals.

Figure 2.4: RPi-IO interface module

The RPi-IO module allows connections to the processing modules, and it also integrates a 40-pin standard female connector that can connect to a Raspberry Pi2/3. The RPi-IO can be considered an adapter module for connecting a Raspberry Pi and ioNeurons<sup>TM</sup> FPGA or MCU modules to enhance the computing power of Raspberry Pi. FPGA and MCU modules free up the Linux OS based Raspberry Pi for higher Level tasks, which is especially useful for real-time processing. RPi-IO also offers a motion tracking sensor that combines a 3-axis gyroscope, a 3-axis accelerometer, a 3axis magnetometer and a Digital Motion Processor in a single chip. Figure 2.5 shows the application platform powered by ioNeurons<sup>TM</sup> processing modules and Raspberry

Figure 2.5: ioNeurons<sup>TM</sup> modules incorporated with Raspberry Pi

Pi through RPi-IO.

#### 2.2 Platform Architecture

The ioNeurons<sup>TM</sup> platform consists of three module types. They are categorized into processing modules, sensor modules, and interface modules based on functionality. Figure 2.6 shows the basic ioNeurons<sup>TM</sup> system block diagram. The processing module is the core part of the whole platform. It can connect to sensor modules and even customized interface modules to meet different application requirements.

Every processing module can be powered individually to avoid the interference of a power source, and the output power limitation of a Power Management Integrated Circuit (PMIC). Every processing module possesses its own stackable interface enabling connections between modules or interface modules that provide connectors to peripherals. If a sensor module needs to pass the collected information to multiple processing modules, this sensor module must establish a connection with those processing modules through the stackable interface which supports multiple communication protocols to establish a point-to-multipoint communication network. If a sensor module only needs to deliver its data to one processing module, connection through the flexible flat cable(FFC) connector would be satisfactory. The FFC connector can output 3.3V to power a sensor module, while it provides 20 customizable pins in an FM10 module, and SPI, a UART interface, GPIOs in an EM4 module.

For the EM4, the Intel<sup>®</sup> Edison is an additional optional computing module that contains core system processing and connectivity elements, such as a processor, Wi-Fi, and Bluetooth. The Intel<sup>®</sup> Edison interfaces with EM4 via a 70-pin connector, and EM4 provides input power to the Edison. The Edison module can communicate with a random EM4 and FM10 through the stackable interface in a stacked module

Figure 2.6: ioNeurons  $^{\rm TM}$  system block diagram.

combination. Moreover, two Edison modules can also communicate with each other through the stackable interface if they are in two adjacent EM4 modules.

#### 2.3 Stack-able Interfaces

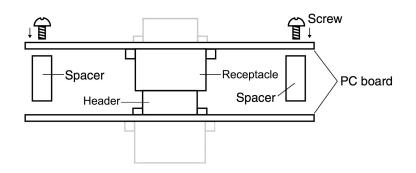

In modern electronic hardware design, modularity has become a trend that makes coordination between different products easier and more cost-effective. In this case, varied types of board-to-board connectors become essential components to achieve connection between modular hardware, and there are thousands of different connectors that can be selected to meet various requirements in projects.

Board-to-board connectors can be categorized by opening direction, mounting type, transfer speed, and functionality. There are two types of opening direction: right angle to board or parallel to board. In terms of mounting type, they can be separated into two groups: surface mount and through-hole. In general, throughhole mounted connectors are stronger, cheaper, and easier for tracing than surface mounted connectors; however, their size tends to be more prominent when having the same amount of pin positions as surface mount connector because of the wider pitch between every two pins. Also, PCB tracing can be significantly affected in the area where the through-hole-pins present, because tracing cannot be applied in the inner layers of PCB, thus leading to an increase of the overall dimensions of the PCB. Based on data transfer speed, there are high-speed connectors and low-speed connectors. Based on functionality, there are data bus connectors, power connectors and combined connectors. Data bus connectors are designed for data transfer, in which the pins are ordinarily small, while power connectors are designed for power supply, in which the pin size is big enough to carry current safely. Combined connectors have both advantages that data bus connector and power connectors have, which implies more expensive cost.

Considering functions and cost-benefit factor, the stack-able interfaces are implemented with a pair of P5KS series narrow pitch, 30-pin, board-to-board connectors from Panasonic Corporation. The header and receptacle are soldered separately on the top and bottom side of each computing module. Every two modules then can be connected via this type of connector; the connector receptacle at the top of one module connects to the connector header at the bottom of another module, integrating with four plastic spacers of a certain height. Figure 2.7 presents the structure of the stack-able connector.

Figure 2.7: ioNeurons<sup>TM</sup> stackable connectors

The Manufacturer part number of the header connector is AXK6S30547YG. This mating receptacle connector is available in three different heights. The board-to-board mating stack height can be 5.0, 5.5, or 8.0 millimeter. Table 2.1 lists the Panasonic part number for the receptacle connector and corresponding DigiKey part numbers for an expansion board. The header of the P5KS connector is on the top, while the socket of the connector is on the bottom. The socket and header are protected from reverse mating by two chamfered corners. When the Intel<sup>®</sup> Edison is not present, mating height 5.0 and 5.5 mm receptacle parts can be used to lower the overall height. Otherwise, when the Intel<sup>®</sup> Edison is present, a mating height 8.0 mm receptacle

| Panasoni | c P/N             | Mating stack height | Digikey P/N   |

|----------|-------------------|---------------------|---------------|

| AXK5S300 | $047 \mathrm{YG}$ | 5.0 mm              | 255-2564-1-ND |

| AXK5S302 | 247YG             | 5.5 mm              | 255-3234-1-ND |

| AXK5S303 | 347YG             | 8.0 mm              | 255-2563-1-ND |

Table 2.1: Stackable 30-pin P5KS connector part numbers

must be chosen to ensure a large enough space between two processing modules to accommodate the Edison module. Figure 2.1 shows the presence of an Intel<sup>®</sup> Edison between an EM4 module and FM10 module with a pair of 8.0 mm mating height connectors.

When designing the stackable interface, a thorough consideration of the flexibility of the connector function is vitally important. Each processing module must be able to satisfy the requirement of high-speed communication between nodes performing distributed collaborative computing. The stackable interface can establish connections for any two processing modules in the stack structure; it also provides the dedicated communication channels supporting multiple protocols for any two adjacent modules. The stackable interface also offers high-speed communication connections between modules.

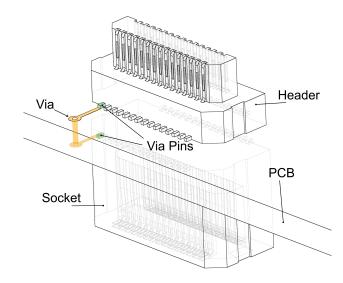

Figure 2.8: Via Pins in the stackable connector

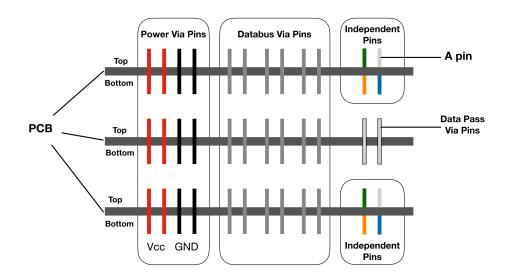

Based on the connecting type, the 60 pins on a pair of the connectors can be divided into two categories: Independent Pin and Via Pin. In this thesis, it is defined that an independent pin is not connected to any other pin of the connector, but directly connected to a pin of the processor or other chips. The Via Pin is defined as any two pins which have a corresponding position on the top header and bottom socket respectively, and are connected through a via in the PCB. Via Pins exist in pairs carrying the same signal. Via Pins provide powerful support for device expansion and cross-module communications. Figure 2.8 shows a pair of Via Pins on the stackable interface.

Via Pins can be categorized as Power Via Pins, Databus Via Pins and Data Pass Via Pins. The definitions of each type are as follows:

Power Via Pins connect a common power source to interface modules or sensor modules and provide a common ground for all of them.

Databus Via Pins connect to a specific pin on the processor of the module. Databus Via Pins not only provide a channel for data exchange, but also allow the processor to act as a node to connect to the data exchange channel. For example, a pair of Databus Via Pins having corresponding positions on multiple processing modules can be connected together to form a channel in the stack structure. This channel passes through all the modules enabling data exchange between any two processors. In I2C communication protocol, these processor nodes are connected to SDA and SCL formed by the Databus Via Pins.

Data Pass Via Pins do not connect to any pins on the processor or any other signals on the module. This type of via pin is isolated from the surroundings, which is to provide a channel allowing the upper layer module to communicate with the lower layer module in a multi-layer processing module stack structure.

Figure 2.9 shows the different types of stackable pins on three processing modules. There are 4 pairs of Via Pins that are set as Power Via Pins: 2 for VCC and 2 for GND. This reinforced dual pair of Via Pins design effectively avoids the possibility of burning the connector due to overload current on a single pair of pins, thereby increasing the capacity to take and supply large current flow.

Figure 2.9: Types of Via Pins in the stackable connectors

### Chapter 3

# Design and Implementation of the FPGA Module

#### 3.1 FM10 Board Overview

The FM10 is a compact-sized FPGA processing module in the ioNeurons<sup>TM</sup> series. It is capable of performing Hard-Real-Time digital logic operations in parallel; It also contains huge resources of Logic Gates(LGs), an 8-channel Analog-to-Digital Converter (ADC), and a 4MB Static Random Access Memory (SRAM) to implement complex digital computations. The primary function of the ADC is to translate analog quantities to digital data for further data processing. The SRAM provides users high-speed access memory with fully static operations, no clock or refresh required. FM10 can take a wide range of voltage input from 3.3V to 16.0V benefiting from an efficient battery management chip; Meanwhile it can provide a 3.3V DC power source at maximum 1A current.

The physical dimension of FM10 is 40.0 mm x 55.0 mm. It has one 24-pin Flat Flex Cable (FFC) connector and two 30-pin P5K series connectors, which permit 40 GPIOs in total and outputs of 3.3V or 5.0V voltage individually. FM10 can easily transfer data to computers because it integrates a Future Technology Devices International (FTDI) USB-to-Serial port chip and a USB type-AB connector.

Figure 3.1:  $ioNeurons^{TM} FM10$

The FM10 can work standalone; however, with the design of the stackable connector, it can also collaborate with multiple FM10 or EM4 modules, which can enhance the computing capacity and increase the number of Input/Output interfaces. FM10 is equipped with user programmable LEDs, push buttons and slide buttons, which allows developers to apply different configurations to meet specific requirements.

The FM10 uses an Intel Max 10 series FPGA chip 10M25SAE114I7G (144-pin EQFP); a single-chip, low-cost, programmable logic device with 25000 Logic Elements(LEs). It also integrates a non-volatile user flash memory and ADCs in a hard IP core block. The ADCs allow the FPGA to process analog signals from real-world sensors. It provides 8-channel 12-bit digital representation of the analog signal being observed with a cumulative sampling rate of up to 1 million samples per seconds (MSPS).

# 3.2 Layout and Components

Figure 3.2: FM10 module PCB and components (top view)

Figure 3.3: FM10 module PCB and components (bottom view)

It is vitally important that every component is placed in a suitable position on a

printed circuit board since it determines the overall dimension, number of layers, and complexity of tracing. Taking production cost and manufacturing techniques into account while keeping the overall size as small as possible, the FM10 employs a 6 layer PCB structure and plating through holes only; no blind via holes or buried via holes were used since they significantly increase the cost of production. The minimum diameter of through holes is 0.15 mm. The solder resist layer covers any through holes which are under 0.35 mm in diameter to protect them and avoid a short circuit, and the stop layer masks will not be applied to these hole locations. The minimum width of a trace is 0.1524 mm, and the minimum clearance between different signal wires is 0.1778 mm. The minimum distance between objects on signal layers and the board dimension is 0.2032 mm, and the thermal isolation is 0.1778 mm. The FR4 insulation material is applied between any two conductor layers. Table 3.1 shows the PCB layer stack. Electroless Nickel Immersion Gold (ENIG) surface treatment is applied on the top and bottom layer during PCB manufacture to prevent the nickel from oxidizing with a thin layer of immersion gold.

When determining the relative position of components, the one having the most pins takes priority because its position has the most significant impact on tracing. The FPGA chip (10M23SAE114I7G) has 144 pins; it is the chip with the largest number of pins on this board. If one side of this chip, where pin number 1 is located, is defined as the chip's left side, most of the high-speed pin and GPIO of the FPGA are located on the bottom side (pin37 to pin72) and right side (pin73 to pin108). Relatively, the SRAM and the FFC connector are the two components that have the next most pins; to reduce the distance between them and the FPGA, the SRAM is placed below the FPGA chip while the FFC connector is placed on the right of the FPGA. In addition, the 50 MHz crystal is placed as close to the FPGA as possible because of its high-frequency clock signal, which is a critical factor to maintain stable

| Layer | Layer Stack                             | Layer Name     | Material      | Thickness         | Plane  |

|-------|-----------------------------------------|----------------|---------------|-------------------|--------|

| 1     |                                         | Top paster     | Sn63/Pb37     | 0.12mm            |        |

| 2     |                                         | Top overlay    |               |                   |        |

| 3     |                                         | Top solder     | Solder resist | 0.01mm            |        |

| 4     |                                         | Top ENIG       | Gold          | $0.05 \mu { m m}$ |        |

| 5     | ·                                       | Тор            | Copper        | 0.018mm           | Signal |

| 6     | /////////////////////////////////////// | Dielectric 1   | FR-4 TG140    | 0.0913mm          |        |

| 7     | ·                                       | Layer 2        | Copper        | 0.03mm            | D_GND  |

| 8     |                                         | Dielectric 2   | FR-4 TG140    | 0.53mm            |        |

| 9     |                                         | Layer 3        | Copper        | 0.03mm            | Signal |

| 10    | /////////////////////////////////////// | Dielectric 3   | FR-4 TG140    | 0.1056mm          |        |

| 11    |                                         | Layer 4        | Copper        | 0.03mm            | 5V_SYS |

| 12    |                                         | Dielectric 4   | FR-4 TG140    | $0.53\mathrm{mm}$ |        |

| 13    | ·                                       | Layer 5        | Copper        | 0.03mm            | A_GND  |

| 14    | /////////////////////////////////////// | Dielectric 6   | FR-4 TG140    | 0.0913mm          |        |

| 15    |                                         | Bottom         | Copper        | 0.018mm           | Signal |

| 16    |                                         | Bottom ENIG    | Gold          | $0.05 \mu { m m}$ |        |

| 17    |                                         | Bottom solder  | Solder resist | 0.01mm            |        |

| 18    |                                         | Bottom overlay |               |                   |        |

| 19    |                                         | Bottom paster  | Sn63/Pb37     | 0.12mm            |        |

# Table 3.1: FM10 PCB Layer Stack

operation of the whole system.

In order to reduce electromagnetic interference (EMI), the FM10 6-layer structure adopts the top layer, the third layer, and the bottom layer as signal layers, in which copper is paved in the area around signal routes and connects to the ground plane. The second and the fifth layer are the ground planes, and the fourth layer is the power plane. The solid ground plane will minimize inductance, and any signal plane close to the ground plane will have continuous return current.

Decoupling capacitors are placed near the power pins of each chip. When the chip's payload suddenly increases, the circuit tries to increase its current, however the inductance in the power supply line hinders the current rising and causes the power line voltage to sag. At this time the decoupling capacitors provide short bursts of current to maintain the voltage at a stable level.

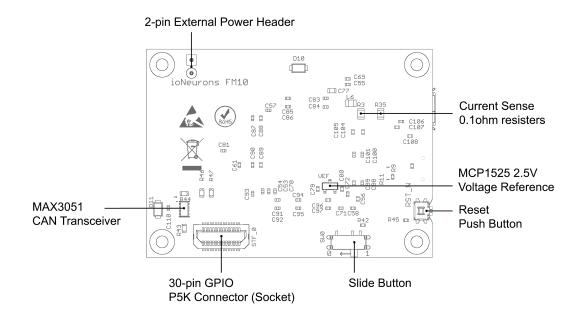

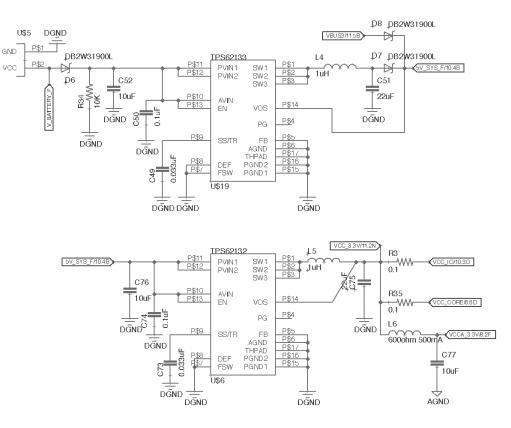

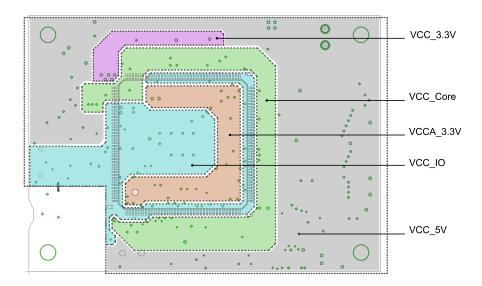

#### 3.2.1 Power management and distribution

The FM10 can be powered by a DC power supply, USB, and Li-Ion or other batteries because of its high-performance power management module design which has a wide operating input voltage range from 3.3 V to 17 V. It allows FM10 to easily work in various application environments with flexible power requirements. At the same time, FM10 can provide 5 V and 3.3 V power sources, which allows small sensor modules that connect to FM10 to be powered, thus avoiding redundant power circuit design for external sensors.

The power management module of FM10 has two synchronous Step-Down DC to DC Converters from Texas Instruments; their part numbers are TPS62133 and TPS62132. Both of them adopt 16-pin 3x3 mm QFN packages and can provide 3 A of continuous output current at 3.3 V and 5 V respectively with a maximum up to 95% converting efficiency. These two chips are made for mobile application platforms;

They use advanced regulation topology (DCS-Control) that combines advantages of multiple control modes, which can monitor output voltage changes and feed it directly to a fast comparator to set the switching frequency. This technology provides immediate response for dynamic load changes to achieve fast and stable voltage operation. These DC to DC converters also prevent the circuit from shorting and overloading. When a load or a short circuit is detected and the output voltage drops below 0.5V, the current limit will be reduced to 1.6A immediately. If the output voltage picks up above 0.5V again, the device recovers to the normal operating mode. Figure 3.4 shows the schematic of the voltage converter connectivity in FM10. A 1.0uH inductor and a 22.0uF capacitor are connected to its output as an external LC output filter.

Figure 3.4: FM10 module power schematic

The chip, TPS62133, accepts a maximum of 17.0 V input power, and its output voltage is fixed 5.0 V, which is the input voltage for the next level DC-DC converter

chip TPS62132. A DB2W900L diode from Panasonic Electronic Components is placed between the two chips to prevent reverse current. Moreover, the USB connector also has a 5.0V power line connecting to the input of TPS62132 via a DB2W900L diode, and this allows the system to also be powered by a USB connector directly. TPS62132 provides 3.3 V output voltage to the FPGA and other chips whose rated voltages are 3.3 V. The two diodes (D8, D7) feature 30.0 V reverse breakdown voltage which prevents the USB from being burnt by a high reverse voltage, and allows FM10 to be powered by battery and USB at the same time.

Figure 3.5: Power layer design of FM10's PCB

In order to provide the FPGA chip with a clean, low-noise power supply, a power tree was designed to separate the 3.3V external power supply into different groups serving as multiple inputs to the MAX 10 device via VCC\_ONE, VCC\_IO and VCCA. Figure 3.5 shows the power layer design in the PCB. The VCC\_3.3V power supply is divided into VCC\_Core, VCC\_3.3V and VCC\_IO to power different portions varying in function on the FPGA chip. This reduces the interference between different functional groups which can arise due to voltage fluctuations caused by the

different current demands of each functional group.

#### 3.2.2 FPGA: 10M25SAE114I7G

The chip, 10M255AE144I7G, belongs to Intel<sup>®</sup> MAX10 series; it is single-supply FPGA, which requires only 1 external power supply of 3.3 V [14]. It is built on 55nm embedded NOR flash technology, providing 25000 logic elements, integrated Analogto-Digital Converters (ADC) and 2 MB of user flash memory to store configuration files and user data. The ADC provides 8 channels with 12-bit digital representation of the analog signals being observed, with a cumulative sampling rate of up to 1million samples per second (MSPS). The user flash memory provides ideal storage space to store non-volatile information. It uses an EQFP package, offering 144 pins, in which 101 pins have general-purpose input/output (GPIO) functionality. In addition, the speed grade -7I is another important parameter in design. There is no consistent definition of a speed grade for all FPGA/CPLD devices. The -7I for this chip means it is industrial class; the pin-to-pin delay is 7 nanoseconds. In other words, the smaller the number, the faster the speed, which has an impact on the selection of SRAM.

The maximum power consumption of the 10M25S chip can be 2.943 W, which comes from the VCC\_ONE pins. All VCC\_ONE pins are powered by VCC\_Core. If the user's design is beyond the maximum power consumption, it will cause that part of the function to perform abnormally. The minimum system design includes the power supply, crystal oscillator, voltage reference and adapter interface. The type of crystal oscillator is CB3LV-3C-50M0000 from CTS Electronics Components providing a 50 MHz clock signal. The voltage reference chip, MCP1525 from Microchip, provides a 2.5 V precision voltage reference that has initial maximum tolerance of  $\pm 1\%$ , and temperature stability of  $\pm 50$  ppm/c<sup>o</sup>.

#### 3.2.3 SRAM: IS61WV25616EDBLL

Static Random Access Memory (SRAM) is a kind of random access memory. The 'static' means the memory can store the data permanently as long as it is powered. Data does not need to be refreshed periodically and would not be lost. By contrast, the data in SDRAM needs to refreshed periodically to ensure the effectiveness of the data. Both of them are called volatile memory since the stored data would be lost if the power is cut off. Compared to SDRAM, the SRAM has advantages of faster speed, lower power consumption, especially during idle, and easier control. This is also the reason that SRAM is selected for FM10. The disadvantages of SRAM are more complicated internal circuit and high production cost, therefore, it is not suitable to be used in the applications requiring large storage.

Figure 3.6: The SRAM schematic of FM10 module

The ISSI, IS61WV25616EDBLL, on FM10 is a high-speed asynchronous CMOS SRAM chip, which has 4194304 bits of memory organized as 262144 words by 16 bits. This chip can satisfy most of the application requirements that need high computing speed. The asynchronous means that the read and write operation is triggered by rising or falling edge of the control signal or the address signal. The read and write can occur at any time. However, synchronous SRAM has one clock signal, thus all the operations are driven by the clock signal. In other words, the read and write operation only happens at expected times. The access time of IS61Wv25616EDBLL is  $8 \sim 10$  ns, which is faster than the FPGA's clock signal. In another words, the SRAM can be accessed and operated by the FPGA on every clock cycle meaning there are no waiting clock cycles. Figure 3.6 shows how the SRAM is powered in FM10 and its pin connection to FPGA.

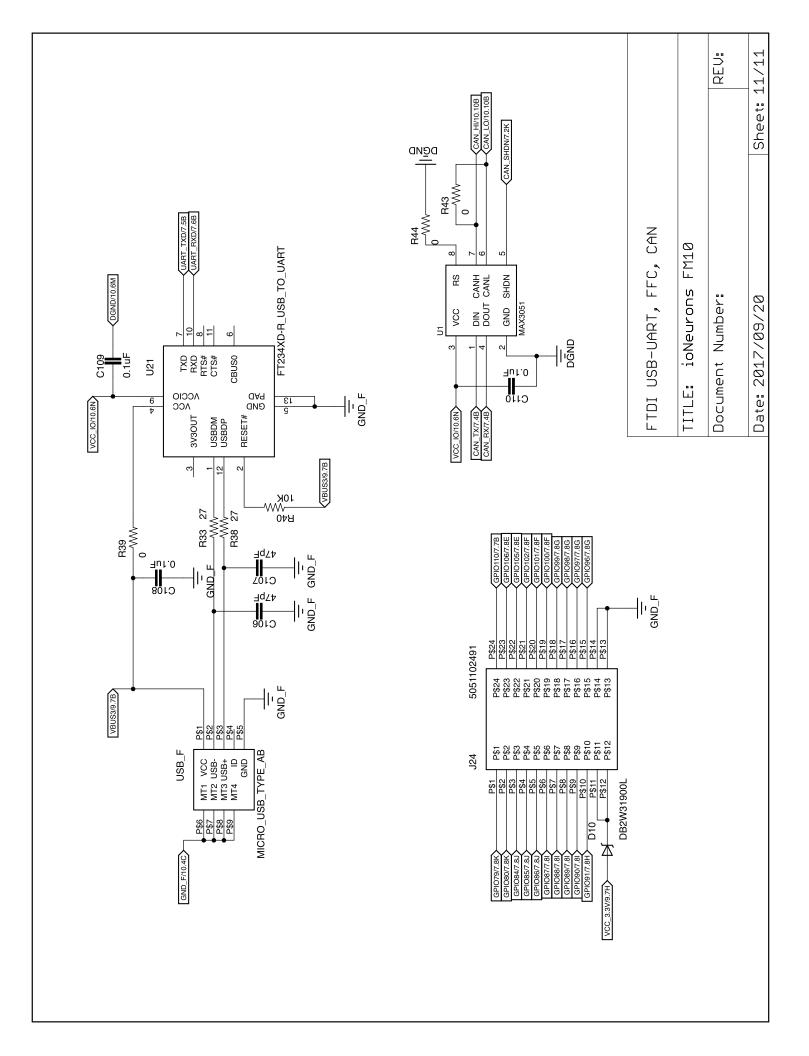

#### 3.2.4 CAN Transceiver

A CAN bus standing for Controller Area Network bus is a robust data communication protocol that was initially used on vehicles enabling devices to communicate with each other, but now it is not limited to use in the automobile field only. CAN's high performance and reliability have been recognized, and are widely used in industrial automation, ships, medical equipment, and so on. The CAN transceiver makes the FM10 interfaces more friendly to access CAN network, and this greatly increases the applications of FM10. The CAN bus provides powerful support for distributed control platform which is using ioNeurons<sup>TM</sup> processing modules, to realize real-time and reliable data communication between various nodes.

Unlike other data transfer protocols, a pair of CAN bus twisted wires allows more than two devices to connect in parallel and exchange data; in other words, it is not a fixed point-to-point communication protocol; it can create a communication network and offer flexible point-to-point or point-to-multipoint communications. Those devices connecting to a CAN bus are Electronic Control Units (ECUs) also known as nodes. A node can be a simple I/O device or a complicated embedded computer. Any of the devices can be a host as long as it has the corresponding functionality. Once a device broadcasts a message on the bus, every other device will listen and identify if they are interested in this message, and then the message will be received by the one that is interested.

To transfer data, CAN bus signalling uses differential signals on the two wires: one is called CAN\_high, the other one is called CAN\_low. When CAN\_high is driven to 5 V and CAN\_low is driven to 0V, the transmission is recognized as dominant state representing logic level 0. When neither of them is driven, they are levelled to the reference voltage which is 2.5 V, and at this time, the transmission is recognized as recessive state representing logic level 1. In the physical layer, these two wires are twisted together in order to reduce the influence of electromagnetic interference. Two 120  $\Omega$  termination resistors are placed on each end of the CAN bus to suppress signal reflections.

Figure 3.7: The CAN transistor schematic of FM10 module

In order to generate the differential signals, a transceiver chip that is based on CAN bus protocol is required. In FM10, the transceiver chip is MAX3051 from Maxim Integrated. This chip can translate the logic level signal 0 or 1 from the host controller to differential signals that are transmitted on the CAN bus. It also features four different modes of operation that enables data transfer speed control. The schematic in Figure 3.7 shows a typical operating circuit.

#### 3.2.5 FTDI

As the rapid development of laptops continues toward lighter and thinner, many traditional connectors are replaced by those having lower volume and faster transfer speeds. Universal Serial Bus (USB) facilitates the communication between computer and other peripherals to a large extent. USB is standardized as an industrial standard that prescribes the communication protocol, cable, and connector type. It substitutes the traditional serial communication ports and the connectors that were previously used such as the D-subminiature connector. However, in the development of FPGA and embedded systems, traditional serial communication protocols take less resources, and are relatively easy to implement, so they still play an important role in data transfer and debugging of embedded developments. Universal asynchronous receivertransmitter (UART) is a very common communication protocol. In order to bridge the connection between USB on the computer and serial output on the FPGA via the UART communication protocol, a UART to USB converter chip from FTDI is needed. A corresponding driver must be installed in the computer operating system, to allow the USB port to be recognized as a virtual serial communication port.

FT234XD USB to basic UART IC provides USB and an asynchronous serial data transfer interface, which is fully compliant with the USB 2.0 specification. Its UART interface has support for 7 and 8 data bits with 1 or 2 stop bits. The data transfer rate can be configured from 300 baud to 3M baud rate. Figure 3.8 illustrates the FT234XD typical configuration with a USB bus powered design. The UART\_TXD and UART\_RXD are connected to PIN\_124 and PIN\_120 on the FPGA through 0  $\Omega$  resistors or a suitable ferrite bead according to the current; These can reduce the EMI noise that the FT234XD radiates to the USB host over the USB cable.

Figure 3.8: The FTDI schematic of FM10 module

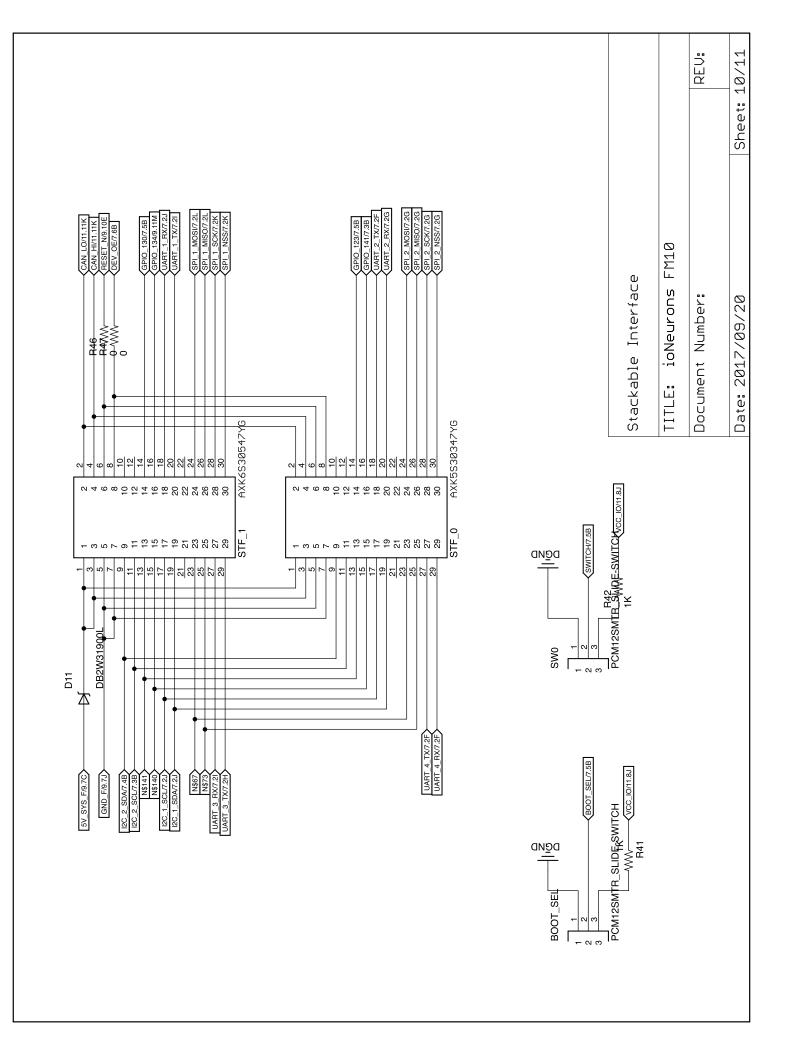

# **3.3** Interfaces and pin mapping

As a processing module, the selection of suitable connectors for FM10 directly impacts the user experience and the way its used. In order to facilitate adoption of FM10 in as many projects as possible and considering the cost-benefit factor, FM10 is designed to use two different types of connector: Flat Flex Cable (FFC) connectors and P5KS series board to board narrow pitch connectors; Both of them are classified as surface mount type and high-speed connectors. The primary function of FFC is to provide and expand the connectivity to other peripherals. P5KS connectors are utilized for implementing expandable and stackable features between ioNeurons<sup>TM</sup> modules.

The FFC connector mounted on FM10 module is 24-pin with a 0.4mm pitch, fitting a 12mm wide flat flex cable, which can connect FM10 with another module. In the 24-pin FFC connector, 20 out of 24 pins are defined as data transfer pins, and other 4 pins are set as power pins: 2 for VCC and 2 for GND. This reinforced dual power pin design effectively avoids the possibility of burning the connector due to overloading current on a single pin, thereby increasing the capacity to take and supply large current flow. In addition, the FFC connector has a double-bottom-contact terminal design which can remove dust and contaminants better than single-bottom-contact terminals. Two contact points on each pin also provides stable redundant contact forces for secure electrical reliability. The FFC is placed at upper side of the FPGA chip, and it is very close to FPGA Pin\_73 ~ Pin\_108. Most of these pins are able to carry high-speed differential signals. Not only does this layout design shorten the trace length between FPGA and FCC connector, but it also reduces the EMI noise. FM10 chooses to use the parallel-to-board type FFC connector to achieve more space between two adjacent boards thus making it easier for users to install cables.

FM10 uses Panasonic P5KS series narrow pitch connectors for communicating between ioNeurons<sup>TM</sup> processing modules. A pair of 30-pin connectors are soldered on the top and bottom side of FM10. The header of P5KS connector is on the top, while the socket of the connector is on the bottom. The socket and header are protected from reverse mating by two chamfered corners.

Each connector has a total of 30 pins, which are distributed in two rows with a pin-to-pin pitch of 0.5 mm. It was chosen to be used on FM10 due to the diverse mating height choices for this type of connector. In the design, an 8.0 mm mating height is used to avoid collision between the Intel<sup>®</sup> Edison module and FM10 when the modules are assembled. Both the header and socket have 4 pins that were defined as power pins: 2 for VCC and 2 for GND; each pin can take up to 0.5A current. This reinforced design effectively avoids the possibility of burning the connector due to large current flow, thereby increasing the capacity to take and supply large current flow. A DB2W900L diode from Panasonic Electronic Components is placed between the power source and power pins to prevent current from going backward. In other words, users cannot power FM10 via power pins from the P5KS connector, but FM10 can provide a 5.0 V power output. Table 3.3 and Table 3.4 show the connection

| FFC Pin Number |         | FPGA Pin Name | Function |

|----------------|---------|---------------|----------|

| 1              | FFC_0   | PIN_79        | GPIO     |

| 2              | FFC_1   | PIN_80        | GPIO     |

| 3              | FFC_2   | PIN_84        | GPIO     |

| 4              | FFC_3   | PIN_85        | GPIO     |

| 5              | FFC_4   | PIN_86        | GPIO     |

| 6              | FFC_5   | PIN_87        | GPIO     |

| 7              | FFC_6   | PIN_88        | GPIO     |

| 8              | FFC_7   | PIN_89        | GPIO     |

| 9              | FFC_8   | PIN_90        | GPIO     |

| 10             | FFC_9   | PIN_91        | GPIO     |

| 11             | FFC_VCC | N/A           | VCC 3.3V |

| 12             | FFC_VCC | N/A           | VCC 3.3V |

| 13             | FFC_GND | N/A           | GND      |

| 14             | FFC_GND | N/A           | GND      |

| 15             | FFC_10  | PIN_96        | GPIO     |

| 16             | FFC_11  | PIN_97        | GPIO     |

| 17             | FFC_12  | PIN_98        | GPIO     |

| 18             | FFC_13  | PIN_99        | GPIO     |

| 19             | FFC_14  | PIN_100       | GPIO     |

| 20             | FFC_15  | PIN_101       | GPIO     |

| 21             | FFC_16  | PIN_102       | GPIO     |

| 22             | FFC_17  | PIN_105       | GPIO     |

| 23             | FFC_18  | PIN_106       | GPIO     |

| 24             | FFC_19  | PIN_110       | GPIO     |

Table 3.2: FM10 24-pin FFC pin-out and signal list

between the 30-pin connectors and the FPGA with pin's functionalities.

In this thesis, it is defined that any pins on the top header and the bottom socket that have the corresponding position to each other and are connected through PCB via, are Via Pins. A pair of Via Pins carry the same signal. The FM10's P5KS connectors contain 16 pairs of Via Pins: some of them are connected to the FPGA's specific pins to build up the I2C or CAN bus communication circuit; while some of them are just pierced forming a bridge without connecting to FPGA. Via Pins can solve issues such as device expansion, module perpendicular connectivity and crossmodule communications.

| P5K Pin<br>Number | P5K Pin<br>Name | FPGA Pin<br>Name | Via Pin | Function |

|-------------------|-----------------|------------------|---------|----------|

| 1                 | HS_1            | N/A              | Yes     | VCC 5V   |

| 2                 | HS_2            | N/A              | Yes     | CAN_LO   |

| 3                 | HS_3            | N/A              | Yes     | VCC 5V   |

| 4                 | HS_4            | N/A              | Yes     | CAN_HI   |

| 5                 | HS_5            | N/A              | Yes     | GND      |

| 6                 | HS_6            | PIN_87           | Yes     | RESET_N  |

| 7                 | HS_7            | N/A              | Yes     | GND      |

| 8                 | HS_8            | PIN_122          | Yes     | DEV_OE   |

| 9                 | HS_9            | PIN_135          | Yes     | GPIO     |

| 10                | reserved        | N/A              | N/A     | N/A      |

| 11                | HS_11           | PIN_140          | Yes     | GPIO     |

| 12                | reserved        | N/A              | N/A     | N/A      |

| 13                | HS_13           | N/A              | Yes     | N/A      |

| 14                | H_14            | PIN_130          | No      | GPIO     |

| 15                | HS_15           | N/A              | Yes     | N/A      |

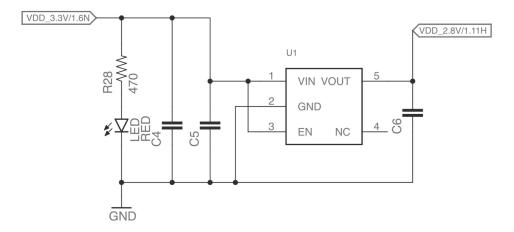

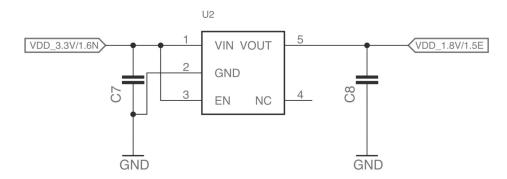

| 16                | H_16            | PIN_134          | No      | GPIO     |