# ADVANCED ANALOG LAYOUT DESIGN AUTOMATION IN COMPLIANCE WITH DENSITY UNIFORMITY

by

<sup>©</sup>Gholamreza Shomalnasab

A thesis submitted to the School of Graduate Studies in partial fulfillment of the requirements for the Degree of Doctor of Philosophy

**Faculty of Engineering of Applied Science**

Memorial University of Newfoundland

October, 2017

St. John's Newfoundland and Labrador Canada

## **ABSTRACT**

To fabricate a reliable integrated circuit chip, foundries follow specific design rules and layout processing techniques. One of the parameters, which affect circuit performance and final electronic product quality, is the variation of thickness for each semiconductor layer within the fabricated chips. The thickness is closely dependent on the density of geometric features on that layer. Therefore, to ensure consistent thickness, foundries normally have to seriously control distribution of the feature density on each layer by using post-processing operations.

In this research, the methods of controlling feature density distribution on different layers of an analog layout during the process of layout migration from an old technology to a new one or updated design specifications in the same technology have been investigated. We aim to achieve density-uniformity-aware layout retargeting for facilitating manufacturing process in the advanced technologies. This can offer an advantage right to the design stage for the designers to evaluate the effects of applying density uniformity to their drafted layouts, which are otherwise usually done by the foundries at the final manufacturing stage without considering circuit performance. Layout modification for density uniformity includes component position change and size modification, which may induce crosstalk noise caused by extra parasitic capacitance. To effectively control this effect, we have also investigated and proposed a simple yet accurate analytic method to model the parasitic capacitance on multi-layer VLSI chips. Supported by this capacitance modeling research, a unique methodology to deal with

density-uniformity-aware analog layout retargeting with the capability of parasitic capacitance control has been presented. The proposed operations include layout geometry position rearrangement, interconnect size modification, and extra dummy fill insertion for enhancing layout density uniformity. All of these operations are holistically coordinated by a linear programming optimization scheme. The experimental results demonstrate the efficacy of the proposed methodology compared to the popular digital solutions in terms of minimum density variation and acute parasitic capacitance control.

## **ACKNOWLEDGEMENT**

First and foremost, I would like to express my sincere appreciation to my advisor, Dr. Lihong Zhang, for his guidance, inspiration, suggestions, criticism and financial support that he has provided throughout the course of my research and studies. He always encourages me to conduct innovative research and trains me to be an independent researcher. Special thanks are also extended to Dr. Howard Heys for his time and support as my co-supervisor for the first year of my PhD program and his instruction as one member on my Supervisory Committee. I also thank Dr. Ramachandra Venkatesan for taking the time to review this dissertation and serving on the Supervisory Committee.

I also gratefully acknowledge the Faculty of Engineering and Applied Science, the Memorial University of Newfoundland, Natural Sciences and Engineering Research Council of Canada (NSERC), Canada Foundation for Innovation (CFI), Research and Development Corporation (RDC) of Newfoundland and Labrador (through its Industrial Research and Innovation Fund and ArcticTECH R&D Award), for the financial support.

My appreciations also go to the entire group members of the CADLAMS and my colleagues: Xuan Dong, Tuotian Liao, Mohammad Torabi for their friendship and assistance in the course of my research programme. Additional gratitude is given to my friends Remzi Cej and Mohammad Hekmatnejad which have been a great part of my life at Memorial University.

Finally, I would like to express my special appreciation to my parents, Faramarz Shomalnasab and Sedigheh Tohidi, and my sisters for their continued support and love which support me to pursue my ambitions. The deepest thanks are expressed to my lovely wife, Khoshrooz Kazemi, for her endless love, inspiration, encouragement and patience.

# **TABLE OF CONTENTS**

| ABSTRACT                                  | II  |

|-------------------------------------------|-----|

| ACKNOWLEDGEMENT                           | IV  |

| TABLE OF CONTENTS                         | VI  |

| LIST OF FIGURES                           | IX  |

| LIST OF TABLES                            | XII |

| LIST OF SYMBOLS AND ABBREVIATIONS         |     |

| CHAPTER 1 INTRODUCTION                    |     |

| 1.1 Background                            |     |

| 1.2 Statement of Problems                 |     |

| 1.3 Research Objectives                   | 4   |

| 1.4 Structure of the Thesis               | 5   |

| CHAPTER 2 LITERATURE REVIEW               | 7   |

| 2.1 Introduction                          | 7   |

| 2.2 Capacitance Modeling                  | 7   |

| 2.3 Layout Synthesis and Retargeting      | 14  |

| 2.4 Density Analysis and Fill Synthesis   | 18  |

| 2.5 Summary                               | 26  |

| CHAPTER 3 ANALATIC MODELING OF PARASITIC  |     |

| CAPACITANCE                               | 27  |

| 3.1 Introduction                          | 27  |

| 3.2 Preliminaries of Capacitance Modeling | 27  |

| 3.3 Modeling of Fringe Capacitance        | 29  |

| 3.3.1 Substrate Capacitance               | 30  |

| 3.3.2 Coupling Capacitance                | 35  |

| 3.3.3 Lateral Capacitance                 | 39  |

| 3.3.4 Linear Model                        | 41  |

| 3 3 5 Curve-Fitting Technique             | 42  |

| 3.4 Summary                                                           | 44  |

|-----------------------------------------------------------------------|-----|

| CHAPTER 4 DENSITY-UNIFORMITY-AWARE ANALOG                             |     |

| LAYOUT RETARGETING                                                    | 45  |

| 4.1 Introduction                                                      | 45  |

| 4.2 Regular Retargeting Process                                       | 46  |

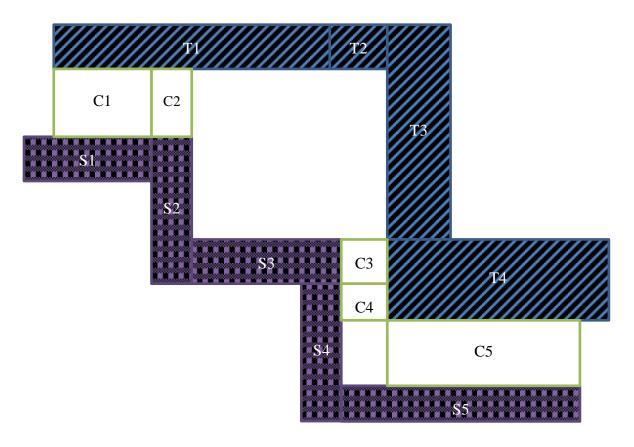

| 4.3 Density-Uniformity-Aware Analog Layout Retargeting Process Flow.  | 52  |

| 4.4 Linear-Programming Formulation and Optimization                   | 56  |

| 4.4.1 Density Analysis                                                | 56  |

| 4.4.2 Problem Formulation                                             | 58  |

| 4.5 Summary                                                           | 64  |

| CHAPTER 5 DENSITY-UNIFORMITY OPTIMIZATION AND CONTROL ALGORITHM       |     |

| 5.1 Introduction                                                      | 65  |

| 5.2 Interconnect Widening Process                                     | 66  |

| 5.2.1 Smart Splitting                                                 |     |

| 5.3 Area Shift Process                                                | 74  |

| 5.4 Parasitic Capacitance Control during Layout Retargeting           | 78  |

| 5.5 Summary                                                           |     |

| CHAPTER 6 EXPERIMENTAL RESULTS                                        |     |

| 6.1 Introduction                                                      |     |

| 6.2 Verification of Capacitance Modeling                              |     |

| 6.2.1 Substrate Capacitance                                           |     |

| 6.2.2 Coupling Capacitance                                            |     |

| 6.2.3 Lateral Capacitance                                             |     |

| 6.2.4 Analysis of Computation Time                                    |     |

| 6.2.5 Case Study                                                      |     |

| 6.2.6 Extension to More Advanced Technologies                         |     |

| 6.3 Experimental Result of Density-Uniformity-Aware Analog L          |     |

| Retargeting                                                           | •   |

| 6.3.1 Experimental Comparison of Various Density Control Schemes      | 108 |

| 6.3.2 Density-Uniformity-Aware Analog Layout Retargeting Verification | 111 |

| 6.4 Summary                                | 128 |

|--------------------------------------------|-----|

| CHAPTER 7 CONCLUSIONS AND RECOMMENDATIONS. | 129 |

| 7.1 Summary                                | 129 |

| 7.2 Research Contributions                 | 130 |

| 7.3 Recommendations for Future Research    | 133 |

| REFERENCES                                 | 134 |

| APPENDIX                                   | 142 |

| Candidate's Publication List               | 142 |

# LIST OF FIGURES

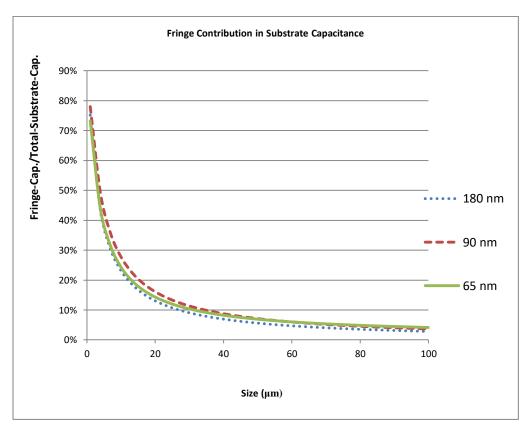

| Figure 1 – Fringe capacitance contribution with different sizes in 3 different technologies.                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

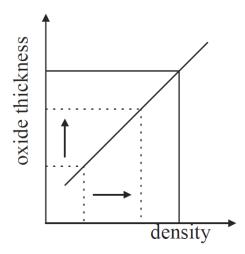

| Figure 2 – Relationship between layer thickness and local density [48]20                                                                                                                                                                                                                                                                                      |

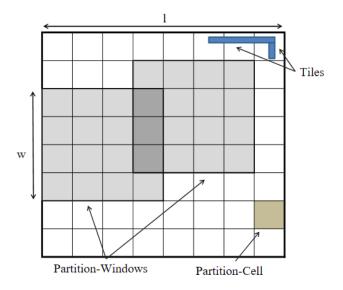

| Figure 3 – An $l \times l$ layout is partitioned into smaller cells, each of which has a size of $(w/r) \times (w/r)$ . Each $w \times w$ partition-window (light gray) consists of $r \times r$ partition-cells. A pair of partition-windows from different dissections may overlap with each other21                                                        |

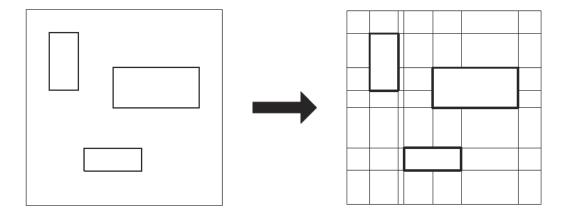

| Figure 4 – Generating Hanan grid over a layout [48]                                                                                                                                                                                                                                                                                                           |

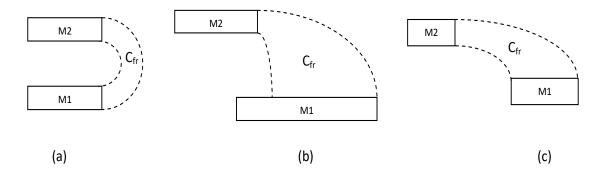

| Figure 5 – Fringe capacitances (a) sidewall to sidewall fringe in the case where two metal blocks (M1 and M2) exactly overlap, (b) sidewall to top surface fringe capacitance when two metal blocks (M1 and M2) have overlap and displacement, (c) fringe capacitance between sidewall of top metal block (M2) and top surface of bottom metal block (M1). 29 |

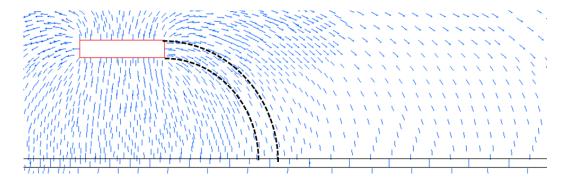

| Figure 6 – Electrostatic field simulation shows electric field between the dashed lines can be approximated by the circular lines                                                                                                                                                                                                                             |

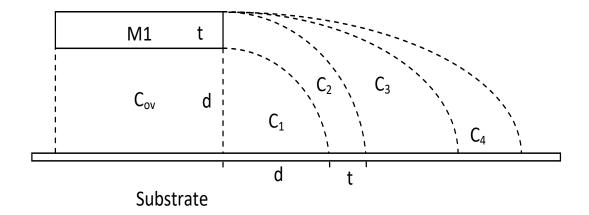

| $Figure\ 7-Splitting\ fringe\ capacitance\ of\ one\ side\ to\ several\ sub-components31$                                                                                                                                                                                                                                                                      |

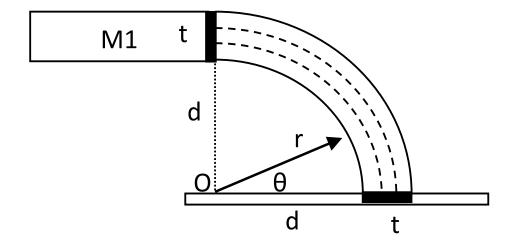

| Figure 8 – Calculating $C_2$ in a circular electric field. $t$ is the thickness of Metal-1 layer and $d$ is the vertical distance between Metal-1 layer and substrate                                                                                                                                                                                         |

| Figure 9 – Actual charge density (shown in colorful density) reduces as the distance from origin <i>O</i> increases                                                                                                                                                                                                                                           |

| Figure 10 – Choosing a proper factor to calculate the fringe capacitance based on the displacement between M1 and M2                                                                                                                                                                                                                                          |

| Figure 11 – Modeling details of fringe capacitance in Figure 5(c)39                                                                                                                                                                                                                                                                                           |

| Figure 12 – Lateral capacitance with its different components. (a) Two metal blocks are in a line. (b) Two metal blocks have displacement                                                                                                                                                                                                                     |

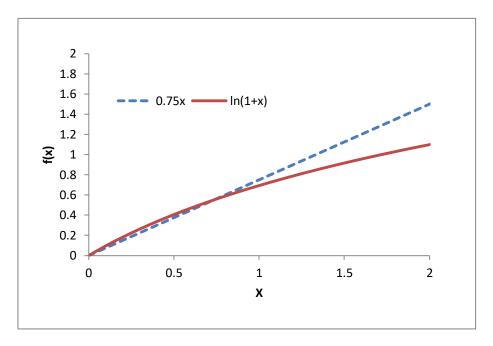

| Figure $13$ – Linearization of $ln(1+x)$ to $0.75 x$ in range of $0.65 < x < 1.2$                                                                                                                                                                                                                                                                             |

| $Figure\ 14-A\ mask\ layer\ representation\ in\ corner-stitching\ data\ structure\ [40]47$                                                                                                                                                                                                                                                                    |

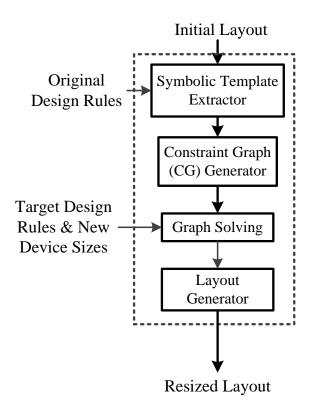

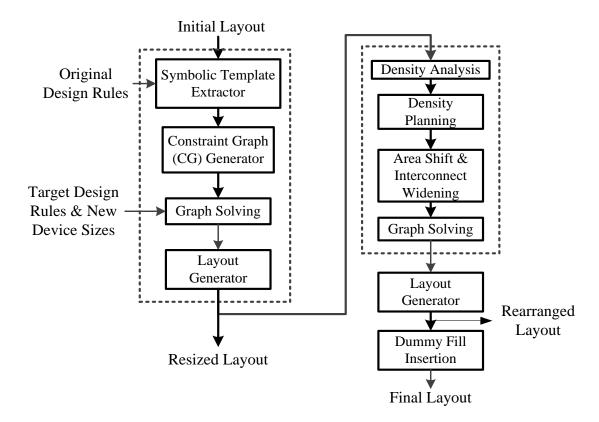

| Figure 15 – Flow diagram of the regular retargeting platform47                                                                                                                                                                                                                                                                                                |

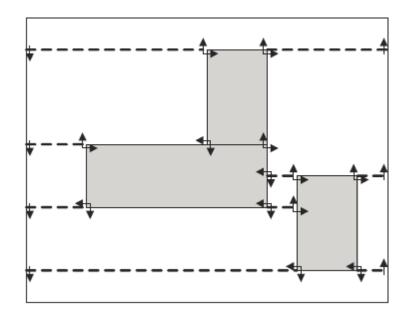

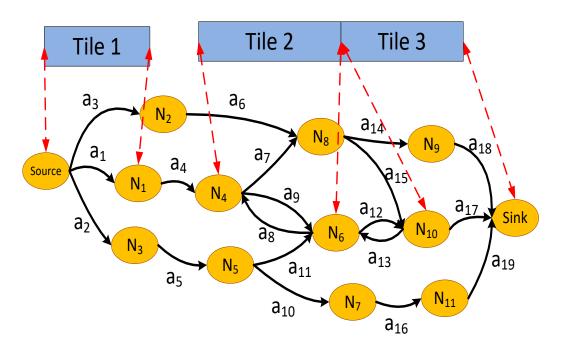

| Figure 16 – An exemplary horizontal constraint graph including a sub-graph representing the placement of three solid tiles                                                                                                                                                                                                                                    |

| Figure 17 – Flow diagram of the proposed density uniformity-aware layout retargeting methodology                                                                                                                                                                                                                                                              |

| Figure 18 – Pseudo code of the interconnect widening operation                                                                                                                                                                                                                                                                                                |

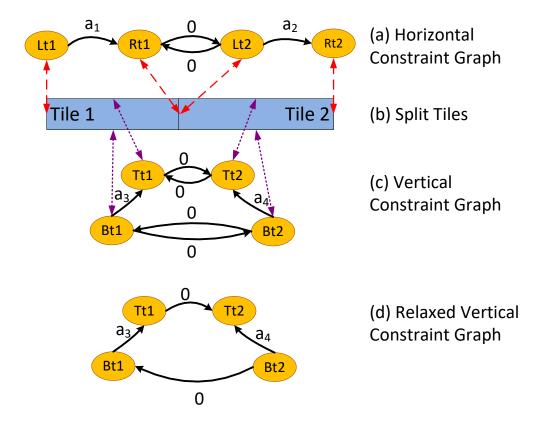

| Figure 19 – Example of splitting a tile into smaller tiles and the corresponding constraint graphs in (a) horizontal and (c) vertical directions, (c) for split tiles and (d) for the relaxed vertical constraint graph                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

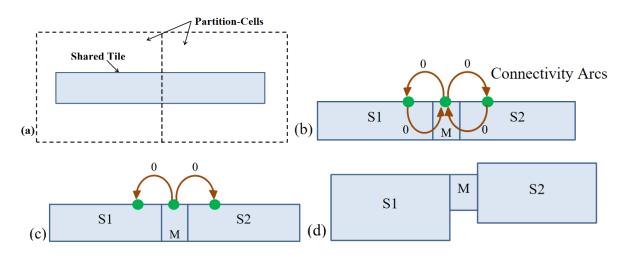

| Figure 20 – Updating connectivity constraints after splitting the shared tiles73                                                                                                                                                                                                  |

| Figure 21 – Pseudo code of the area shift operation                                                                                                                                                                                                                               |

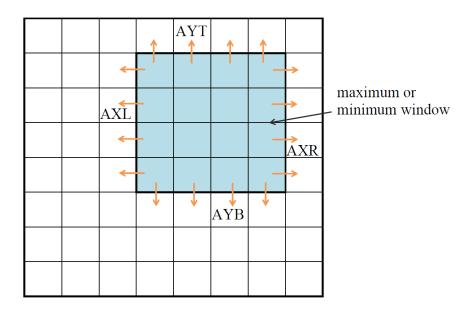

| Figure 22 – Area shift variables for the maximum or minimum partition-window in the local area shift scheme.                                                                                                                                                                      |

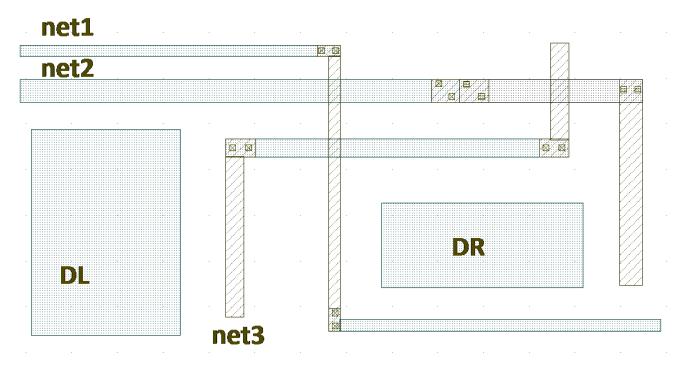

| Figure 23 – parasitic capacitance components between two adjacent nets                                                                                                                                                                                                            |

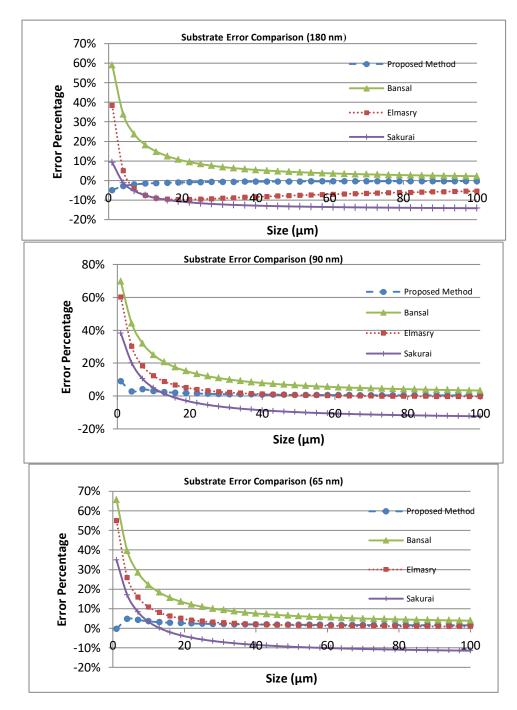

| Figure 24 – Substrate capacitance error comparison for 3 different technologies86                                                                                                                                                                                                 |

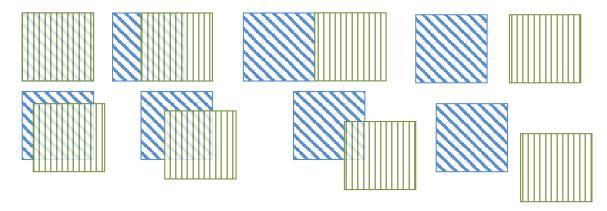

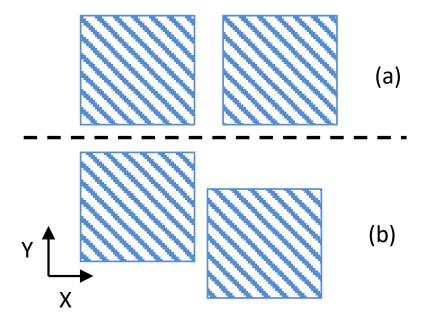

| Figure 25 – Several examples of coupling capacitance test cases (blue squares with orthogonal shadowed lines are on Metal-1 layer and green ones with vertical shadowed lines are on Metal-2 layer).                                                                              |

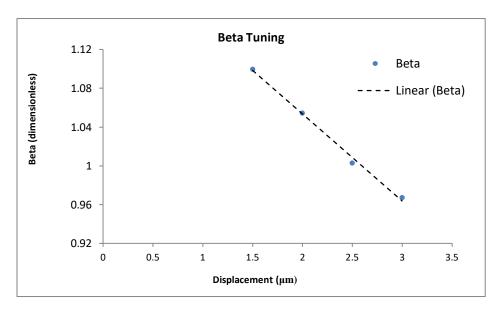

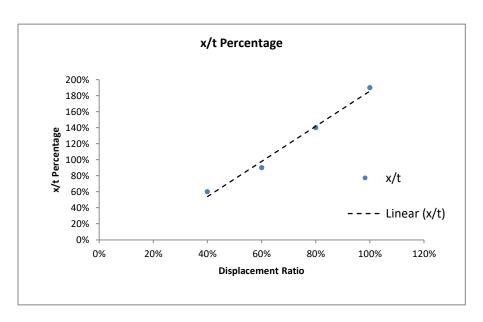

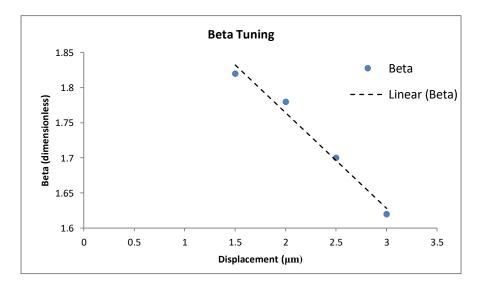

| Figure 26 – Curve-fitting diagram of four samples to tune (11) for CMOS 90 nm technology                                                                                                                                                                                          |

| Figure 27 – Curve-fitting diagram of four samples to tune (16) for CMOS 90 nm technology90                                                                                                                                                                                        |

| Figure 28 – Curve-fitting diagram of four samples to tune (11) for CMOS 65 nm technology                                                                                                                                                                                          |

| Figure 29 – Curve-fitting diagram of four samples (with geometry size of 10μm*10μm) to tune (16) for CMOS 65 nm technology92                                                                                                                                                      |

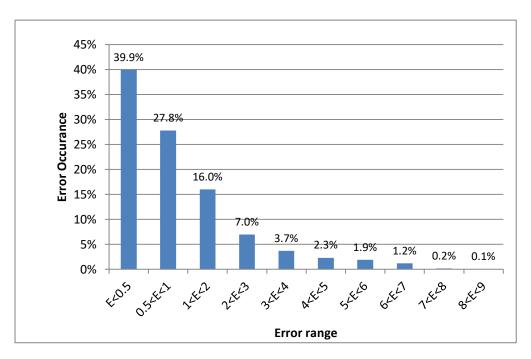

| Figure 30 – Histogram of error occurrences in the Monte-Carlo verification for coupling capacitance in the CMOS 65 nm technology                                                                                                                                                  |

| Figure 31 – Two examples of lateral capacitance test case (top view)99                                                                                                                                                                                                            |

| Figure 32 – Case study of the capacitance modeling                                                                                                                                                                                                                                |

| Figure 33 – Different test cases to investigate the effects of dummy fill insertion and interconnect widening on the laterally-coupling capacitance. (a) The reference test case, (b) dummy scheme1 test case, (c) dummy scheme 2 test case, (d) interconnect widening test case. |

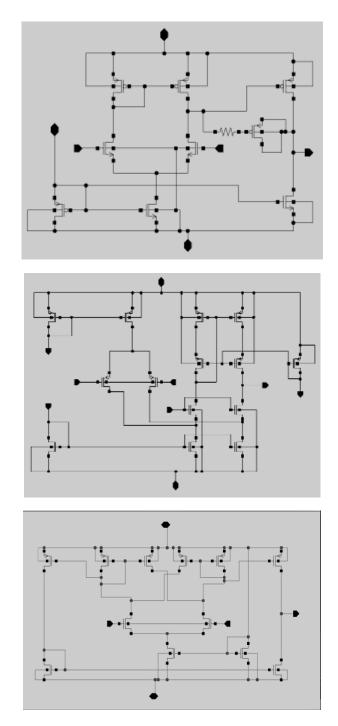

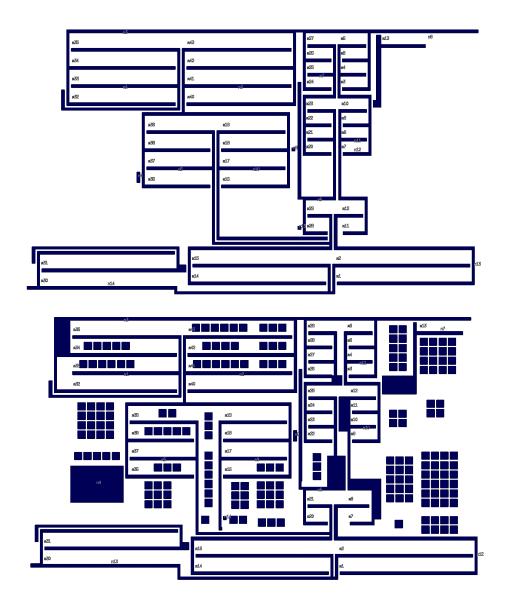

| Figure 34 – Two-stage Opamp schematic (top) and folded-cascode Opamp schematic (middle), and 5-bit ADC analog comparator (bottom)                                                                                                                                                 |

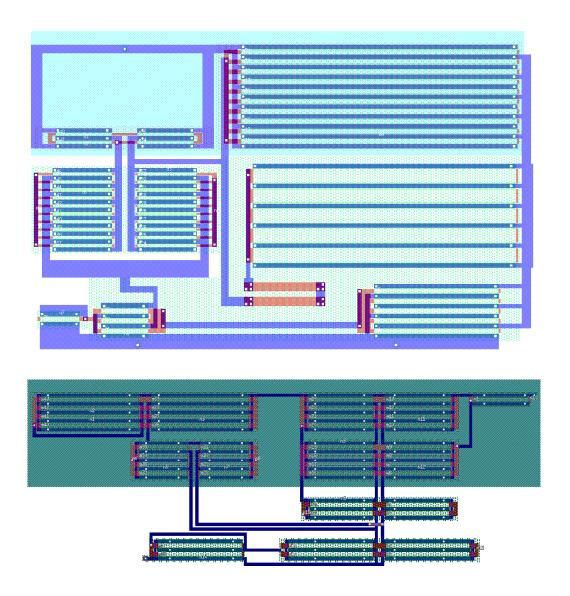

| Figure 35 – Two-stage Opamp original layout (top) and folded-cascode Opamp original layout (bottom)                                                                                                                                                                               |

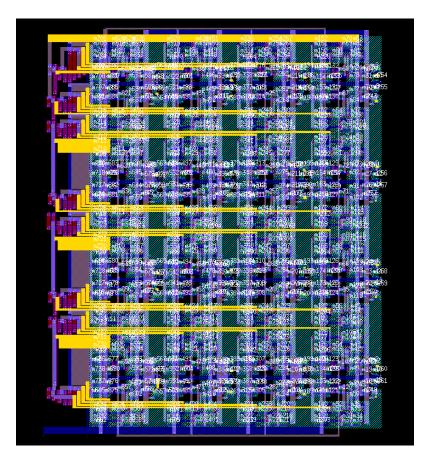

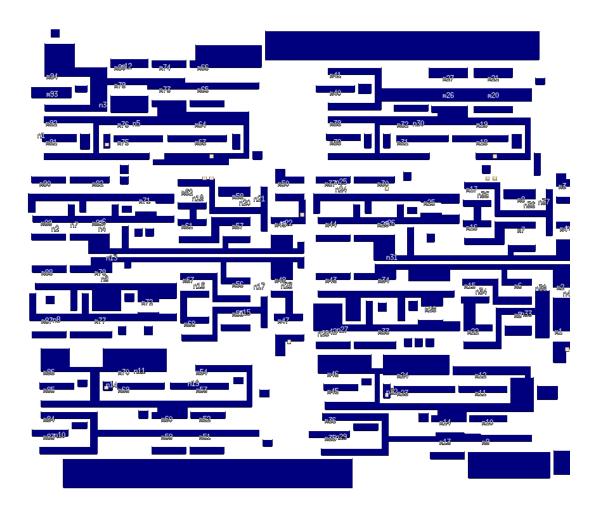

| Figure 36 – the analog part of the 5-bit ADC layout                                                                                                                                                                                                                               |

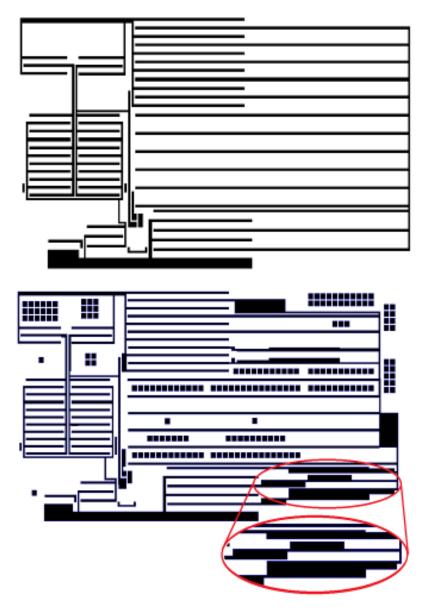

| Figure 37 – Two-stage Opamp layouts before (top) and after (bottom) the AS+IW+DF operations in CMOS 180 nm technology. The splitting and widening operation is also shown in the red ellipse.                                                                                     |

| Figure 38 - Folded-cascode Opamp layouts before (top) and after (bottom         | n) the  |

|---------------------------------------------------------------------------------|---------|

| AS+IW+DF operations in CMOS 180 nm technology.                                  | 126     |

|                                                                                 |         |

| Figure 39 – A small portion of the analog part of the 5-bit ADC layout (Metal 1 | ) after |

| modification by AS+IW+DF                                                        | 127     |

# LIST OF TABLES

| Table 1 – Average of fringe contribution in substrate capacitance                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Table 2 – Proper values obtained from the curve-fitting process85                                                                                                                                       |

| Table 3 – Comparison of coupling capacitance. All numbers represent error percentage. ( <i>NA</i> means not applicable, and <i>NF</i> means not feasible)                                               |

| Table 4 – Statistical results from the Monte Carlo verification for overlapping coupling capacitance in the CMOS 65 nm technology96                                                                     |

| Table 5 – Lateral capacitance effective width $(w_e)$ expressions and corresponding error estimations (R-squared) for different technologies $(dx)$ is the displacement in the corresponding direction) |

| Table $6$ – Comparison of lateral capacitance. All numbers represent error percentage. ( $NA$ means not applicable, and $NF$ means not feasible)                                                        |

| Table 7 – Computation time comparison                                                                                                                                                                   |

| Table 8 – Complexity comparison among the methods that are able to handle fringe capacitance ( <i>d</i> stands for the distance)                                                                        |

| $Table\ 9-Comparison\ of\ substrate\ and\ coupling/lateral\ capacitance\ in\ the\ case\ study106$                                                                                                       |

| Table 10 – Laterally-Coupling Capacitance (top) and substrate capacitance (bottom) increase comparison for test cases of Figure 32 (b)-(d) in reference to the original test case of Figure 32 (a)      |

| Table 11 – Comparison of density variation of two test layouts for CMOS 180 nm technology                                                                                                               |

| Table 12 – Comparison of density variation of two test layouts for CMOS 90 nm technology                                                                                                                |

| Table 13 – Comparison of density variation of two test layouts for CMOS 65 nm technology                                                                                                                |

| Table 14 – Comparison of density variation of 5-bit ADC layouts for CMOS 180 nm technology                                                                                                              |

| Table 15 – Performance comparison of two test layouts in CMOS 180 nm technology 124                                                                                                                     |

| Table 16 – Performance comparison of 5-bit ADC                                                                                                                                                          |

# LIST OF SYMBOLS AND ABBREVIATIONS

ADC Analog to Digital Convertor

ALG Analog Layout Generator

AS Area Shift

BEM Boundary Element Method

CAD Computer-Aided Design

CBCM Charge-Based Capacitance Measurement

CDT Constrained Delaunay Triangulation

CG Constraint Graph

CLP Covering Linear Programming

CMOS Complementary Metal-Oxide-Semiconductor

CMP Chemical-Mechanical Polishing

CPU Central Processing Unit

DF Dummy Fill

DFM Design for Manufacturability

EMCF Electro-Magnetic Curve Fitting

FEM Finite Element Method

GHZ Giga Hertz

GP Geometric Programming

IC Integrated Circuit

IMC Iterated Monte-Carlo

IPRAIL Intellectual Property Reuse-based Analog IC Layout

IW Interconnect Widening

LP Linear Programming

MC Monte-Carlo

MIN-FILL Minimum Fill

MIN-VAR Minimum Variation

MOSFET Metal-Oxide-Semiconductor Field Effect Transistor

NA Not Applicable

NF Not Feasible

RF Radio Frequency

TSV Through-Silicon-Via

VLSI Very Large Scale Integration

#### CHAPTER 1

# **INTRODUCTION**

## 1.1 Background

Competitive consumer electronics demands high-end technologies to better serve the daily life of human beings. Fast growing integrated circuits play a significant role in making various modern technologies (such as communications and multimedia) both powerful and immersive, as demonstrated by the widely affordable mobile devices in use by the general public. Unprecedented innovation in microelectronics chip manufacturing technologies calls for redesigning of the entire chip, which was functional in the outdated technologies, for newly emerging more advanced technologies. As the chip redesigning is a time-consuming process, computer-aided design (CAD) tools are introduced to help designers to complete this procedure more effectively and efficiently [1].

There is a lot of work done on the CAD tools to support the redesigning of digital circuits. Nowadays, it is already possible to use hardware description languages and scalable technology libraries to automate the entire process of designing a complex digital system/circuit for any specific technology and/or migrating to a different technology. But in stark contrast, the situation for analog and radio-frequency (RF) integrated circuits is completely different due to the high sensitivity and nonlinearity nature of analog signals and devices. The CAD tools to retarget an existing analog design to a newer technology process or specification are under research and development.

Although some methods and corresponding CAD tools have been proposed in the literature, they are far from maturity as their digital counterpart.

Chemical Mechanical Polishing (CMP) is a manufacturing process, which uses both chemical and mechanical means to make the surface of wafer planar [2]. As a normal practice in the very-large-scale-integrated (VLSI) chip fabrication, CMP has been widely utilized to satisfy the local and global planarity requirements imposed by the advanced photolithography methods [3]. To reliably fabricate multi-layer VLSI chips with high yield, the deposition density of each layer occupied by any geometric blocks should be maintained uniform in order for the CMP process to work better [4]. Therefore, foundries usually modify the layout on the wafer at the back end by inserting dummy features, which do not have any logic functionality but only change the layer density. Obviously, the signal and functional integrity of the circuits (especially sensitive analog and RF blocks) originally well done by the designers might not be guaranteed during the fabrication.

Depending on the local density of the wafer, CMP may cause unwanted effects such as erosion and dishing. This can cause variation in thickness of interlayer dielectric, which may change interconnect properties (e.g., capacitance and resistance) and lead to timing uncertainty as well as other phenomena. To improve layer property and enhance reliability in the IC manufacturing process, the global material deposition within a layout must be uniformly distributed [5]. One solution is to use dummy fill insertion to improve pattern density [6]. Dummy fill blocks are non-functional features inserted into sparse

area of a layout to increase local density in that region. However, they may increase parasitic capacitance between interconnects and thus affect circuit performance [7].

#### 1.2 Statement of Problems

# 1) Simple yet accurate model of parasitic capacitance

Based on the introduction above, accurate modeling of parasitic capacitance in VLSI chips is critical if one needs to understand and control the dummy fill insertion. Accurate modeling usually comes along with complex formulation and expensive computational process. Therefore, the demand for simple and accurate modeling is quite obvious. Researchers always have to make a trade-off between accuracy and simplicity for an analytic model based on the applications. For the optimization algorithms, a model to be utilized is preferred to be simpler yet accurate.

#### 2) Design for manufacturability of analog layouts

Integration of manufacturability considerations into the design stage of chip layouts will increase the final product quality and yield. In the traditional process of designing circuits and their layouts, design for manufacturability may not be considered seriously. Therefore, manufacturability issues have to be addressed by the foundries in the fabrication stage. This may unfortunately alter and degrade circuit performance.

# 3) Improving analog layout retargeting process

Layout generation or layout retargeting may be performed automatically by computer-aided design tools. A vast number of commercial tools have been introduced

for synthesizing digital layouts, whereas very limited promising tools are available for the analog counterparts. The area of automatic analog layout generation and optimization is still under development.

To the best of our knowledge, none of the current commercial automated analog layout retargeting tools can deal with the density uniformity challenges with a dedicated method that is tailored for analog layouts. Instead they have to solely rely on the solutions developed for general digital layouts. It has been well recognized that analog layouts, which look much sparser, are largely different from digital ones due to complex analog constraints. Moreover, the capability of density uniformity is especially beneficial to the analog layout retargeting tools, which typically convert layouts from old technologies to advanced ones. In the old technologies, density rules are normally not critical or even not required, whereas they become mandatory for the advanced technologies. Therefore, the analog layout retargeting tools demand the functionality of density uniformity as one prerequisite for them to be accepted by the analog designers in the era of advanced technologies.

#### 1.3 Research Objectives

Although the sole solution for digital layouts by means of dummy fill insertion has been already studied in the previous publications, density uniformity optimization has not yet been seriously addressed in the automated analog layout generation context. The main objective in this thesis work is to investigate a new layout retargeting methodology to generate a layout with uniform density distribution. The proposed layout retargeting

methodology can automatically produce an output layout following the same geometric floorplan of the input layout. To facilitate complex iterative loops in the optimization, a simple yet accurate model to include the parasitic capacitance into constraints is needed.

Towards these objectives, this PhD research has been conducted to gain the following achievements. A parasitic capacitance modeling methodology for a multi-layer VLSI chip has been developed. Then a linear-programming formulation and optimization method has been devised to globally schedule the resource allocation for various means to meet the density uniformity goals. Finally, several special functional features including layout density control, geometry modification, and dummy fill insertion have been integrated to form the proposed density-uniformity-aware analog layout retargeting flow. Our experiments show that all the features above are properly combined together to effectively contribute to optimum output layouts in compliance with density uniformity without compromising electrical performance.

#### 1.4 Structure of the Thesis

This thesis is organized as follows. In Chapter 2, a comprehensive literature review, including capacitance modeling, density analysis, automated layout generation, and layout retargeting, is conducted. In Chapter 3, the proposed modeling of parasitic capacitance inside VLSI chips is discussed. Chapter 4 describes the second phase of this PhD research, that is, the control and optimization scheme of the proposed density-uniformity-aware analog layout retargeting process. The implementation details of the proposed methodology are explained in Chapter 5. Chapter 6 is dedicated to the

experimental results and verification of the proposed methodology. Chapter 7 concludes this study with some contributions listed and provides some recommendations for future research.

## **CHAPTER 2**

# LITERATURE REVIEW

#### 2.1 Introduction

In this chapter, the previous work on the major aspects of this dissertation research will be reviewed. Parasitic capacitance modeling approaches are surveyed in Section 2.2. Then the work on automatic layout synthesis is reviewed in Section 2.3. In Section 2.4, the previous work on layout density analysis and dummy fill synthesis is studied. Finally, a brief summary is presented in Section 2.5.

# 2.2 Capacitance Modeling

To ensure sufficient reliability margin, it is indispensable to effectively evaluate performance of laid-out circuitry before chip fabrication. Interconnect parasitic capacitance is one of the major contributors to performance degradation and signal integrity problems [8] [9]. As state-of-the-art technologies have multiple metal layers, calculation of parasitic capacitance between these layers is challenging due to the required accuracy and highly intensive computation effort. Unlike commercial tools that typically use empirical equations specialized for a particular technology, a general reliable modeling methodology for deriving simply expressed yet accurate reusable equations is strongly demanded [10].

Parasitic capacitances can make severe impact on circuit performance if they are not correctly modeled and taken into account in the circuitry design. They may lead to performance degradation due to the issues of signal integrity and crosstalk noise. In particular, capacitance modeling in the context of complex geometry of leading-edge technologies is even more difficult [11]. Without simply expressed analytic models, extraction of a complicated layout with thousands even millions of interconnects would be extremely time-consuming and thus impractical for circuitry optimization purpose [12]. Fringe capacitance, which is normally formed by sidewalls of interconnect blocks, has an increasingly important contribution in the total parasitic capacitance in advanced technologies. Due to small absolute values of fringe capacitances, they used to be safely ignored for the old technologies. However, for the modern deep-submicron or nanometer technologies, smaller geometries, which usually generate smaller total parasitic capacitance, are widely used. Thus, the impact of fringe capacitance cannot be overlooked any longer. Moreover, according to our experiments, the contribution of the fringe component within overall capacitance increases if the size of the related geometry is shrinking (as shown in Figure 1). For example, in CMOS 90 nm technology, the fringe contribution within the entire substrate capacitance increases from 9% for 40 µm-size geometry to 28% for 10 µm-size one and even more for smaller sizes. Therefore, accurate

\_

<sup>&</sup>lt;sup>1</sup> Substrate capacitance is a capacitance formed between any geometry pattern on one layer and the substrate ground plane inside the chip.

modeling of the fringe capacitance is becoming more important in the advanced technologies.

Figure 1 – Fringe capacitance contribution with different sizes in 3 different technologies.

Adding dummy fill is one of the Design-for-Manufacturability (DFM) attempts to meet density requirements for high-yield chip fabrication [3]. Although inserting dummy fill can help make uniform layers, this practice may degrade the performance of sensitive analog circuitry or high-speed digital blocks due to added parasitic capacitance. Therefore, accurate modeling of dummy fill impact on the parasitic capacitance is crucial [13] [14]. For this reason, this dissertation research has been first focused on the modeling study of parasitic capacitance in the advanced technologies.

Computer-Aided Design tools using optimization loops can optimally add dummy fill to a chip layout while minimizing negative impact of dummy blocks on circuit performance. However, adding thousands or millions of dummy fill to a well-designed layout makes it difficult for CAD tools to invoke accurate commercial capacitance extractors to estimate a huge number of capacitors and associated performance degradation within loops of optimization. Instead, traditional rough capacitance estimation equations have to be widely used in the state-of-the-art optimization work [3] [15]. This is just a vivid example that exhibits the necessity of this research. Here the motivation is to investigate simple yet accurate analytic parasitic capacitance models, which can be used in the CAD algorithms for loops of optimization.

The reported techniques for capacitance modeling can be classified into three categories: numerical methods, analytic methods, and test-based or empirical methods. Finite Element Method (FEM), Boundary Element Method (BEM), and multipole algorithms [16] are some of the available numerical methods. These methods solve electromagnetic equations and usually provide accurate results. However, they are typically computationally expensive when applied in the modern VLSI circuits [17] [18]. Thus, they are normally deployed for the verification purpose before tape-out rather than being used as an estimator within loops of optimization.

As an alternative, analytic methods use approximate equations derived from electromagnetic or mathematical models. Since the computation of overlap capacitance is easy to handle, [11] [19] focus on different analytic models, which are used to account for fringe capacitance between interconnects by using conformal mapping. These

methods try to model electric flux between plates by mapping an elliptical shape to a rectangle. Due to intensive mathematical computation, the developed models are not recommended for extracting the layout with a great number of interconnects although accuracy of the models is acceptable.

Bueno-Barrachina et al. [20] presented electrostatic field equations to calculate capacitance between inclined plates. FEM software like ANSYS was used to solve electrostatic equations and plot them to validate their assumption. The authors verified their equations with the geometries much larger than the feature size of modern submicron or nanometer VLSI circuits. Although their model was specialized for a certain case (i.e., metal blocks with the same size), our experiments show that such a model can still be used for smaller feature size with reasonably good accuracy. Samudra and Lee evaluated special interconnect geometry in their research [21]. As their analytic equations were derived for a specific shape of interconnects (trapezoid), such equations cannot be generalized to cover other interconnect shapes. Zhao et al. [22] proposed analytic modeling of interconnect capacitance based on electric filed distribution. They used several empirical factors in their model. Although the reported accuracy was promising, the authors did not report their model computation time. Moreover, in the analytic approaches above, the proposed equations require use of some technologydependent factors, which are normally derived from experiments. However, the way how to obtain those factors is not clarified in the publications. This makes reproduction of the published methods, in particular for the modern technologies, extremely hard.

The third category is the empirical technique [23], where plenty of experimental data for a particular technology are collected and fitted to a certain model. In these methods some technology-dependent parameters have to be obtained for the best match. These methods are widely used in commercial tools where the capacitance extraction equations are different for special situations appearing in the layout. Using computationally intensive operators (e.g., exponentiation or logarithm) and many equations for one general scenario is deemed as the drawbacks of the empirical technique.

Barke [24] compared previous work on the estimation of line-to-ground capacitance, which are analytic equations combined with several empirical factors. Since this study was targeted at an old technology (where the author verified the equations with geometry sizes around 1 µm), several proposed equations function well for large geometries in the modern submicron technologies. However, these equations often fail to work well for smaller geometries. Tani *et al.* [18] also proposed approximation equations for parasitic capacitance extraction with promising results for some particular cases (e.g., two crossing metal lines). Their analytic method also includes several empirical factors that are hard to determine for new technologies. Moreover, estimation of coupling<sup>2</sup> capacitance for adjacent interconnects was postponed as their future work.

\_

<sup>&</sup>lt;sup>2</sup> Coupling capacitance is a capacitance formed between two parallel patterns belonging to different electrical nets inside a VLSI chip.

After comparing three numerical methods (FEM, BEM, and random walk method [25]) and analytic methods, Husain [26] suggested some guidelines to extract interconnect capacitances of a large layout. Several methods were also compared with each other along with the error sources analyzed for each of them. In conclusion, the author stressed that the numerical-method-based field solvers are too slow in extraction of parasitic capacitances for large layouts. Moreover, it was suggested that the existing analytic methods need to be modified for being used in the new technologies. In the work by Chang *et al.* [27], a Charge-Based Capacitance Measurement (CBCM) method was introduced to measure total capacitance of one interconnect. Using a test structure and a test signal, the authors could measure the capacitance of a pin. This is a general method, but out of our interest in this dissertation research.

Accurate modeling of parasitic capacitance has vast applications in VLSI industries. Hyun *et al.* [28] used a model similar to the one proposed in [11] for Through-Silicon-Via (TSV) coupling capacitance. The average reported error is around 5-8%. The sidewall parasitic capacitance in nano-scale trench isolated MOSFETs [29] and gate capacitance in gate-all-around cylindrical silicon nanowire MOSFETs [30] were also modeled by using a conformal mapping method, which is similar to [11] and [23]. Furthermore, capacitance modeling is important in Chemical Mechanical Polishing and density analysis. Kahng and Samadi [3] reported the significance of accurate parasitic capacitance estimation in dummy fill insertion stage where imprecise filling process without considering effect of parasitic capacitance from the layout can dramatically degrade circuit performance.

#### 2.3 Layout Synthesis and Retargeting

Automated analog layout generation has always been one of the appealing topics in the area of electronic design automation. Such efforts can be categorized into two different streams. In the first division, an analog layout can be generated from scratch by using sequential operations of device generation, placement and routing. The associated methods have been studied so well that a variety of academic and commercial tools are currently available for decent layout generation directly from analog schematic. However, different from the mature digital hardware description language and physical design flow, these methods are still unable to convert a well-designed layout to fit for updated specifications or new technologies. Therefore, the second research stream in this disseration, called layout retargeting, has been called upon to address this issue in the context of restless technology upgrade. Normally, a modern analog layout retargeting method uses a silicon-proven input layout as template to produce an optimal solution suitable for modified specifications or updated technologies with simultaneous placement and routing operations.

LAYLA [31] is a hardware description language to develop parameterized cell libraries for VLSI layouts mostly focused on digital circuits. Hong *et al.* [32] introduced a performance-driven analog layout compiler. Their proposed compiler includes device generation, placement, and routing with performance considerations in order to meet the design specifications. KOAN/ANAGRAM II [33] is a tool based on macrocell layout automation to produce a complete analog layout from scratch. It includes two main modules: KOAN is responsible for device generation and placement, and ANAGRAM II

handles interconnections among the devices. The analog layout synthesis is broken down into sequential steps. To improve this work, the authors pointed out that a good understanding and communication between placement and routing is necessary. Malavasi *et al.* [34] presented a methodology for automatic synthesis of a full custom IC layout with complex analog constraints. By using this approach, high-level specifications can be translated into low-level constraints, which can control the supporting tools for placement, routing and compaction. Although parasitic constraints are taken into account in the layout generation, the projected parasitic bounds may create an over-constrained problem, which renders the problem unsolvable.

Zhang et al. [35] proposed a layout synthesis flow for RF circuits to consider parasitic closure issues. Their method utilizes performance-driven placement and global routing along with device tuning. Since layout effects related to performance are only modeled in terms of net length, parasitic coupling intricacy in the advanced technologies may not be considered by this method. In [36] a layout synthesis method, ALADIN, was proposed with sequential steps of module generation, placement and routing. The third version of the Analog Layout Generator (ALG) [37] was improved by Yilmaz and Dundar. Similarly this tool is capable of module generation, placement and routing. It offers optimization-based and rule-based module generation. The generated modules are fed to a placer to finalize the module locations in the layout. Finally in the routing stage, all of the modules are electrically connected globally and locally. During these sequential steps, this tool utilizes optimization algorithms to minimize performance degradation caused by parasitic effects and process variation.

An important factor for layout automation is how to use expert design knowledge in the physical design. In the following layout retargeting works, the expert design knowledge is normally reflected from the old layout or input template. Castro-López *et al.* [38] presented their work of analog layout retargeting by creating an extensive hierarchical template from an input layout. By generating constraints from input layout and applying new design specifications plus objectives, an iterative simulation-based optimization algorithm can generate a resized layout. In contrast, the authors used slicing tree to represent a layout in the layout synthesis process [39]. Since both methods require a lot of simulation and computation effort in the iterations to reach final solutions, the efficiency of these algorithms needs to be improved.

Jangkrajarng *et al.* introduced a layout retargeting tool called Intellectual Property Reuse-based Analog IC Layout (IPRAIL), which uses a symbolic template to preserve input layout properties and eventually generate a layout that meets all new design rules and specifications [40]. The symbolic template introduced in their work is directed constraint graphs, which are optimized in the context of new design constraints to generate a retargeted layout fit for new technology processes and/or specifications. In [41], Zhang and Liu improved the retargeting process by considering performance bounds when handling the symbolic template. Circuit performance sensitivities are first identified and modeled, and then the corresponding parasitic bounds are added to the pool of constraints. Finally the optimization problem is resolved by using combination of a graph-based technique with mixed-integer non-linear programming. Although the basic design rules and parasitic effects have been well covered, some design-for-

manufacturability tactics emerging in the advanced technologies cannot be handled by these methods.

Wang et al. [42] used layout symbolic template and Geometric Programming (GP) in the process of layout regatgeting. The presented experiment shows some promising results compared to the previous works. Chin et al. [43] presents an analog layout prototyping method by reusing layout knowledge while preserving routing behavior. The layout routing information is extracted into a graph with Constrained Delaunay Triangulation (CDT) algorithm. Multiple placements of the modules are explored, while for each placement candidate, the graph containing routing information is updated and resolved to derive the interconnected layout. For any left-over unrouted nets, manual routing is needed at the end of the process. Finally, the layout is tuned on the basis of simulation results with certain aid of users. Although this method can reduce layout prototyping time, it is hard to be fully automated and the final result heavily relies on expert knowledge.

LAYGEN II [44] proposed by Martins *et al.* is a tool for automated analog IC layout generation based on input template and optimization techniques. As an input, the layout template information, which is used for guiding placement and routing, is converted to a B\*-tree representation by a placer. Once the layout floorplan is identified, an optimization-based router completes the interconnection with an evolutionary algorithm as the optimization engine. Although effective, the applied optimization method may cause degradation in the computational efficiency for the layout with a large number of blocks. Furthermore, an automated analog IC design flow from circuit level

specifications to physical layout description is included in AIDA [45]. The fully automated circuit-level synthesis is done by a multi-objective multi-constraint optimization approach. Then a layout is generated considering design rule constraints from a sized circuit-level description and high level layout guidelines. In this work, LAYGEN II is used to generate and optimize the final layout.

Weng *et al.* in [46] proposed an analog layout migration methodology to effeciently generate multiple layouts while keeping similar or better circuit performance. Various placement constraints are extracted from the original layout and hierarchically stored into a topology slicing tree. Pan *et al.* [47] proposed a prototyping framework for analog layout migration with planar preservation. In their work, constrained Delaunay triangulation is used to extract placement and routing features from an input layout into a crossing graph, which can be migrated into multiple layouts with placement and routing reconnection.

#### 2.4 Density Analysis and Fill Synthesis

All of the analog layout automation tools above strive to meet design specifications and technology design rules. To fabricate a chip in deep sub-micron or nanometer technologies, a layout should normally meet certain density design rules. As shown in Figure 2, layer thickness and local density has a tight relationship [48]. Variation in layer thickness may cause some unwanted degradation in chip performance. To control layer thickness, foundries try to control the local density by imposing density design rules.

If these rules are not met, foundries would usually have to modify the layout by inserting non-functional dummy blocks to achieve the desired density coverage for increasing the chip yield. Typically, density analysis comes with area fill synthesis as a part of CMP process. The goal of density analysis is to find the windows that violate density constraints (upper bound or lower bound). When the density analysis is combined with fill synthesis, the optimal number of demanded dummy blocks is calculated by using an optimization approach. Following such a recommendation, some dummy blocks are inserted into the layout to achieve better pattern density distribution in terms of uniformity.

Foundries have enforced density rules on different layers to minimize the effect of CMP variation, which can consequently control variation of the layer thickness. For example, in 0.35 µm and below technologies, foundries require overall density of any metal layer to be maintained between 35% and 70%. These density design rules are defined based on a specific technology and/or context (such as application specific integrated circuit (ASIC), digital or analog layouts) [48].

Figure 2 – Relationship between layer thickness and local density [48].

Kahng *et al.* [48] investigated three major approaches of analyzing layout density, including fixed dissection method, optimal extremal-density window analysis, and multilevel density analysis. All of these methods are based on scanning layout with different windows to find maximum and minimum window densities. The density of all  $w \times w$  windows in the layout is checked to verify density uniformity distribution in the layout. The size of window (w) is a factor of a few parameters (e.g., process technology, CMP process, etc). Checking all eligible  $w \times w$  windows in the layout to find extremal windows is a time consuming procedure. Therefore, foundries normally utilize some simpler methods to analyze the density of a layout.

One of such simpler methods is called fixed dissection density analysis method, which is nowadays quite popular and often used by foundries. In the fixed dissection regime as shown in Figure 3, a layout is partitioned to smaller partition-cells, and the density of all the windows are calculated over the layout to find the extremal windows.

As another method, all of the window corners are always on the Hanan grid [49], which is formed when drawing vertical and horizontal lines passing through all the tile edges as shown in Figure 4. The author also proposed a multi-level density analysis approach, which recursively subdivides the layout until the number of tiles in each cell is small for improving accuracy while its running time is still fast. Although the presented algorithms appear to be accurate, the experimental results show they are very slow when the number of tiles is large.

Figure 3 – An  $l \times l$  layout is partitioned into smaller cells, each of which has a size of  $(w/r) \times (w/r)$ . Each  $w \times w$  partition-window (light gray) consists of  $r \times r$  partition-cells. A pair of partition-windows from different dissections may overlap with each other.

Figure 4 – Generating Hanan grid over a layout [48]

Besides that, the authors of [48] also studied the filling problem by using linear programming (LP) to minimize the density variation of windows (i.e., the maximum window density minus the minimum window density). This formulation is called MIN-VAR, which can suggest the amount of needed dummy fill to be inserted in different regions of the layout. This work is one of the earliest endeavors in the area of dummy fill insertion optimization. Although its optimization coverage and uniformity performance are relatively limited compared to the consequent works, its versatility of the LP formulation has profound impact on the further research of dummy fill synthesis.

In another work, Xiang *et al.* [50] presented a methodology based on the fixed dissection method. The main idea of their research is to recursively use fixed dissection approach with smaller cell size. To efficiently reduce run-time of the algorithm, the authors used a specific structure for mapping the tiles in the layout and avoided double

counting in their equations. This method was claimed to be faster than the previous methods yet accurate.

Chen *et al.* [51] presented Monte-Carlo-based filling methods with similar runtime compared to the previous LP-based methods. In their Monte-Carlo approaches, each partition cell is assigned with a certain priority, which is calculated as a function of multiple parameters, such as density upper bound, available filling area, *etc.* Then one partition cell is chosen based on its priority and filled with the predetermined amount of dummy fill. Although the reported accuracy looks somewhat promising, the drawback of this method is that an excessive amount of dummy fill may be inserted into the layout. The same authors improved their work in [52] by presenting iterative methods based on linear programming, Monte-Carlo and greedy algorithms. To reach optimum solutions, they alternated between two main formulations, minimum window density variation (i.e., MIN-VAR) and minimum amount of inserted dummy fill (called MIN-FILL). The experimental results show that the new methods can derive better solutions at the cost of slightly longer running time over the non-iterated methods.

Another fill synthesis method was proposed to consider the impact of fill insertion on the circuit performance in [53]. The authors first developed a method of estimating the effects of dummy fill on parasitic capacitance and timing overhead in the digital layout design. Then the problem was formulated to minimize the total delay based on integer linear programming and greedy algorithm. In comparison with the other works, this scheme showed a reduction in the total delay of digital circuits. However, since the accuracy and scope of the applied capacitance modelling were not clearly reported in this

work, it is uncertain whether the same modeling scheme can be applied to the advanced technologies. Tian *et al.* [54] also presented a modeling method for density analysis of a layout considering all dies on a wafer. Their formulation of fill placement is similar to MIN-VAR, but with an addition of variation budget. Although the reported results were promising, this paper failed to provide some comparison results with other approaches.

Mukherjee and Chakraborty in [55] presented a random greedy algorithm to insert pixel-wise dummy fill. In their density analysis method, they tried to use floating window to improve density uniformity. However, lack of the details in their implementation makes it unclear for the readers to understand how dummy insertion was performed. Despite the promising test results that showed the efficacy of their proposed method, they actually compared the experimental results with only one distinct method, which was literally aimed at different functionalities. Feng *et al.* [56] developed a polynomial-time approximation algorithm for covering LP (CLP) problem of dummy fill insertion, based on which they presented a greedy iterative algorithm to achieve better performance. While the run time of the proposed algorithm was shrunk significantly, the number of the inserted dummy blocks could be reduced only up to 3%. Moreover, the experimental results of the proposed greedy algorithm were only compared with a Monte-Carlo-based algorithm.

A novel density analysis method with the objective of minimizing gradient density was proposed in [57]. The density analysis was done with window coarsening and uncoarsening to minimize gradient density until the optimal number of dummy blocks was identified. In this work, coupling capacitance constraints were also considered.

However, although the proposed method could significantly reduce the density gradient and the number of inserted dummy blocks, there was no report on the final density variation of the experimental layouts in the paper. Dhumane and Kundu [58] proposed a method of concentrically growing windows to check density uniformity for better dummy fill insertion. With a focus on yield improvement, they intended to balance the competing goals between surface planarity and critical area minimization. However, in spite of the growing window approach for dummy fill insertion, their problem formulation is actually quite similar to the fixed dissection method used in [48]. Saha and Sur-Kolay [59] developed a planarization method to address the limitation of the conventional square partition-windows for dummy fill synthesis. They proposed a Voronoi-diagram-based tessellation for better selection of the positions where dummy fill blocks need to be inserted.

A novel design flow for dummy fill insertion using Boolean mask operations was presented in [60]. To improve computational efficiency, the authors claimed that dummy fill insertion can be moved to mask generation steps when a design is going to be fabricated by foundries. In this process, a mask for dummy blocks is prepared, optimized, and then combined with the masks for the active patterns included in the original design. This proposed flow can significantly reduce the product delivery time. Nevertheless, the performance of the modified layouts was not discussed in the paper although it may be affected due to dummy fill insertion. In a recent work, Liu *et al.* [61] proposed three new filling approaches, which first find fillable areas in a layout and then insert dummy features in a way to minimize the total overlap. In another similar work, Lin *et al.* [62]

introduced a dummy fill insertion method for digital layout design with coupling constraints considered. By using integer linear programming and min-cost flow graph optimization, the proposed method can effectively improve the layout density variation.

# 2.5 Summary

This chapter is started with a review of the previous works on parasitic capacitance modeling on multi-layer VLSI chips. Then the existing layout generation and retargeting methods/tools are surveyed in the domain of analog and RF integrated circuits. Finally the previous works on layer density analysis and layout density uniformity optimization methods are reviewed. The above literature review would provide a better understanding of the history and the state-of-the-art on the major areas covered in this dissertation research. The next chapter will be focused on the discussion of the proposed methodology for parasitic capacitance modeling in multi-layer layouts.

# CHAPTER 3

# ANALATIC MODELING OF PARASITIC CAPACITANCE<sup>3</sup>

#### 3.1 Introduction

In this chapter, the analytic models developed for different fringe capacitance components in parasitic capacitance are explained. First a brief discussion about the preliminaries of capacitance modeling is presented. Then the proposed analytic models for substrate capacitance, coupling capacitance, and lateral capacitance are discussed. Finally, the approximated linear models and the utilized curve-fitting technique are discussed.

# 3.2 Preliminaries of Capacitance Modeling

To facilitate the modeling, as generally used in the literature, we can define two parasitic capacitive components as follows: 1) *overlap capacitance*, which is formed between two overlapping parallel conductors on different layers or the same layer; 2) *fringe capacitance*, which is formed between non-overlapping sidewall of one conductor and surface or sidewall of a second conductor on the same or different layer with reference to the first conductor.

<sup>&</sup>lt;sup>3</sup> The research of this chapter has been published in [A2], [A4], [A8] and [A10].

The capacitance of overlapping metal interconnects can be easily computed by using the following parallel plate equation,

$$C_{ov} = \varepsilon_r \varepsilon_0 \frac{A}{d} \tag{1}$$

where  $\varepsilon_r$  is the relative dielectric coefficient,  $\varepsilon_0$  is the vacuum permittivity, A is the overlap area, and d is the distance between two parallel plates. In the cases where there are multiple dielectric layers, we use weighted average of dielectric coefficients to calculate average dielectric coefficient. This is similar to the method documented in [28].

Figure 5 exhibits electric flux between two metal surfaces (i.e., block *M1* on Metal-1 layer and block *M2* on Metal-2 layer), which generates different fringe capacitive components (i.e., sidewall-sidewall and sidewall-surface). Analytic models of fringe capacitance often deploy technology or geometry dependent parameters [26]. Fringe capacitance modeling also has a close relationship with geometric parameters. In modern technologies, due to technology scaling-down and the trend of using smaller size geometries, fringe capacitance is playing an increasingly more important role in parasitic capacitance.

Figure 5 – Fringe capacitances (a) sidewall to sidewall fringe in the case where two metal blocks (M1 and M2) exactly overlap, (b) sidewall to top surface fringe capacitance when two metal blocks (M1 and M2) have overlap and displacement, (c) fringe capacitance between sidewall of top metal block (M2) and top surface of bottom metal block (M1).

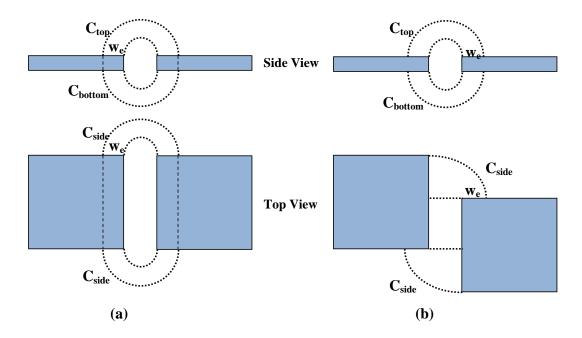

Capacitance appearing in circuits can also be categorized from another point of view: Substrate Capacitance is formed between an interconnect block and the ground plane, Coupling Capacitance is generated between two interconnect blocks on different layers, and Lateral Capacitance is produced between two interconnect blocks on the same layer [63]. These terms are widely used in the literature. In some literature, coupling and lateral capacitances are generally called coupling capacitance. Each of the substrate capacitance, coupling capacitance, and lateral capacitance may have overlap and fringe components as described above. In the following sub-sections, the details of modeling these capacitances are explained.

# 3.3 Modeling of Fringe Capacitance

Our proposed modeling approach, which is aimed to be used as a general method for any kind of technology and geometry, is based on physics concept of electric field and charge between plates. The derived analytic equations are formulated based on electrostatic field analysis and approximated to simple equations but preserving promising results. We divide the modeling into three different categories. First, we propose an equation to calculate fringe component of substrate capacitance. Then, it is extended to compute fringe component of coupling capacitance. Finally, the method is applied for computation of lateral capacitance.

#### 3.3.1 Substrate Capacitance

Substrate capacitance is a type of capacitance between an interconnect block and substrate plane (usually as ground). An interconnect block may have four fringe capacitance components, one for each side. We will first derive equations for one side, and then we will apply them to the others. In our method, the key point of accurately calculating fringe component is to split it to several major sub-components.

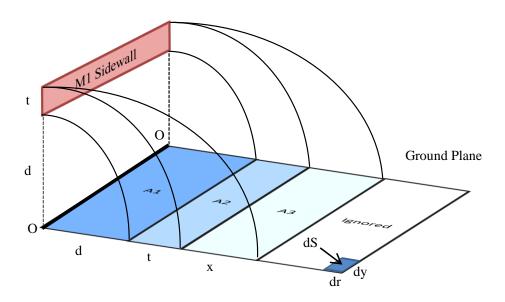

As shown in Figure 7, the fringe capacitance between one side of a metal rectangle MI and the substrate plane is made up of  $C_1$ ,  $C_2$ ,  $C_3$ , and  $C_4$ . We can calculate  $C_2$  based on electromagnetic equations by using geometric parameters such as metal thickness (t) and vertical distance (d) between the metal block and surface of the ground plane.  $C_1$  and  $C_3$  are also calculated in terms of  $C_2$  based on charge density distribution concept.  $C_4$  can actually be neglected due to very less contribution. Then the fringe capacitance for this side would be the sum of the first three sub-components as they are connected in parallel.

To calculate  $C_2$ , we assume the electric field lines are circular as shown in Figure 6 and Figure 7. Figure 6 shows the simulation of electric field which forms the capacitance between a metal block and the ground plane. Without loss of generality, we can also

assume the block is on Metal-1 layer and the substrate plane is connected to ground. Then the voltage between the metal block side wall and the ground plane can be calculated by using (2):

Figure 6 – Electrostatic field simulation shows electric field between the dashed lines can be approximated by the circular lines.

Figure 7 – Splitting fringe capacitance of one side to several sub-components.

$$V = \int_{L} \vec{E} \cdot \vec{dl} = \int_{\theta=0}^{\theta=\pi/2} E(r) \cdot r \cdot d\theta = E(r) \cdot r \cdot \frac{\pi}{2}.$$

(2)

In (2), the voltage is calculated by integrating vector multiplication between electric field vector  $\vec{E}$  and length vector  $\vec{dl}$  over arc L. As shown in Figure 8, electric field vector

can be converted to a function of radius, E(r), which is independent of angle  $\theta$ . Vector  $\vec{dl}$  is also converted to  $r \cdot d\theta$ .

The superficial charge density, which is represented by  $\sigma$  at the distance r from the origin labeled as O on the ground plate, is:

$$\sigma(r) = \varepsilon_r \varepsilon_0 \cdot E(r). \tag{3}$$

After combining (2) and (3), we can obtain

Figure 8 – Calculating  $C_2$  in a circular electric field. t is the thickness of Metal-1 layer and d is the vertical distance between Metal-1 layer and substrate.

$$\sigma(r) = \frac{2 \,\varepsilon_r \varepsilon_0}{\pi r} V. \tag{4}$$

An element of charge for unit length is defined as follows:

$$dq = \sigma(r) dS = \sigma(r) \cdot 1 \cdot dr, \tag{5}$$

where dS (shown in Figure 9) is the element of area, which is dr for unit length (i.e., dy = 1).

Now by integrating dq, the total stored charge  $Q_2$  between the M1 sidewall and the shadowed area A2 on the substrate plane surface can be represented in the form of (6)

$$Q_2 = \frac{2 \,\varepsilon_r \varepsilon_0}{\pi} V \int_d^{d+t} \frac{dr}{r} = \frac{2 \,\varepsilon_r \varepsilon_0}{\pi} V \ln(1 + \frac{t}{d}). \tag{6}$$

Figure 9 – Actual charge density (shown in colorful density) reduces as the distance from origin *O* increases.

Note that the calculated charge is not the total stored charge in the scenario above. Instead it only represents portion of the charge that is associated with capacitance  $C_2$ . Due to that, it can be named as  $Q_2$ .

The general equation for calculating capacitance (i.e., C = Q/V) can help calculate  $C_2$ , that is, for unit length:

$$C_2 = \frac{2 \,\varepsilon_r \varepsilon_0}{\pi} \ln(1 + \frac{t}{d}) \tag{7}$$

To calculate the other components, we refer to charge density of the substrate plane surface. The actual charge density decreases when the distance from origin O increases (as shown in Figure 9).

If the average charge density  $(\bar{\sigma})$  is considered for the surface, the relationship between  $C_1$  and  $C_2$  can be approximated to the following equation:

$$\frac{C_1}{C_2} = \frac{Q_1/V}{Q_2/V} = \frac{\bar{\sigma}A_1}{\bar{\sigma}A_2} = > \frac{C_1}{C_2} = \frac{A_1}{A_2},\tag{8}$$

where V is the voltage between two plates,  $Q_1$  and  $Q_2$  represent the charge of each related region, and  $A_1$  and  $A_2$  stand for the corresponding area of each segment on the substrate plate surface. Thus, we will have

$$C_1 = \frac{d}{t} C_2. \tag{9}$$

$C_3$  can be calculated in a similar way.

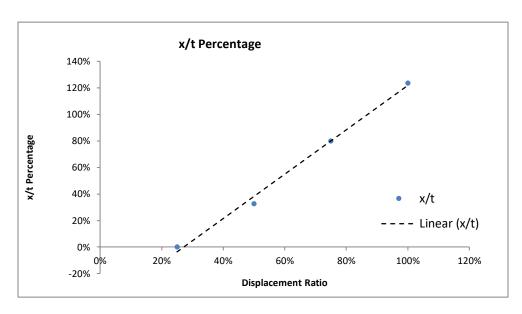

$$C_3 = \frac{x}{t} C_2. \tag{10}$$

Now the most challenging issue is how to determine a correct distance for x. As observed from Figure 9, beyond x, electric flux is not strong enough to contribute towards the fringe capacitance formation. So the curve-fitting technique is used to select the right value of x for one specific technology. Other factors such as corner capacitive effect as well as the error due to applying average charge density can be accounted for by choosing suitable technology-dependent values for x. The details of the applied curve-

fitting technique will be discussed in 3.3.5. Therefore, the fringe substrate capacitance for one side is calculated by summing up the three components above:

$$C_{fringe,sub} = C_1 + C_2 + C_3 = \left(\frac{d}{t} + 1 + \frac{x}{t}\right) C_2.$$

(11)

The fringe capacitances of the other sides can be calculated in the same way. Thus, the substrate capacitance for a square metal block can be computed by adding overlap capacitance and four side-wall fringe components as follows:

$$C_{sub} = C_{ov} + 4C_{fringe.sub}. (12)$$

# 3.3.2 Coupling Capacitance

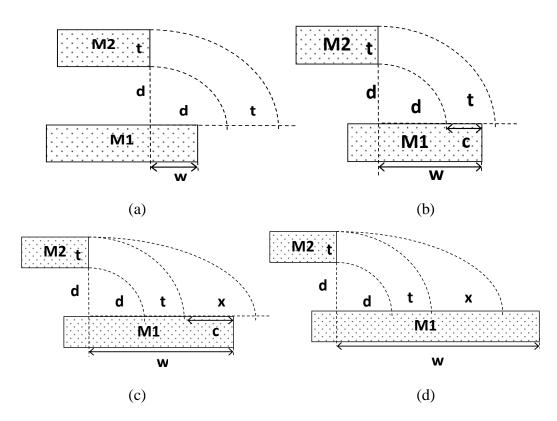

Coupling capacitance is the capacitance between two metal blocks on different layers. Figure 5 shows different examples of this capacitance. It includes one overlap component (if applicable) and several fringe components. As discussed in 3.2, the overlap component is easy to compute by using (1), whereas the computation of the fringe components is much more complicated. We can categorize the fringe capacitance into 3 different situations. In Figure 5(a), fringe capacitance is formed between two sidewalls when they are in a line. In Figure 5(b), fringe capacitance is defined between sidewall of M2 and top surface of M1. Fringe capacitance in Figure 5(c) has the same definition, but two metal blocks have no overlap. For each of the situations above we have developed an equation as explained below. Those equations will cover all of the coupling fringe capacitance situations appearing within a design.

Figure 5(a) shows a fringe capacitance when two metal blocks (say, M1 and M2) exactly overlap on one side. In this case, the fringe component can be approximated to a capacitance, which is formed by semicircular shape electric flux between two side walls. If we change the upper bound angle in (2) to  $\theta = \pi$  and continue the rest of the derivation, we can reach the following equation for the fringe capacitance in unit length:

$$C_2 = \frac{\varepsilon_r \varepsilon_0}{\pi} \ln(1 + \frac{2t}{d}). \tag{13}$$

Calculating the fringe capacitance in Figure 5(b) is similar to calculating the fringe component of substrate capacitance (11), where x can be determined by the curve-fitting technique.

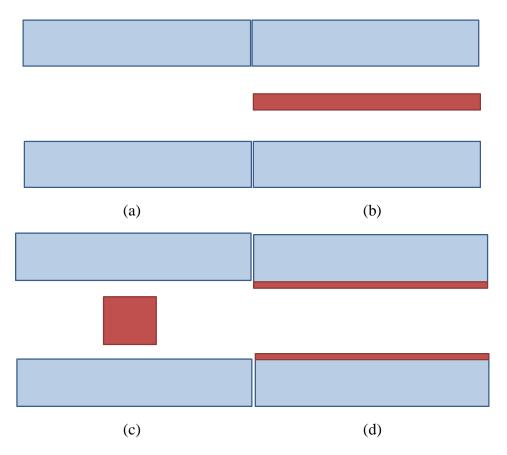

In case the displacement (w in Figure 10) amount of the top surface of the bottom metal block is less than (d + t + x), a proper value in calculating fringe capacitance should be considered. We can categorize it in the following four different cases as depicted in Figure 10(a)-(d):

- If w is less than vertical distance (d) between two metal layers as shown in Figure 10(a), only a portion of  $C_1$  in (11) is considered as the fringe capacitance. Therefore, the coefficient of  $C_2$  in the rightmost expression of (11) would be  $(\frac{w}{t})$ , that is, the unit fringe capacitance for that side would be  $C_{fringe} = (\frac{w}{t}) \times C_2$ .

- If w is between d and (d + t) (where t is the thickness of the top layer) as shown in Figure 10(b), we can consider  $C_1$  plus a portion of  $C_2$  in the formulation. In this

case, we first calculate  $C_2$  and then use the coefficient of  $C_2$  in the rightmost expression of (11) as  $(\frac{d}{t} + \frac{c}{t})$ , where c = w - d.

- If w is greater than (d + t) but less than (d + t + x) as shown in Figure 10(c), the coefficient of  $C_2$  in the rightmost expression of (11) would be  $(\frac{d}{t} + 1 + \frac{c}{t})$ , where c = w (d + t).

- If w is greater than (d + t + x) as shown in Figure 10(d), the coefficient of  $C_2$  in (11) would be  $(\frac{d}{t} + 1 + \frac{x}{t})$  as described earlier.

Figure 10 – Choosing a proper factor to calculate the fringe capacitance based on the displacement between *M1* and *M2*.

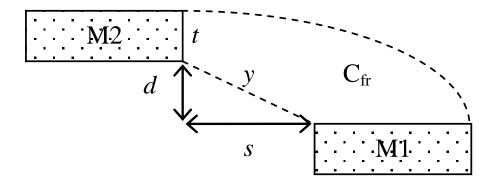

If two metal blocks have no overlap as displayed in Figure 5(c) and Figure 11, a partial solution from [11] is borrowed for a similar scenario, that is, the unit fringe capacitance is proportional to the expression as given in (14):

$$C_{\text{fringe}} \sim \frac{\varepsilon_r \varepsilon_0 t}{y},$$

(14)

where y is the orthogonal distance between corners of two metal blocks, which is expressed as

$$y = \sqrt{d^2 + s^2} \,, \tag{15}$$

where d and s are vertical and horizontal distances of two corners respectively.

The suitable technology-dependent factor (i.e., the best fit for  $\beta$  in (16)) should be for the following equation in order to calculate fringe capacitance in this scenario: