# COMPILING A SYNCHRONOUS PROGRAMMING LANGUAGE INTO FIELD PROGRAMMABLE GATE ARRAYS

CENTRE FOR NEWFOUNDLAND STUDIES

### TOTAL OF 10 PAGES ONLY MAY BE XEROXED

(Without Author's Permission)

YING SHEN

## Compiling a Synchronous Programming Language into Field Programmable Gate Arrays

By

©Ying Shen, B.Eng., M.Eng.

A thesis submitted to the School of Graduate Studies in partial fulfilment of the requirements for the degree of Master of Engineering

Faculty of Engineering and Applied Science Memorial University of Newfoundland

May 1999

St. John's

Newfoundland

Canada

To my parents and my sisters

#### Abstract

This thesis shows how to compile a program expressed by a novel hardware description language, the State Machine Algol-Like Language (SMALL), into Field-Programmable Gate Arrays (FPGAs). A "netlist generator" for the SMALL language is created to transform a parallel Algorithmic State Machine (ASM) chart into a structural VHDL description. The one-hot encoding technique is used for the transformations. The structural VHDL description for the netlist is simulated and synthesised by Synopsys VSS (VHDL System Simulator) and Synopsys FPGA Compiler, respectively. The netlist is very simple and the components of the netlist consist of only D-type flip-flops and basic gates. The Design Manager of the Xilinx Alliance Series version 1.4 is used to produce configuration data for Xilinx FPGA chips. The Xilinx XC4000 family is employed as the target FPGA device.

The simulation results for several SMALL programs indicate that the netlist generator performs the specified requirements for all the statements and all the operators in the SMALL language.

Using the netlist generator and existing place-and-route tools makes the implementation of SMALL programs on FPGAs easy. This research offers a significant advance on the original SMALL implementation. Due to its simplicity and simple semantics, it is believed that the SMALL language will be widely used in many areas in the future.

### Acknowledgements

I would like to take this opportunity to appreciate the help and assistance from many people in my study for the degree of Master of Engineering. Particularly, I would like to thank my supervisor. Dr. Theodore S. Norvell, for his guidance and financial support through the program. His broad knowledge in Electrical and Computer Engineering has greatly helped in every stage of my research program. The generous financial support from Memorial University is also greatly appreciated.

I am very grateful for the assistance provided by my fellow graduate students. namely Mohsin Riaz, Yaser El-Sayed and Zhikai Ding in using some software packages. Thanks are also due Dr. James J. Sharp, Dr. Mahmoud R. Haddara and Mrs. Moya Crocker for their help during my graduate studies at Memorial.

Special appreciation goes to my parents who have stayed in St. John's for a whole year to look after my son Kevin during my graduate studies. Their dedication is very helpful to my family. Finally, I would like to thank my husband Fanyu for his help and encouragement.

# Contents

| Al | bstrac  | et                                                     | i   |

|----|---------|--------------------------------------------------------|-----|

| Ac | knov    | vledgements                                            | ii  |

| Co | onten   | ts                                                     | iii |

| Li | st of l | Figures                                                | vi  |

| Li | st of a | Abbreviations                                          | ix  |

| 1  | Intr    | oduction                                               | 1   |

| 2  | Lite    | rature Review                                          | 5   |

|    | 2.1     | SMALL: A Programming Language for State Machine Design | 5   |

|    |         | 2.1.1 The SMALL Language                               | 5   |

|    |         | 2.1.2 The Formal Semantics of SMALL                    | 8   |

|    |         | 2.1.3 An Example Program Written in SMALL              | 9   |

|    | 2.2     | The Original Implementation of the SMALL Language      | 11  |

|    | 2.3     | The Main Contributions of This Thesis                  | 14  |

|    | 2.4     | Related Work                                           | 14  |

| 3                                               | Des  | Design and Implementation of the Netlist Generator for SMALL |    |  |  |

|-------------------------------------------------|------|--------------------------------------------------------------|----|--|--|

|                                                 | 3.1  | Specification for the Netlist Generator                      |    |  |  |

|                                                 |      | 3.1.1 An Example ASM Chart                                   | 20 |  |  |

|                                                 |      | 3.1.2 Data Flow Diagram for the Netlist Generator            | 27 |  |  |

|                                                 | 3.2  | Utility Module                                               | 27 |  |  |

| 3.3 Netlist Module                              |      | Netlist Module                                               | 29 |  |  |

|                                                 |      | 3.3.1 Netlist                                                | 29 |  |  |

|                                                 |      | 3.3.2 Functions                                              | 30 |  |  |

|                                                 | 3.4  | Netlist State Module                                         | 31 |  |  |

|                                                 | 3.5  | A Module for Generating Signal and Register Circuits         | 32 |  |  |

|                                                 |      | 3.5.1 Generating Signal Circuits                             | 32 |  |  |

|                                                 |      | 3.5.2 Generating Register Circuits                           | 35 |  |  |

|                                                 | 3.6  | A Module for Generating Node Circuits                        | 37 |  |  |

| 3.7 A Module for Generating Expression Circuits |      | A Module for Generating Expression Circuits                  | 43 |  |  |

|                                                 | 3.8  | A Module for Connecting Node Circu.                          | 51 |  |  |

|                                                 | 3.9  | Output to VHDL Module                                        | 54 |  |  |

| 4                                               | Hare | dware Implementation of the SMALL Language with FPGA         | 59 |  |  |

| 4.1 Background                                  |      | Background                                                   | 60 |  |  |

|                                                 |      | 4.1.1 VHDL: VHSIC Hardware Description Language              | 60 |  |  |

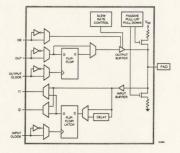

|                                                 |      | 4.1.2 Field Programmable Gate Arrays                         | 51 |  |  |

|                                                 |      | 4.1.3 The Design Procedure and Environment                   | 55 |  |  |

|                                                 | 4.2  | Simulation with the Structural VHDL Description              | 67 |  |  |

|    |       | 4.2.1           | Components                                                         |                                       | 67  |

|----|-------|-----------------|--------------------------------------------------------------------|---------------------------------------|-----|

|    |       | 4.2.2           | Test Benches                                                       |                                       | 70  |

|    |       | 4.2.3           | Simulation Results                                                 |                                       | 72  |

|    | 4.3   | Gate-L          | evel Synthesis                                                     |                                       | 92  |

|    | 4.4   | Hardw           | re Implementation with FPGA                                        |                                       | 92  |

| 5  | Con   | clusion         |                                                                    |                                       | 96  |

| Re | feren | ces             |                                                                    |                                       | 100 |

| A  |       |                 | Descriptions Representing the N<br>1ch for a Sequential Multiplier | etlist Circuit and                    | 103 |

| B  |       |                 | Descriptions Representing the N<br>ench for a Serial Adder         | etlist Circuit and                    | 116 |

| С  | Th    | e VHD<br>Test B | Descriptions Representing the Annual States of Two-I               | Array Types and<br>Dimensional Arrays | 121 |

| D  |       |                 | Descriptions Representing the A<br>the Operations of Three-Dimens  |                                       | 124 |

| E  |       |                 | Descriptions Representing the ench for Example 6                   | Netlist Circuit and                   | 127 |

| F  | A     | Brief In        | roduction to Gofer                                                 |                                       | 136 |

# **List of Figures**

| 1.1 The Framework of This Thesis                        |

|---------------------------------------------------------|

| 2.1 A Sequential Multiplier                             |

| 2.2 The Implementation of the SMALL Language 13         |

| 3.1 The Example SMALL Program                           |

| 3.2 A Timing Diagram of the Program Shown in Figure 3.1 |

| 3.3 The ASCII Form of the Example ASM Chart: Entities   |

| 3.4 The ASCII Form of the Example ASM Chart: Nodes      |

| 3.5 The ASCII Form of the Example ASM Chart: Edges      |

| 3.6 An Example ASM Chart                                |

| 3.7 Data Flow Diagram for the Netlist Generator         |

| 3.8 The Signal Circuits                                 |

| 3.9 The Register Circuits                               |

| 3.10 The Dummy Node Circuit                             |

| 3.11 The State Node Circuits                            |

| 3.12 The Assert Node Circuits                           |

| 3.13 The Assignment Node Circuits                       |

| 3.14 The Condition Node Circuit                         |

| 3.15 The Expression Circuits                            |

|                                                         |

| 3.16 A Ripple Carry Adder Circuit                                           |  |  |

|-----------------------------------------------------------------------------|--|--|

| 3.17 A Full Adder Circuit                                                   |  |  |

| 3.18 The Overflow Output Circuit for Operators: plus and                    |  |  |

| 3.19 A Simple SMALL Program                                                 |  |  |

| 3.20 An ASM Chart for the SMALL Program Shown in Figure 3.19                |  |  |

| 3.21 The Circuit of the SMALL Program Shown in Figure 3.19                  |  |  |

| 3.22 An Example VHDL Output Description                                     |  |  |

|                                                                             |  |  |

| 4.1 A Simplified Block Diagram of the XC4000 CLB                            |  |  |

| 4.2 The XC4000 IOB                                                          |  |  |

| 4.3 The XC4000 Interconnect                                                 |  |  |

| 4.4 The Test Bench for the VHDL Output Shown in Figure 3.22                 |  |  |

| 4.5 A Parity Generator Written in the SMALL Language                        |  |  |

| 4.6 The Structural VHDL Output for a Parity Generator Shown in Figure 4.575 |  |  |

| 4.7 The Test Bench for the VHDL Output Shown in Figure 4.6                  |  |  |

| 4.8 The Simulation Result of a Parity Generator Shown in Figure 3.1         |  |  |

| 4.9 The Simulation Result of a Parity Generator Shown in Figure 4.5         |  |  |

| 4.10 The Simulation Result of a Sequential Multiplier Shown in Figure 2.1   |  |  |

| 4.11 A Serial Adder Written in the SMALL Language                           |  |  |

| 4.12 The Simulation Result of a Serial Adder Shown in Figure 4.11           |  |  |

| 4.13 The SMALL Program for Example 4                                        |  |  |

| 4.14 The Simulation Result of the SMALL Program Shown in Figure 4.13        |  |  |

| 4.15 The SMALL Program for Example 5                                        |  |  |

| 4.16   | The Simulation Result of the SMALL Program Shown in Figure 4.15 88 |

|--------|--------------------------------------------------------------------|

| 4.17   | The SMALL Program Used in Pattern Matching                         |

| 4.18   | The Simulation Result of the SMALL Program Shown in Figure 4.1791  |

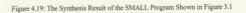

| 4.19   | The Synthesis Result of the SMALL Program Shown in Figure 3.1      |

| 4.20   | The Synthesis Result of the SMALL Program Shown in Figure 2.1      |

| A.1    | The Structural VHDL Output Description for a Sequential Multiplier |

| A.2    | The VHDL Description of the Test Bench for a Sequential Multiplier |

| B.1    | The Structural VHDL Output Description for a Serial Adder 119      |

| B.2    | The VHDL Description of the Test Bench for a Serial Adder 120      |

| C.1    | The VHDL Description for Data Types Used in Example 4              |

| C.2. 1 | The VHDL Description of the Test Bench for Example 4               |

| D.1    | The VHDL Description for Data Types Used in Example 5              |

| D.2    | The VHDL Description of the Test Bench for Example 5               |

| E.1    | The VHDL Description for the Netlist Circuit of Example 6          |

| E.2    | The VHDL Description for the Test Bench of Example 6               |

# List of Abbreviations

- ASM Chart Algorithmic State Machine Chart.

- ASIC Application Specific Integrated Circuit.

- CAD Computer-Aided Design.

- CLB Configurable Logic Block.

- CMC Canadian Microelectronics Corporation.

- DPGA Dynamically Programmable Gate Array.

- FPGA Field Programmable Gate Array.

- IOB Input/Output Block.

- SMALL State Machine Algol-Like Language.

- Synopsys FC Synopsys FPGA Compiler.

- Synopsys VSS Synopsys VHDL System Simulator.

- VHDL VHSIC Hardware Description Language.

- VHSIC Very High Speed Integrated Circuit.

# **Chapter 1**

### Introduction

Several hundreds of hardware description languages have been presented in the past decades (Wodtko, 1987). Only some of these languages are designed to describe synchronous behavior. SMALL (State Machine Algol-Like Language) is a novel hardware description language that has been developed especially for both teaching and synchronous state-machine design purposes by Norvell (1997) at Memorial University of Newfoundland. It consists of a simple set of symbols and notations that replace schematic diagrams of digital circuits. SMALL, as a hardware-oriented programming language, could be applied into many areas as follows (Norvell, 1996 and 1997).

- · It is oriented toward teaching sequential circuit design.

- It can be embedded in a larger specification language.

- It can aid design communication, hardware simulation and the transformation of designs from a higher level (such as state machine) to a lower level (such as gates).

- It can be used in design derivation from specification.

- It can be used in rapid development.

The program written in SMALL can be directly compiled into hardware without human intervention.

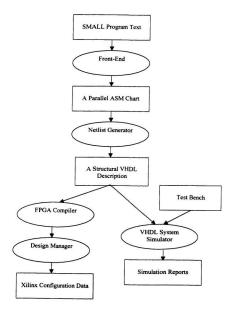

Due to its simplicity in sequential circuit design, in formal semantics. and in time model, the SMALL language will be more widely used in the future and its further development becomes more important. The purpose of this thesis is to compile programs expressed in the SMALL language into Field-Programmable Gate Arrays (FPGAs), a technology that allows a design expressed in the SMALL language to be implemented without a conventional fabrication plant. The entire compilation process can be divided into the four stages shown in Figure 1.1. First, the text of a SMALL program is converted to a parallel Algorithmic State Machine (ASM) chart. At the second stage, the netlist for the SMALL program is created. The next stage is to synthesise from the structural VHDL (The VHSIC Hardware Description Language) netlist. The final stage implements the netlist using a specific Xilinx FPGA chip. It should be noted that the functional simulation is carried out in order to verify that the Netlist Generator performs the specified requirements before the third stage.

The Netlist Generator is written in the functional language Gofer (Jones, 1991, 1993, and 1994; Cunningham, 1995; and Wadler, 1995). The input to the Netlist Generator is a parallel ASM (Algorithmic State Machine) chart that is generated by the compiler's front-end. Its output is a structural VHDL source file describing a netlist composed of simple gates and flip-flops. Synopsys VSS (VHDL System Simulator) is used for simulation that verifies the netlist circuit created by the Netlist Generator matches the requirements. Synopsys FPGA Compiler (FC) is adopted for synthesising the gate-level

Figure 1.1: The Framework of This Thesis

VHDL description and automatic hardware generation. Design Manager of the Xilinx Alliance Series version 1.4 is employed to produce the configuration data for a specific Xilinx FPGA chip. The Xilinx XC4000 family FPGA logic is chosen as the target technology.

The rest of this thesis is organised as follows:

Chapter 2 provides an introduction to the SMALL programming language and discusses related approaches.

Chapter 3 describes in detail the design and implementation of the Netlist Generator for the SMALL language, including algorithm descriptions and translation circuits.

Chapter 4 gives the hardware implementation of the netlist for the SMALL language using a Field Programmable Gate Array (FPGA). Several examples are simulated to verify that the Netlist Generator produced in Chapter 3 meets the specified requirements.

Finally, Chapter 5 contains some concluding remarks.

## Chapter 2

### **Literature Review**

This chapter is intended to provide an introduction to the SMALL programming language and to review related work. An understanding of the original implementation of the SMALL language will be helpful in order to comprehend the Netlist Generator. An example of a SMALL program used for synthesis and simulation in later chapters is also presented.

### 2.1 SMALL: A Programming Language for State Machine Design

One essential contribution of this thesis is the creation of a Netlist Generator for the SMALL programming language. In order to understand the design and implementation of the Netlist Generator, this section briefly describes the SMALL programming language. The following is a review based on the SMALL documentation (Norvell, 1996).

### 2.1.1 The SMALL Language

SMALL stands for State Machine Algol-Like Language. Its relationship to ASM

charts is almost the same as the relationship between high-level software languages (like Algol) and flow charts. In the SMALL language, signals are used to carry information instantaneously and registers are used for storing information through time. The value of a signal is determined in the current clock period; however, the value of a register is the latest value assigned to it in a previous clock period. The following two forms are used for the declarations of the signals and the registers, respectively.

#### sig signal\_name TC

#### req register name TC

In the above forms, sig and reg are keywords; signal\_name and register\_name are identifiers. T is a type that is either bool or array n of T at present and C is the scope of the declarations. In order to communicate with external world, the keyword global could be added to the beginning of the declarations.

The statements in the SMALL language include:

- s ! expression which places data on a signal s; this is called as "assert statement".

- r <- expression which places data in a register r; this is called as "assignment statement".

- · tick which expresses the end of one clock and the start of the next.

- statement\_0 statement\_1 ... statement\_n which represents a sequence of statements executed consecutively from left to right.

- if expression then statement\_0 else statement\_l fi which is an alternative composition and means that when the expression is true, the statement statement\_0 is executed; otherwise, the statement statement l is executed.

- while expression do statement od whose meaning is that the statement is executed if the expression is true; the expression is reevaluated in the clock period following the completion of the statement.

- repeat statement until expression whose meaning is that the statement is executed, and if the expression is true in the last clock period of the statement, the repeat statement is complete; otherwise, the loop is restarted in the next clock period.

- par statement\_0 || statement\_1 || ... || statement\_n rap which is a parallel composition and which will end as soon as all the processes have ended.

- skip which simply ends immediately.

- stop which stops the interpreter.

In the SMALL language, the concept of duration is important. It is defined as the difference between the initial and final clock period by Norvell (1997). According to the definition, the duration of assert and assignment statements is 0; tick and skip have duration 1 and 0, respectively. The duration of a parallel statement is the maximum of the duration of the processes and that of a sequence of statements is the sum of the duration of each statement. In the sequence of statements, the final clock period of *statement\_i* is also the initial clock period of *statement\_i+1*. For the alternative composition, whether *statement\_0* or *statement\_1* is chosen, the start time of the chosen statement is the same as the start time of the whole alternative composition. The finish time of the alternative composition depends on the finish time of *statement\_0* when the value of the *expression*, the finish time is true at the start time. In the case of a false value for the *expression*, the finish time of the alternative composition is the same as the finish time of statement\_l. For the while statement, when the expression is true during a clock period, the statement is executed in the same clock period and the loop is restarted in the first clock period after the last clock period used by the statement; when the expression is false, the while statement ends immediately. Therefore, the duration of the while statement is related to its loops. Similar to the while statement, the duration of the repeat statement is also related to its loops. Both looping forms imply a delay immediately before the loop is restarted.

A number of the operators constitute expressions. The expressions are divided into seven categories, including identifiers, constants, unary expressions, binary expressions, subscript expressions, subarray expressions and array expressions. In the next section, an example will be given to illustrate the above statements and some operators in the SMALL language.

#### 2.1.2 The Formal Semantics of SMALL

A specification is a predicate on behaviours. In SMALL, the starting time, the final time, and values of signals and registers over all time are used to describe the behaviours. The following variables representing times and time varying functions describe the behaviour of a command with a global signal  $s: T_s$  and a global register r:

Tr.

| t : xnat                | The starting time.                       |

|-------------------------|------------------------------------------|

| t': xnat                | The final time.                          |

| s : wire.T <sub>s</sub> | The value of s during each clock period. |

| s : wire.bool            | Whether s is asserted during each clock period.         |

|--------------------------|---------------------------------------------------------|

| r : wire. T <sub>5</sub> | The value of r during each clock period.                |

| F : wire.bool            | Whether r receives a new value after each clock period. |

In the above definition, *xnat* is a set of times and *wire*. *T* represents a function. *xnat* and *wire*. *T* are defined as follows:

$$xnat = nat \cup \infty$$

wire.  $T = xnat \rightarrow T$

The formal semantics is determined by semantic equations which are presented in (Norvell, 1997). Their definitions include that primitive commands are specifications and that composition operators equal operators on specifications.

The following example specification obtained from (Norvell, 1997) can explain some simple semantics.

$$t' = t + 1 \wedge \bar{s} \cdot t \wedge s \cdot t = r \cdot t \wedge \bar{r} \cdot t \wedge r \cdot (t + 1) = 10$$

A command that implements this specification will have the following meanings:

- · The duration of the command is 1.

- · During its first clock period, the signal s has the same value as the register r.

- 10 will be assigned to r between its two clock periods.

#### 2.1.3 An Example Program Written in SMALL

Figure 2.1 shows an example written in SMALL to illustrate many expressions and statements in the language. This example is obtained from (Norvell, 1996) and will be synthesised and simulated in Chapter 4.

```

1/0

par

global signal go : bool

1/1

global signal done : bool

112

global signal multiplier : array 4 of bool

113

global signal multiplicand : array 4 of bool

11.4

global reg p : array 8 of bool

115

while true do

116

reg d: array 4 of bool

117

reg b: array 4 of bool

// 8

reg count: array 2 of bool

119

repeat // Initialize while waiting to start.

//10

p[404] <- 4 of 0

//11

count <- 0 as 2 bits

a <- multiplicand

//13

b <- multiplier

//14

until go

//15

tick

//16

repeat // Invariant: the product thus far (multiplicand * the first

//17

//count bits of multiplier) is the last 4+count bits of p.

//18

// Form product of a and b(0].

//19

signal DD : array 4 of bool

//20

if b(0) then pp !a else pp ! 4 of 0 fi

//21

// Add this to the most significant 4 bits of p.

1177

signal sum : array 5 of bool

1173

sum ! p[4@4] uplus pp // Replace the top 4 bits of the

1/24

// product with the 5 bit sum. To make room, shift,

1/25

p[503] <-sum

//26

1127

p[300] <-p[301]

b <- b[301] ++ [0]

1128

count <- count plus (1 as 2 bits)

1170

until count = 3 as 2 bits

//30

tick

//31

repeat done ! 1 until not go

1/32

od

1/33

1/34

global signal go : bool

//35

global signal done : bool

1/36

global signal multiplier : array 4 of bool

1/37

global signal multiplicand : array 4 of bool

//38

go!1 multiplier ! [1, 1, 0, 0] multiplicand ! [0, 1, 0, 0]

1/30

tick

//40

repeat skip until done

//41

//42

rap

```

Figure 2.1: A Sequential Multiplier

The example in Figure 2.1 is used to multiply two 4-bit numbers to produce an 8-bit result. It produces one partial product in each clock period. By shifting the partial product and adding the multiplicand if a bit in the multiplier is 1 in each clock period, the final product can be obtained after five clock periods. Many signal and register declarations and statements appear. For example, Line 0 to Line 42 is a parallel composition. Assert statements and assignment statements are used to send data to the signals or the registers. For example, the statements such as p[404] <- 4 of 0, multiplier ! [1,1,0,0], and multiplicand ! [0,1,0,0] initialise the partial product the multiplier, and the multiplicand, respectively. There are many expressions and operators in the example. For instance, the expression, p[404] in Line 11, presents the segment of length 4 beginning at index 4 and the '4 of 0' expresses an array of length 4 that is the same as 10, 0, 0, 01. Because index 0 is used for the least significant bit, the expression 'las 2 bits' in Line 29 means the 2 bits unsigned magnitude representation of 1 and has the value [1,0]. The operators such as 'uplus' in Line 24, '++' in Line 28 and 'plus' in Line 29 distribute to array of boolean level. From the above example, it is shown that SMALL has many distinguishing features that other hardware description languages lack. Compared with other hardware description languages, SMALL's simplicity will help it to be used in many practical areas.

#### 2.2 The Original Implementation of the SMALL Language

The following paragraph from (Norvell, 1996) describes the original implementation of the SMALL language. The current implementation is in Gotr version 2.30 and uses the prelude cc.prelude. Goter is a functional language designed and implemented by Mark P. Jones and is very similar to Haskell. Extensive use is made of monads and an imperative programming style.

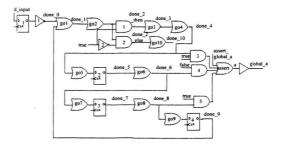

The implementation of the SMALL language is shown in Figure 2.2. The original implementation consists of all components other than the Netlist Generator. In Figure 2.2, the front-end is composed of Lexer, Parser, and Analyzer. The function of each component shown in Figure 2.2 is described in the following.

The lexer takes a source program written in the SMALL language as its input and outputs a token sequence. The parser creates an abstract syntax tree and finds all syntax errors. The analyzer creates an intermediate representation of the source program from the abstract syntax tree. It has several functions. The first is to check the source program for compile-time errors such as type errors and misuses of identifiers. The second is to produce a requirement table that is a list of all signals and registers, including the extra signals introduced for each process in order to coordinate termination of the parallel processes. These signals and registers are used to run the program. The last function is the generation of an ASM chart representation of the program. The ASM chart expresses the control-flow of the source program. It is a collection of nodes connected by directed edges. Nodes are divided into five varieties: state nodes, dummy nodes, asset nodes, assignment nodes, and condition nodes and are labeled by expressions. The next step is one of two alternatives. Either the executer simulates execution of the ASM chart with test inputs, or the Netlist Generator translates the ASM chart to a gate-level

Source Program Written in SMALL

Figure 2.2: The Implementation of the SMALL Language

Original Implementation

implementation in terms of gates and flip-flops.

### 2.3 The Main Contributions of This Thesis

One essential contribution of this thesis is the creation of a Netlist Generator for the SMALL programming Language. The ASM chart and requirements table is taken as the input to the Netlist Generator. The output will be a netlist composed of gates and flipflops and expressed by a VHDL entity declaration and a structural architecture declaration. The Synopsys VSS is used for the functional simulation of the structural VHDL description to verify that the Netlist Generator performs the specified requirements. The detailed design and implementation of the Netlist Generator for the SMALL language will be presented in the following chapter.

Another contribution of this thesis is to implement such netlists with FPGAs. The Synopsys FPGA Compiler is adopted for the gate-level synthesis and logic optimisation. The Design Manager of the Xilinx Alliance Series is used to create configuration data for Xilinx FPGA chips. Some information about pre-placement and routing and post-layout for implementing a sequential multiplier shown in Figure 2.2 on a Xilinx XC4028EX-3-PG299 FPGA will be provided in Section 4.4.

#### 2.4 Related Work

There has been some previous work on compiling a program written in a selected language into hardware, such as FPGAs and silicon. The difference between synchronous and asynchronous methods for controlling the timing in circuits should be noted. In synchronous communication, a message is sent and received simultaneously, without communication delay. An asynchronous communication has a time delay when a message is sent and received. Usually, local handshaking signals are used in the asynchronous method; a global clock is used in the synchronous method. The following is a review of the related work.

An early work is done by Martin (1986). He developed a compiler from a concurrent programming language into delay-insensitive circuits that are obtained by a series of semantics-preserving transformations. The compilation is divided into the four steps: process decomposition, handshaking expansion, production-rule expansion, and operator reduction. The circuits are correct by construction.

The work of Weber et al. (1992a and 1992b) on Joy, a simple yet complete programming language for circuits, is similar to that of Martin. They have modelled delay-insensitive circuits as directed graphs and proved the correctness of their compilation algorithm. The resulting circuits are composed of some primary components; each of the components is described by a wiring diagram and a finite-state automaton.

Guo and Luk (1995) have provided a methodology for compiling a design expressed in the Ruby language into FPGAs. The Ruby language is intended for the specification and synthesis of the circuits described by relational abstractions of their behaviour (Rossen, 1990) and allows simple relations to be composed into more complicated ones by using higher-order functions. With mathematically based compilation tools, the correct hardware can be produced from high-level descriptions very rapidly. The refinement module and the floorplanning module of their compilation system are also discussed in detail.

Another close work presented by Berry and Gonthier (1992) and Jagadeesan et al. (1995) has involved the hardware implementation of the ESTEREL synchronous programming language which is based on the "Synchrony Hypothesis" and has welldefined mathematical semantics. Berry and Gonthier have shown an algorithm to translate ESTEREL programs into deterministic automata. Berry (1995) has provided the direct hardware implementation that transforms ESTEREL programs into boolean circuits by using the current ESTEREL hardware or software compiling and verification technology.

LUSTRE is a synchronous declarative language devoted to real-time systems and is suitable for data path description. Thuau and Pilaud (1990) have divided the compilation of a LUSTRE program into two steps: expanding all the nodes to get a single system of equations and producing a finite automaton. The verification tool LESAR is developed for proving the correctness of a circuit.

The VHDL (Lipsett et al., 1989; Patterson, 1994) and Verilog (Thomas and Moorby, 1991) languages provide the digital system designer with accurate description and modelling of a system at a wide range of levels, from the highest behavioural level of abstraction to the lowest structural gate level. Many people are interested in circuit synthesis with VHDL or Verilog. Greaves (1995) has worked on defining formal semantics for the Verilog language that is used for simulation and compilation into hardware. Gschwind and Salapura (1995) have proposed a VHDL design methodology for FPGAs to integrate the modelling, verification and implementation processes.

Hehner et al. (1998) presented two new ways to implement ordinary programs with logic gates. They have adopted local delays and given a framework for the proof of correct circuits in terms of a formal semantics for programs and circuits.

The most closely related work is conducted by Page and his group (Page and Luk, 1991; He et al., 1993; and Page, 1996). They have compiled programs written in a subset of occam into FPGAs. A "normal form" method (He et al., 1993) is used for processing into a netlist and for proving the correctness of their compilation. Page and Luk (1991) have described a prototype compiler written in the functional language SML that transforms Handel, an occam-like language, to a netlist. Page (1996) has further implemented his hardware-software codesign by compiling the Handel language into a netlist, which is suitable for Xilinx Dynamically Programmable Gate Arrays (DPGAs) technology.

This research is also related to and influenced by the above work. We have focused on compiling programs in the SMALL language into a netlist, which can be loaded into a Xilinx FPGA. Compared with the work of Page *et al.*, the main difference is that, Page *et al.* considered the implementation of control hardware for channel communication and used a flip-flop in their assignment control hardware; this research has not. This is because assignment statements and assert statements in SMALL have a duration of 0 rather than 1.

The one-hot encoding is used as the encoding technique in this thesis. It uses one flipflop per state node. Gschwind and Salapura (1995) have proved that one-hot encoding is both the fastest encoding and one of the smallest representations as it makes the best use of the flip-flops on an FPGA.

# **Chapter 3**

# Design and Implementation of the Netlist Generator for SMALL

The purpose of this thesis is to compile programs expressed in the SMALL language into FPGAs. To do so, a Netlist Generator for the SMALL language has been created to transform parallel ASM charts to structural VHDL files. The ASM chart is obtained after the source SMALL program is processed by the front-end stage shown in Figure 2.2. The VHDL file describes a netlist that is a collection of devices and wires implementing the program. The devices in our netlist consist of simple gates and D-type flip-flops. The Netlist Generator is programmed using the functional language Gofer (Jones, 1994; Cunningham, 1995; and Wadler, 1995). Based on (Norvell, 1998), this chapter will give detailed design and implementation for the Netlist Generator.

### 3.1 Specification for the Netlist Generator

The input to the Netlist Generator is an ASM chart. The output will be a VHDL file composed of an entity declaration for a device and a structural architecture for the same device. This section will provide an example ASM chart and the data-flow diagram for the Netlist Generator. An example VHDL description will be given in Section 3.9.

#### 3.1.1 An Example ASM Chart

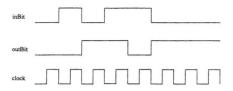

In order to illustrate ASM charts, Figure 3.1 shows a simple SMALL program describing a parity generator and some test inputs. The function of the program is that at each clock period, the *outBit* is the parity of those *inBits* that have been seen in the previous clock periods. A timing diagram of the program is given in Figure 3.2. It can be seen that in Figure 3.2, the output named *outBit* is (0, 0, 1, 1, 0) if the input named *inBiti* is (0, 1, 0, 1, 1) in the first five clock periods.

```

global sig inBit: bool

global sig outBit: bool

par

while true do

repeat

outBit ! 0

until inBit

tick

repeat

outBit ! 1

until inBit

od

L L

inBit ! 0

tick

inBit ! 1

tick

inBit 1 0

tick

inBit ! 1

tick

inBit ! 1

tick

rap

```

Figure 3.1: The Example SMALL Program

Figure 3.2: A Timing Diagram of the Program Shown in Figure 3.1

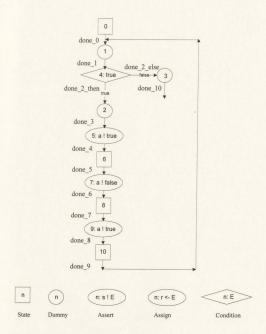

This program shown in Figure 3.1 can be converted to a parallel ASM chart form by a front-end that has been implemented by Norvell. It is noted that a requirements table is included in the parallel ASM chart in this chapter. The ASCII descriptions of the ASM chart of the SMALL program are shown in Figure 3.3, in Figure 3.4, and in Figure 3.5. A diagram of the ASM chart appears in Figure 3.6.

("inBit",Signal "inBit"True of type bool) ("outBit",Signal "outBit"True of type bool) ("#r\*1",Signal "#r\*1"True of type bool) ("#!\*0",Signal "#1\*0"True of type bool)

Figure 3.3: The ASCII Form of the Example ASM Chart: Entities

ASM charts are composed of "Entities", "Nodes", and "Edges". The collection of entities shown in Figure 3.3 is called a "requirements table" and lists all the registers and signals used for communication across space or time in the source program. The requirements table provides the following information for each entity:

- · The name of the entity.

- · Whether the entity is a signal or register.

- · Whether the entity is local or global.

- · For a signal entity, the active value of the signal.

- · The entity's type, that is, bool or an array.

It is noted that signals "#r\*1" and "#1\*0" shown in Figure 3.3 are introduced in order to coordinate termination of the parallel processes.

Figure 3.4 represents a collection of nodes. These nodes are divided into five kinds: state nodes, dummy nodes, assert nodes, assignment nodes, and condition nodes. For each node, the node number and the node type are needed. Additional expressions are used for the assert nodes, the assignment nodes, and the condition nodes. Assert nodes and assignment nodes are labelled with two expressions representing the target signal or register and the value. The expression labelling a condition node is a boolean and is used to determine which branch is taken. Condition nodes are also labelled with the numbers of the nodes to branch to. Their detailed descriptions are given in Section 3.6, which discusses the generation of circuits for nodes.

The ASM Chart is 36 GRAPH Labels (35.%CondNd (#1\*0.((22.17).bool)) then 31 else 34) (34,%StateNd) (33,%CondNd (#r\*1.((22,17),bool)) then 31 else 32) (32,%StateNd) (31 %DummyNd) (30.%AssertNd(#r\*1.((22,17),bool))!(True.((22,17),bool))) (29.%AssertNd(#1\*0.((22,17),bool))!(True.((22,17),bool))) (28.%StateNd) (27.%AssertNd(inBit.((27.17).bool))!(True.((27.25).bool))) (26.%StateNd) (25.%AssertNd(inBit,((26,17),bool))!(True.((26,25),bool))) (24.%StateNd) (23,%AssertNd(inBit.((25,17),bool))!(False.((25,25),bool))) (22 %StateNd) (21,%AssertNd(inBit,((24,17),bool))!(True,((24,25),bool))) (20.%StateNd) (19.%AssertNd(inBit.((23.17).bool))!(False.((23.25).bool))) (18.%StateNd) (17.%StateNd) (16,%CondNd (inBit,((20,28),bool)) then 14 else 15) (15.%DummvNd) (14.%DummvNd) (13.%AssertNd(outBit.((19.27).bool))!(True.((19.36).bool))) (12.%DummvNd) (11 %StateNd) (10 %StateNd) (9,%CondNd (inBit,((16,28),bool)) then 7 else 8) (8,%DummyNd) (7.%DummvNd) (6.%AssertNd(outBit.((15.27).bool))!(False.((15.36).bool))) (5.%DummyNd) (4.%CondNd (True.((13.23).bool)) then 2 else 3) (3.%DummyNd) (2,%DummyNd) (1,%DummyNd) (0,%StateNd)

Figure 3.4: The ASCII Form of the Example ASM Chart: Nodes

| Adjacency                                                               |

|-------------------------------------------------------------------------|

| (34,[30])                                                               |

| (32,[29])                                                               |

| (30,[35])                                                               |

| (35,[])                                                                 |

| (29,[33])                                                               |

| (33.[])                                                                 |

| (31,[])                                                                 |

| (28 [30])                                                               |

| (28.[30])<br>(3.[29])<br>(27,[28])<br>(26,[27])                         |

| (27 [28])                                                               |

| (26 (27))                                                               |

| (25,[26])                                                               |

| (24,[25])                                                               |

| (23.[24])                                                               |

| (23,[24])                                                               |

| (22,[23])                                                               |

| (20.[21])                                                               |

| (19.[20])                                                               |

| (0.[19,1])                                                              |

| (0.[19,1])                                                              |

| (18,[1])                                                                |

| (16,[1])<br>(14,[18])<br>(17,[12])<br>(15,[17])<br>(13,[16])<br>(16,[]) |

| (17.[12])                                                               |

| (13,[17])                                                               |

| (15,[10])                                                               |

| (12.[13])                                                               |

| (12.[13])                                                               |

| (11, [12])<br>(7, [11])                                                 |

|                                                                         |

| (10.[5])                                                                |

| (8,[10])                                                                |

| (6,[9])                                                                 |

| (9,[])                                                                  |

| (5,[6])                                                                 |

| (2,[5])                                                                 |

| (1,[4])                                                                 |

| (4,[])                                                                  |

|                                                                         |

Figure 3.5: The ASCII Form of the Example ASM chart: Edges

The edges shown in Figure 3.5 express a collection of references to successor nodes. They are very useful in connecting nodes. These edges and the nodes shown in Figure 3.4 form a node-labelled directed graph. Figure 3.6 shows the graph of the example ASM chart that represents the control-flow of the source program in Figure 3.1. In Figure 3.6, the first node is always a state node named Node 0. It represents the start of the program. In this example, a parallel statement appears at the beginning of the program so that a parallel branch is produced. Therefore, Node 0 has Node 1 and Node 19 as its successor nodes. For each tick statement, each while loop, and each repeat loop in the source program, the front-end will generate one state node. These state nodes represent the control state of the program. They are used to wait for the coming of the next clock. For assert nodes, assignment nodes, and dummy nodes, no timing delay exists. Condition nodes are generated for while loops and repeat loops. Each condition node has two branch nodes as its successor.

Expressions come in seven forms: identifier expressions, constant expressions, unary expressions, binary expressions, subscripted array expressions, subarray expressions, and array building expressions. Each expression consists of its type and its location (line number and column number) in the source program. The detailed discussion about expressions will be given in the Section 3.7, which describes generating expression circuits.

It is believed that the clear understanding of the ASM chart is very important for understanding the netlist generation.

Figure 3.6: An Example ASM Chart

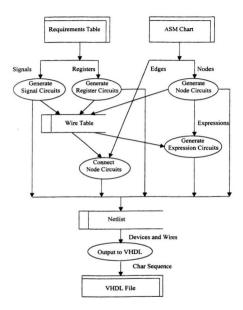

## 3.1.2 Data Flow Diagram for the Netlist Generator

Figure 3.7 gives the data flow diagram for the Netlist Generator. The processes for the Netlist Generator include the following:

- · Generate the circuits of signals and registers according to "Entities" in Figure 3.3.

- Generate node circuits in terms of "Nodes" in Figure 3.4.

- · Generate the circuits of expressions for the nodes that have the expressions.

- Link all the above circuits according to the edges of the graph in Figure 3.5.

- Form an output VHDL file representing the final circuits stored in the "Netlist" shown in Figure 3.7.

The following sections will describe the modules that implement the above processes, including the algorithms and the resulting circuits.

# 3.2 Utility Module

This module has defined some useful data types and useful functions. Gofer notations used in this module and other modules are explained in Appendix F. Especially, the Assoc type constructor is widely used in this thesis. Its definition is as follows:

type Assoc

$$a \ b = [(a, b)]$$

In the above type synonym, Assoc is the name of a new type constructor; a and b are type variables representing the arguments of Assoc. [(a, b)] is a type expression. Assoc a b represents a finite map that associates members of type a with members of type b.

Figure 3.7: Data Flow Diagram for the Netlist Generator

#### 3.3 Netlist Module

In this section, the data structure of the netlist and the types of gates and flip-flops used in the netlist are defined. The functions that create wires and connect devices are also described.

#### 3.3.1 Netlist

The netlist consists of devices and wires. The devices chosen in this study include multi-input and one-output gates such as or-gates, and-gates and xor-gates, one-input and one-output gates such as not-gates and buffers, and D-type flip-flops.

For the devices, a data type named DeviceKind is defined in the following form.

| data DeviceKind = DevK String | Device name  |  |

|-------------------------------|--------------|--|

| [(PortName, Bool)]            | Input ports  |  |

| [PortName]                    | Output ports |  |

The String represents the device name. The type named PortName is the same as String and is used to indicate whether the port is input or output. In the case of input ports, the **Bool** is used to describe whether the port can connect to more than one wire.

The devices used in the netlist are defined as follows:

andGate, orGate, vorGate, inverter, dFlipFlop, buffer :: DeviceKind andGate = DevK \*AhD2" [("in", **True**]] ["our"] orGate = DevK \*VOR2" [("in", **True**]] ["our"] inverter = DevK \*NDFRIEE" [("in", **False**]] ["our"] dFlipFlop = DevK \*DFLIPFLOP" [["in", **True**]] ["our"] dFlipFlop = DevK \*DFLIPFLOP" [["in", **True**]] ["our"] dFlipFlop = DevK \*DFLIPFLOP" [["in", **True**]] ["our"] For the wires, the type InOutLoc is an enumerated type defined as

| data | InOutLoc = | In String  | Input wire  |

|------|------------|------------|-------------|

|      |            | Out String | Output wire |

|      |            | Local      | Local wire  |

The String in the above definition represents the wire name.

For the netlist, its type is defined as

data Netlist = NL Int ---- The number of devices and wires (Assoc DeviceID DeviceKind) ---- Device map (Assoc DeviceID InOuaLoc) ---- Wire map (Assoc DeviceID (Assoc PortName [WireID])) ---- Connection map

In the above form, the type named *Device/D* and the type named *Wire/D* represent the identifiers of devices and wires, respectively. From the definition of the type *Netlist*, it can be seen that the data structure of the netlist shows the characteristics of devices and wires and the relationship between the device and its wires.

#### 3.3.2 Functions

The functions exported from the Netlist module are called *createDovice*, createLocalWire, createInputWire, createOutputWire, and connect. They have the following meanings:

- createDevice is used to create devices.

- createLocalWire, createInputWire, and createOutputWire are used to create local wires, input wires, and output wires, respectively.

- connect is used to connect wires to ports of devices. This function needs to check that

the device has the port and then to confirm that, unless permitted, the port is not

already connected: otherwise the error information will be given.

# 3.4 Netlist State Module

This module defines some data types and some functions. For the Netlist state, the tuple type named NLGState is defined as (Netlist, WireTab, ReqTab). The type named ReqTab is intended to describe the characteristics of the signals and registers. The type named WireTab represents a function from Strings to WireTabEntries. WireTab and WireTabEntries are declared as follows:

#### data WireTabEntry

| = WTELocSig DeviceID    | the identifier of the input gate.                    |

|-------------------------|------------------------------------------------------|

| WireID                  | the identifier of the wire named s.                  |

| WTEGlobSig DeviceID     | the identifier of the input gate.                    |

| WireID                  | the identifier of the input wire named               |

|                         | assert global s.                                     |

| WireID                  | the identifier of the wire named s.                  |

| WTELocReg DeviceID      | - the identifier of the input gate named val.        |

| DeviceID                | - the identifier of the input gate named assign.     |

| WireID                  | the identifier of the wire named r.                  |

| WTEGlobReg DeviceID     | the identifier of the input gate named val.          |

| DeviceID                | the identifier of the input gate named assign.       |

| WirelD                  | the identifier of the input wire named val global r. |

| WirelD                  | the identifier of the input wire named               |

|                         | assign global r.                                     |

| WireID                  | the identifier of the wire named r.                  |

| WTENode DeviceID        | the identifier of the input gate named go.           |

| WireID                  | the identifier of the output wire named done_N.      |

| WTECondNode DeviceID    | the identifier of the input gate named go.           |

| WirelD                  | the identifier of the done N then wire.              |

| WirelD                  | the identifier of the done_N_else wire.              |

| Node                    | the identifier of the gate named thenNode            |

| Node                    | the identifier of the gate named elseNode            |

| WTEDataType String      | -                                                    |

| SigWToDevice DeviceID S | tring                                                |

| RegWToDevice DeviceID   |                                                      |

| 2 (T)                   | -                                                    |

type WireTab = Assoc String WireTabEntry

The type named WireTabEntry contains information such as the identifiers of input gates and output wires for nodes, for local signals, and for local registers. For global signals and global registers, additional identifiers of input wires are needed. The information about signals and registers will be used in the generating signal and register circuits module and the generating expression circuits module. For condition nodes, additional identifiers of nodes are used to choose the control flow. The information about condition nodes is used in connecting node circuits module. The last three lines in WireTabEntry declaration are used to keep the names of signals and registers for output. Functions such as createDeviceM, createInputWireM, createOutputWireM, createLocalWireM, and connectM are the monad forms of the functions defined in the netlist module. The functions named updateWireTabM and updateRegTabM update the wire table and the requirements table.

#### 3.5 A Module for Generating Signal and Register Circuits

One of the processes for the Netlist Generator is to transform all the signals and registers used in the source program into their circuit descriptions. The algorithms for the transformation and the resulting circuits are shown in this section.

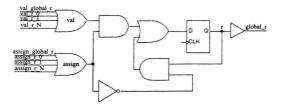

#### 3.5.1 Generating Signal Circuits

In the SMALL language, signals are used to carry information through space and the values of the signals are determined in the current clock period. Figure 3.8 shows the

circuit representations of the signals in the requirements table. It is noted that signals have an active level. The value of the active level of a signal depends on the default value that is the value of the signal in clock periods where it is not asserted. The default value of an active true signal is false and vice-versa. According to the definition and the assert node circuit, an or-gate is chosen in active-true signal circuit as shown in Figure 3.8(a) and Figure 3.8(c). An and-gate is used in active-false signal circuit as shown in Figure 3.8(b) and Figure 3.8(d). In Figure 3.8(c), an input wire named assert global s, an orgate named assert, and its output wire named s are used to represent an active-true global signal s. The circuit representation of each active-false global signal s is shown in Figure 3.8(d). It consists of an input wire named assert global s, an and-gate named assert, and its output wire named s. The buffer and its output wire named global s as shown in Figure 3.8(c) and Figure 3.8(d) are added for the need of the output VHDL file. In the specification of the Netlist Generator, every global signal is defined as the output port of the VHDL file that can not be used as an input to an internal component. Therefore, the signal s is used as both input and output and global s is only used as an output port. The same goes for registers. It is noted that input wires named assert s 0, assert s 1, and assert\_s\_N are not generated here and only shown for illustrative purpose. They are from the outputs of the and-gates or or-gates produced in the circuits of the assert nodes that use the signals as the targets. Section 3.8 gives a simple example to explain the relationship between signal circuits and assert node circuits.

For a signal that has the type array n of T, the circuit representation of each element in the array should be generated. The identifiers of the gates named *assert*, the

# (a) Active\_True Local Signal Circuit

(b) Active\_False Local Signal Circuit

(c) Active\_True Global Signal Circuit

(d) Active\_False Global Signal Circuit

Figure 3.8: The Signal Circuits

input wires named assert\_global\_s, and the output wires named s shown in Figure 3.8 are added to the wire table when the circuit of each signal named s is created.

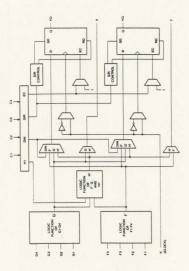

#### 3.5.2 Generating Register Circuits

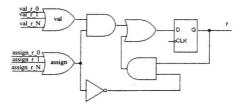

The circuits of the registers in the requirements table are generated in Figure 3.9. The D-type flip-flops are used in the circuits for the registers to store information. The value of a register is the latest value assigned to it in a previous clock period. For each local register named r, as shown in Figure 3.9(a), its transformation is composed of three orgates, two and-gates, a not-gate, a D-type flip-flop, and several wires. In Figure 3.9(b), additional input wires named val\_global\_r and assign\_global\_r, a buffer, and a wire named global\_r are needed for each global register named r. The buffer is generated for the same reason as the buffers in Figure 3.8. All flip-flops in the netlist use the same clock line. The clock is designed as a global VHDL signal. Similar to the transformations of the signals, input wires named val\_ $r_0$ , val\_ $r_1$ , val\_ $r_2$ , N assign\_ $r_0$ , assign\_ $r_1$ , and assign\_ $r_2$  we not generated here and only shown for illustrative purpose. They are the output wires named val\_*farget* and assign\_*Target* produced in the circuits of the assignment nodes that use the register as the target (see Figure 3.13).

The transformation of a register that has the type array n of T is similar to the transformation of the signal that represents an array. As shown in Figure 3.9, the identifiers of the two input or-gates named val and assign, the input wires named val\_global\_r and assign\_global\_r, and the output wire named r are updated to the wire table when the circuit of each register named r is created.

(b) Global Register Circuit

Figure 3.9: The Register Circuits

## 3.6 A Module for Generating Node Circuits

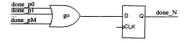

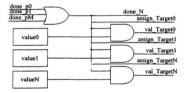

This module generates the circuits of all the nodes in the ASM chart. Each node is labelled. Labels come in five varieties: dummy nodes, state nodes, assert nodes, assignment nodes, conditional nodes. The function named genOneVdCircuit generates the circuit for one node. When the circuits are generated for dummy nodes, state nodes, assert nodes, and assignment nodes, the identifiers of the input or-gate named go and the output wire named done\_N are kept in the wire table. For condition nodes, the identifiers of the input or-gate named go and the two output wires named done\_N\_then and done N else and two nodes named *thenNode* and *elseNode* are stored in the wire table.

The dummy nodes are place-holders. The control flow goes directly through these nodes. The circuit of a dummy node simply consists of an or-gate and an output wire, as shown in Figure 3.10. The wires named done\_p0, done\_p1, and done\_pM are not generated here and they are from the output wires that are produced in the circuits of the predecessor nodes. The same goes for all node types.

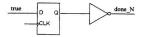

The state nodes represent the control state of the program. They are used to wait for the coming of the next clock period. The first node listed in the ASM chart is always a state node and represents the start of the program. As shown in Figure 3.11(a), its circuit is composed of a D-type flip-flop, an inverter, and three wires. The input wire is a true wire. It is required that the output wire should be true in the first clock period in order to start the program. Figure 3.11(b) gives the circuit generated for a state node numbered N.

Figure 3.10: The Dummy Node Circuit

(a) The Initial State Node Circuit

(b) The Circuit of the State Node Numbered N

Figure 3.11: The State Node Circuits

The assert nodes are used to transfer information to signals. In the ASM chart, assert nodes are labelled with two expressions; target and value. The target expression represents the left-hand-side of an assert statement and will be a signal. The value expression indicates the right-hand-side of an assert statement and will be one of seven kinds of expressions described in the next section. Figure 3.12 gives the assert node circuits. Before generating the assert node circuits, the circuits of the two expressions are created. In Figure 3.12, the value expression circuits are represented by a box labelled value or by several boxes labelled value0, value1, ..., valueN in the case of an array target. As mentioned in generating signal and register circuits module, the output wire named assert Target in Figure 3.12(a) will be the input of the or-gate in the circuit for the target signal of the assert node. The assert Target output in Figure 3.12(b) will be the input of the and-gate in the circuit for the target signal of the assert node. The circuit in Figure 3.12(c) is generated for an assert node whose value expression is an array expression and whose target expression is an active-true array signal. The output wires named assert Target0, assert Target1, ..., assert TargetN will be inputs to several orgates in the circuit for the target signal of the assert node. Asserting an active-false array signal circuit is not shown. It can be obtained according to Figure 3.12(b).

The assignment nodes are used to store information in registers. Similar to assert nodes, each assignment node is associated with a target expression and a value expression. The target expression represents the left-hand-side of an assignment statement and will be a register. The value expression indicates the right-hand-side of an assignment statement and will be one of seven kinds of expressions described in the next

(a) Asserting an Active-True Signal Circuit

(b) Asserting an Active-False Signal Circuit

(c) Asserting an Active-True Array Signal Circuit

Figure 3.12: The Assert Node Circuits

section. The circuits shown in Figure 3.13 are used to represent the assignment nodes. Figure 3.13(a) represents an assignment node whose target expression is a bool type register. The box labelled *value* represents the circuit of the value expression of the assignment node. The wires named assign\_*Target* and val\_*Target* are the input wires of the or-gates named *assign* and *val* in the target register circuit, respectively. The wire named done\_N of this node circuit will be the input wire of the or-gate in its successor node. The circuit shown in Figure 3.13(b) is generated for an assignment node that has an array type register and an array expression. Each of the boxes that are labelled *value0*, *value1*, ..., *valueN* represents a value output wire of the array expression. Each of the output wires named val\_*Target0*, val\_*Target1*, ..., val\_*TargetN* will be the input wire of an or-gate named val in the target register circuit. The wires named assign\_*Target0*, assign\_*Target1*, ..., assign\_*TargetN* will be the input wires of the several or-gates named *assign\_Target1*, ..., assign\_*TargetN* will be the input wires of the several or-gates named *assign the target register* circuit.

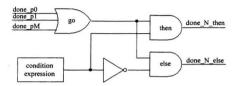

The condition nodes have associated a condition expression that will be true or false and two nodes called *thenNode* and *elseNode*. When the expression is true, the node named *thenNode* will be executed; when the expression is false, the node named *elseNode* will be executed. The circuit for each condition node is generated as shown in Figure 3.14. It is composed of an or-gate named *go*, two and-gates named *then* and *else*, an inverter, a box and several wires. The inverter is used to implement the choice of the control flow. In Figure 3.14, the box labelled *condition expression* represents the expression circuit of the condition node circuit. The output wire named done\_N\_then in the condition node circuit will be the input wire of the *go* gate of the node named

(b) Assigning an Array Register Circuit

Figure 3.13: The Assignment Node Circuits

thenNode. The output wire named done\_N\_else in the condition node circuit will be the input wire of the go gate of the node named elseNode.

Figure 3.14: The Condition Node Circuit

# 3.7 A Module for Generating Expression Circuits

This module will transform all expressions that are associated with assert nodes, assignment nodes, and condition nodes into their corresponding circuits. When generating the circuits of these nodes, the expressions will be transformed into their circuit representations as a part of these node circuits. In the SMALL language, there are seven kinds of expressions: identifier expressions, constant expressions, unary expressions, binary expressions, subscript expressions, subarray expressions and array building expressions. Each expression is transformed into a circuit with the value outputs for the value of the expression and an overflow output that indicates whether overflow occurred in the calculation of the value output. When adding or subtracting two's complement numbers and if the result is too large or too small to be represented in the specified range, we say that "overflow" occurs. The function named genExpCircuits is defined to implement the transformation. Its input parameter is the expression containing the type and the location and other information. Its outputs are wires representing the value outputs and the overflow output. For each kind of expression, the following gives its circuit representation.

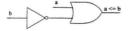

The constant expression, true, is implemented by a true wire as the output value and a false wire as the overflow output. The constant expression, false, is implemented by a false wire as the output value and a false wire as the overflow output.

An identifier expression is a string referring to a signal or a register in the requirements table. The output value of the identifier expression referring to a bool type signal or register is the output named s or r of its signal or register circuit. The false wire is used to express the fact that no overflow occurs in generating the identifier expression circuit. In the case of the identifier referring to an array type signal or register, the output values will be a list of the outputs of every element in the array. The overflow output will be false wire.

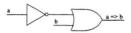

A unary expression consists of an expression and an operator that is one of not, -, and overflow. The not expression is implemented by an inverter as shown in Figure 3.15(a). The overflow expression will be true if there is overflow in the evaluation of its operands. The overflow output is the disjunction of all overflow outputs of the operands. The same goes for other expressions that have no specific explanation of overflow. The expression -*B* distributes to the array of boolean level and is two's complement negation. A ripple carry negater should be used for its implementation. For convenience, this thesis uses a ripple carry adder and inverters instead. The circuit will be discussed in array operations.

A binary expression contains two expressions and one operator that is one of &, or, =>. <=, ==, =/=, =, /=, ++, plus, -, and uplus. The former six operators and the not operator distribute to the bit level. Their meanings are given in (Norvell, 1998). Their expressions are implemented by the circuits shown in Figure 3.15. It is noted that the inputs in Figure 3.15 are the value outputs of the operands. The operators, = and /=, are used to compare two expressions. If the value outputs of the two expressions have the same value, the expression "A = B" will have a true result; otherwise, the expression "A /= B" will have a true result. Similar to the negation operator, the operators such as ++, plus. -, and uplus distribute to the array of boolean level. The function named distributelbM is defined to implement these operations for one dimensional or multidimensional array operands. Because the results of multi-dimensional array operands can be obtained by applying these operators to the one-dimensional arrays, the following simply describes the definitions and the circuit implementations of these operators on one-dimensional arrays. Detailed definitions on these operators can be found in (Norvell, 1996 and 1998).

The expression,  $A \leftrightarrow B$ , implements the catenation of two arrays. A function named catM is defined to generate circuits for this operation. The value outputs of the expression

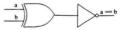

(a) Expression "not a" Circuit

(b) Expression "a & b" Circuit

(d) Expression "a => b" Circuit

(f) Expression "a == b" Circuit

(g) Expression "a =/= b" Circuit

Figure 3.15: The Expression Circuits

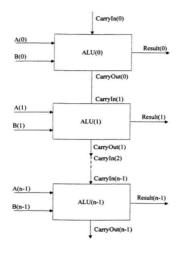

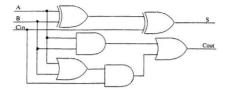

consist of the value outputs of the expression A as the start and the value outputs of the expression B as the end. The expression A uplus B implements the unsigned addition of two numbers. The result length is one more than the length of the longer of A and B. No overflow occurs in the above two operations. However, if there is overflow in evaluating A or B, the overflow outputs of the above two expressions are true. The expression, A plus B, carries out the two's complement addition of two numbers. The binary expression, A - B, implements the two's complement subtraction of two numbers. Functions named uplusM, plusM, and minusM are defined to generate circuits for these operations. The unary expression, - B, is used for the two's complement negation of a number. A function named minusM is defined for the expression that is the same as [false, false, ..., false] - B. A ripple carry adder shown in Figure 3.16 is generated for the circuits of the expressions with uplus and plus operators. A function named genAdder is defined to generate circuits for the ripple carry adder. In Figure 3.16, each box represents the circuit shown in Figure 3.17 and generated for a full adder. The following logic equations for the full adder are described in (Lenk, 1972).

$$S = A\overline{B}\overline{C}_{in} + \overline{A}\overline{B}\overline{C}_{in} + \overline{A}\overline{B}C_{in} + ABC_{in}$$

=  $A \oplus B \oplus C_{in}$

$C_{out} = AB + (A + B)C_{in}$

In the above equations, A and B and  $C_{int}$  are the inputs; S and  $C_{out}$  represent the outputs for the sum and the carry;  $C_{int}$  is 0 for the addition of the least significant bits.

For operations with - B and A - B, a ripple carry subtracter should be used. However, for the convenience, this thesis uses a ripple carry adder and inverters to implement the

Figure 3.16: A Ripple Carry Adder Circuit

operations. Before using the function named genAdder, we implement the operation with not for every element in B and set the initial carry named CarryIn0 to 1 to make the adder perform subtraction.

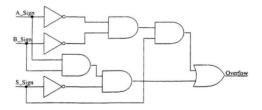

The overflow output for the operation with uplus is false. Figure 3.18 shows the overflow output circuit for the operation with plus. In Figure 3.18,  $A_S$  sign and  $B_S$  sign are the sign bits of the two operands;  $S_S$  sign is the sign bit of the sum; Overflow represents whether overflow occurs. The logic equation for Figure 3.18 is as follows:

Figure 3.18 is also used to generate the overflow output circuit for the expression A-Band the expression -B; however, the inverters should be used for the expression B. The logic equation is changed to the following form.

$$Overflow = S$$

Sign A Sign B Sign + S Sign A Sign B Sign

An array building expression is a list of expressions. The value outputs of the array building expression are a bundle of the value outputs of the expressions. An or-gate is used for disjoining all overflow outputs of the expressions in the array to get the overflow output of the array building expression.

A subscripted array expression contains an expression as an operand and a constant number as the subscript. The value output of the subscripted array expression is selected from the value outputs of the operand in terms of the constant number. The overflow output of the operand is the overflow output of the subscripted array expression.

Figure 3.17: A Full Adder Circuit

Figure 3.18: The Overflow Output Circuit for Operators: "plus" and -

A subarray expression is composed of an expression as an operand and two constant numbers as the length and as the starting subscript. The value outputs of the subarray expression are a subsequence of the value outputs of the operand in terms of the two constant numbers. The overflow output of the subarray expression is the same as the overflow output of the operand.

## 3.8 A Module for Connecting Node Circuits

This module links all the node circuits in terms of the edges in the ASM chart and the information from the wire table. The function named *connectNode* is defined in this module. The output wire named done\_N of each node except for a condition node will be connected to every or-gate named go of its successor node. In the case of a condition node, the output wire named done\_N\_then will be linked to the go gate of its *thenNode* node and the output wire named done\_N\_else will be connected to the go gate of its *elseNode* node. Once the nodes are connected, the netlist is complete.

A simple SMALL example shown in Figure 3.19 is used to illustrate how to generate the circuits of signals and assert nodes and how to connect these circuits. Figure 3.20 gives an ASM chart for the SMALL program shown in Figure 3.19. Each node shown in Figure 3.20 is transformed into its corresponding circuit as shown in Figure 3.21. For example, the flip-flop labelled 1 and the inverter labelled 1 represent Node 0 and the orgate labelled gol is generated to represent Node 1, a dummy node. In Figure 3.20, the done\_N wire of each node is also labelled in Figure 3.21. According to the *done\_N* wires, all the node circuits are connected to represent the circuit of the SMALL program shown

| global sig a: bool | //0 |

|--------------------|-----|

| while true do      | //1 |

| a ! true           | //2 |

| tick               | //3 |

| a ! false          | //4 |

| tick               | //5 |

| a ! true           | //6 |

| od                 | //7 |

Figure 3.19: A Simple SMALL Program