# Hardware Implementation of Pipelined Statistical Cipher Feedback Mode

By

#### © Yuanchi Tian

A thesis submitted to the School of Graduate Studies in partial fulfillment of the requirements for the degree of Master of Engineering

# Department of Electrical and Computer Engineering Faculty of Engineering and Applied Science

Memorial University of Newfoundland

October 2015

St. John's

Newfoundland and Labrador

### Abstract

Pipelined statistical cipher feedback (PSCFB) mode is a new mode of operation for block cipher encryption. It is an improved version of conventional SCFB mode with higher throughput. SCFB mode has the mechanism of self-synchronization to recover from bit slips during transmission in a communication channel. To improve the throughput, PSCFB is a modified version of SCFB that combines Counter mode and Cipher Feedback (CFB) mode and allows for the pipelining of the underlying block cipher while still preserving the efficiency and self-synchronizing capabilities.

In this thesis, the hardware architecture of PSCFB mode is presented, resulting in a fully implemented PSCFB encryption/decryption system for the first time. No previous implementations of PSCFB has achieved maximum data width and high throughput. In this thesis, several PSCFB system implementations with different size and input/output rate are investigated. The Advanced Encryption Standard (AES) with a pipeline architecture is used as the block cipher in PSCFB. The PSCFB system is designed, simulated and synthesized targeted to an Altera

Cyclone IV FPGA and TSMC 180 nm CMOS process. System performance is analyzed. The PSCFB encryption and decryption systems can reach throughputs of 10 Gbps in FPGA and 23 Gbps in CMOS, which is suitable for high speed optical larger communication like SONET/SDH. This PSCFB system reaches the theoretical maximum data width, thus achieving maximum efficiency. Not only is the system designed to work in high frequency, but also optimized to reduce area cost. Compared with pipelined AES, which is the block cipher, the PSCFB system itself only costs about 20% of the combinational logic functions and 55% of the registers in the FPGA, and costs about 20% of the total equivalent gate count in CMOS.

### Acknowledgements

This thesis would not have been possible without my supervisor, Dr. Howard Heys. I would like to express my sincere gratitude for his patience, motivation and encouragement. He guided me in all my research at Memorial University. During the past two years, Dr. Heys helped me in cryptography and let me to continue to work on his idea. He shaped the material contained herein, including papers presented in NECEC and CCECE.

Besides my supervisor, I am also grateful to Dr. Cheng Li and Dr. Lihong Zhang, who have taught me in Advanced Digital Systems and ASIC Design course. The knowledge from these courses helped me finish this thesis.

I would like to thank CMC for the support of CAD tools and design kits.

My sincere thanks also goes to my family members, colleagues and friends for supporting me all the time.

# Contents

| Abstract                                        | ii  |

|-------------------------------------------------|-----|

| Acknowledgements                                | iv  |

| Contents                                        | V   |

| List of Tables                                  | X   |

| List of Figures                                 | xii |

| Lists of Symbols, Nomenclature or Abbreviations | xv  |

| Chapter 1 Introduction                          | 1   |

| 1.1 Motivation                                  | 3   |

| 1.2 Thesis Outline                              | 5   |

| Chapter 2 Background                            | 7   |

| 2.1 Symmetric Key Ciphers                       | 7   |

| 2.2 Block Ciphers and Stream Ciphers            | 8   |

| 2.3 Advanced Encryption Standard (AES)          | 10  |

|   | 2.3.1 SubBytes                                       | 12 |

|---|------------------------------------------------------|----|

|   | 2.3.2 ShiftRows                                      | 13 |

|   | 2.3.3 MixColumns                                     | 13 |

|   | 2.3.4 AddRoundKey                                    | 14 |

|   | 2.3.5 Key Expansion                                  | 15 |

| 2 | .4 Conventional Modes of Operation                   | 16 |

|   | 2.4.1 Electronic Codebook (ECB) Mode                 | 16 |

|   | 2.4.2 Cipher Block Chaining (CBC) Mode               | 18 |

|   | 2.4.3 Cipher Feedback (CFB) Mode                     | 19 |

|   | 2.4.4 Output Feedback (OFB) Mode                     | 21 |

|   | 2.4.5 Counter (CTR) Mode                             | 23 |

| 2 | .5 Statistical Self-Synchronization                  | 25 |

|   | 2.5.1 Statistical Cipher Feedback (SCFB) Mode        | 25 |

|   | 2.5.2 SCFB Mode with Counter Mode                    | 28 |

|   | 2.5.3 PSCFB Mode                                     | 28 |

| 2 | .6 Target Technologies                               | 31 |

|   | 2.6.1 Application-Specific Integrated Circuit (ASIC) | 31 |

|   | 2.6.2 Field-Programmable Gate Array (FPGA)           | 32 |

|   | 2.6.3 ASIC vs. FPGA                                  | 32 |

|   | 2.7 Previous Work of PSCFB                                           | 34 |

|---|----------------------------------------------------------------------|----|

|   | 2.8 Summary                                                          | 35 |

| C | Chapter 3 Pipelined AES                                              | 36 |

|   | 3.1 Basic Architecture Without Pipelining                            | 36 |

|   | 3.2 Loop Unrolling                                                   | 38 |

|   | 3.3 Pipelining                                                       | 39 |

|   | 3.3.1 Outer-Round Pipelining                                         | 39 |

|   | 3.3.2 Inner-Round Pipelining                                         | 41 |

|   | 3.4 Pipelined AES in PSCFB                                           | 42 |

|   | 3.5 Modified Blackout Period                                         | 45 |

|   | 3.6 Summary                                                          | 45 |

| C | Chapter 4 Design of PSCFB                                            | 46 |

|   | 4.1 Design Considerations                                            | 46 |

|   | 4.2 Overall Structure                                                | 49 |

|   | 4.3 Plaintext and Ciphertext Queue                                   | 51 |

|   | 4.3.1 Design 1: Basic Structure With Reduced Hardware Resource Usage | 52 |

|   | 4.3.1.1 Plaintext Queue: A Small Scale Example                       | 53 |

|   | 4.3.1.2 Design Considerations for Full Scale System                  | 57 |

|   | 4.3.1.3 Ciphertext Queue: A Small Scale Example                      | 58 |

| 4.3.2 Variable Width Transmission Between Two Queues                    | 60   |

|-------------------------------------------------------------------------|------|

| 4.3.3 Design 2: An Updated Version of Queues                            | 61   |

| 4.3.4 Design 3: A Further Improved Ciphertext Queue With Barrel Shifter | :.64 |

| 4.3.4.1 Barrel Shifter in Ciphertext Queue                              | 64   |

| 4.3.4.2 A Small Scale Example                                           | 66   |

| 4.3.4.3 Design Considerations for Full Scale System                     | 67   |

| 4.3.5 Pointer Calculator                                                | 68   |

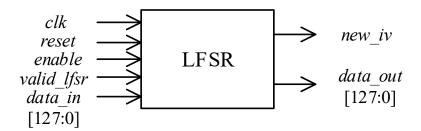

| 4.4 Counter (LFSR)                                                      | 70   |

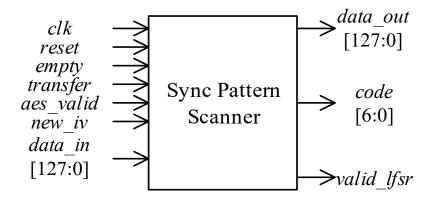

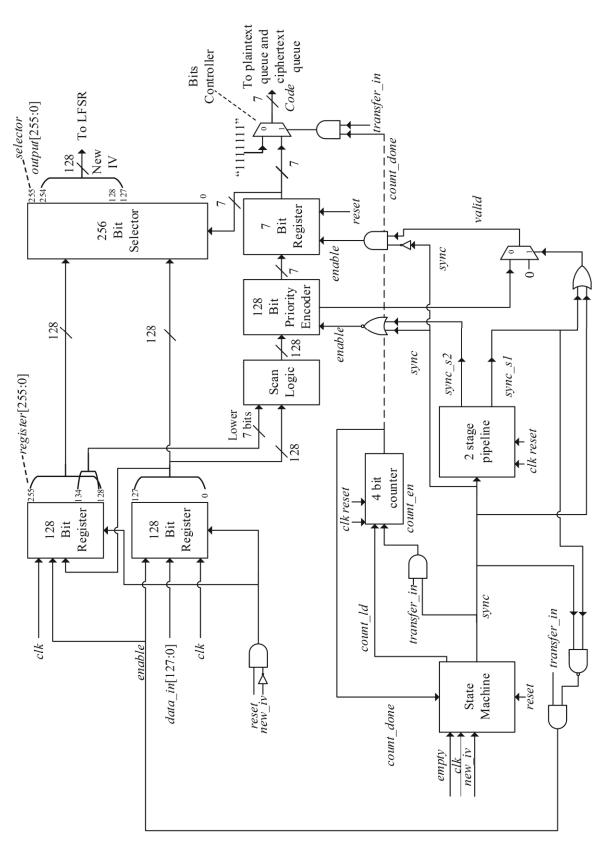

| 4.5 Sync Pattern Scanner                                                | 72   |

| 4.5.1 Structure                                                         | 72   |

| 4.5.2 Control Unit                                                      | 78   |

| 4.6 Barrel Shifters                                                     | 86   |

| 4.7 Summary                                                             | 90   |

| Chapter 5 Implementation and Analysis                                   | 91   |

| 5.1 System 1A                                                           | 94   |

| 5.2 System 1B                                                           | 98   |

| 5.3 System 2                                                            | 100  |

| 5.4 System 3                                                            | 101  |

| 5.5 Summary                                                             | 104  |

| Chapter 6 Conclusions                                         | 105 |

|---------------------------------------------------------------|-----|

| References                                                    | 107 |

| Appendix A Some codes of PSCFB Systems                        | 111 |

| A.1 Sync Pattern Scanner                                      | 111 |

| A.2 State Machine of Sync Pattern Scanner                     | 126 |

| Appendix B Combinations of $M$ and $D$ Satisfying Constraints | 133 |

### List of Tables

| Table 2-1 AES Round Constants                             |

|-----------------------------------------------------------|

| Table 4-1 Cases in Data Transmission for Plaintext Queue  |

| Table 4-2 Cases in Data Transmission for Ciphertext Queue |

| Table 4-3 Truth Table of XNOR Gate76                      |

| Table 5-1 $M$ and $D$ Satisfying Constraints              |

| Table 5-2 Implementations with Different Parameters93     |

| Table 5-3 Address Decoding and Mapping95                  |

| Table 5-4 Resource Usage of System 1A on FPGA96           |

| Table 5-5 Performance of System 1A on FPGA97              |

| Table 5-6 Resource Usage of System 1B on FPGA99           |

| Table 5-7 Performance of System 1B on FPGA99              |

| Table 5-8 Resource Usage of System 2 on FPGA              |

| Table 5-9 Performance of System 2 on FPGA                 |

| Table 5-10 Area Report of System 3 on CMOS 180 nm         |

| Table 5-11 System Area on CMOS 180 nm (D=116, M=580)      |

| 1 abic 5 12 by heliobib 1 cobair in [25] | Table 5-12 Synthesis Result in | [25] |  | 10 | 3 |

|------------------------------------------|--------------------------------|------|--|----|---|

|------------------------------------------|--------------------------------|------|--|----|---|

# List of Figures

| Figure 2-1 Symmetric Key Cipher                        | 8  |

|--------------------------------------------------------|----|

| Figure 2-2 Block Cipher                                | 9  |

| Figure 2-3 Stream Cipher                               | 10 |

| Figure 2-4 AES-128 Encryption Process                  | 11 |

| Figure 2-5 AES State Array                             | 12 |

| Figure 2-6 AES S-box                                   | 13 |

| Figure 2-7 AES Key Expansion                           | 16 |

| Figure 2-8 Electronic Code (ECB) Mode                  | 17 |

| Figure 2-9 Cipher Block Chaining (CBC) Mode            | 18 |

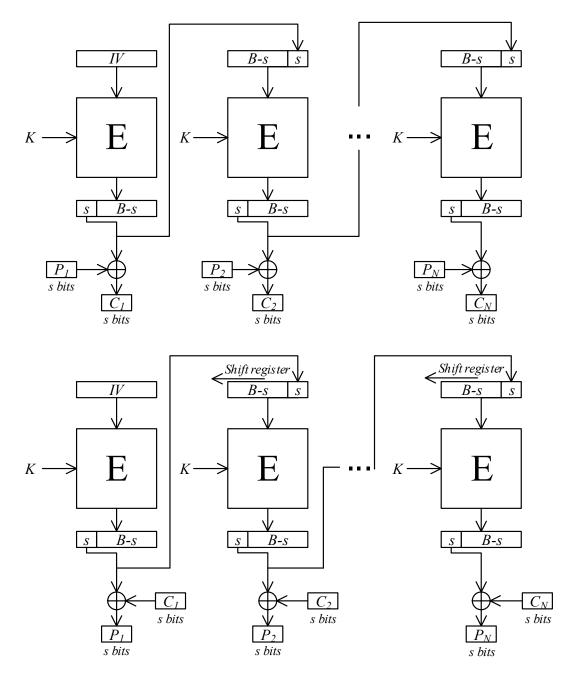

| Figure 2-10 Cipher Feedback (CFB) Mode                 | 20 |

| Figure 2-11 Output Feedback (OFB) Mode                 | 22 |

| Figure 2-12 Counter (CTR) Mode                         | 24 |

| Figure 2-13 SCFB Synchronization Cycle                 | 26 |

| Figure 2-14 Architecture of SCFB Mode                  | 27 |

| Figure 2-15 SCFB Synchronization Cycle Based on Blocks | 27 |

| Figure 2-16 Architecture of SCFB Mode with Counter      | 28 |

|---------------------------------------------------------|----|

| Figure 2-17 PSCFB Synchronization Cycle                 | 29 |

| Figure 2-18 PSCFB Synchronization Cycle Based on Blocks | 30 |

| Figure 3-1 Basic Iterative Architecture                 | 37 |

| Figure 3-2 Loop Unrolling                               | 38 |

| Figure 3-3 Outer-round Pipelining                       | 40 |

| Figure 3-4 Inner-round Pipelining                       | 42 |

| Figure 3-5 Pipelined AES in PSCFB                       | 43 |

| Figure 3-6 Register Insertion                           | 44 |

| Figure 4-1 Architecture of PSCFB Encryption [4]         | 47 |

| Figure 4-2 Structure of Encryption System (Datapath)    | 50 |

| Figure 4-3 Structure of Decryption System (Datapath)    | 50 |

| Figure 4-4 I/O Diagram of Queueing System               | 52 |

| Figure 4-5 General FIFO                                 | 53 |

| Figure 4-6 Reading and Writing Process in PSCFB         | 54 |

| Figure 4-7 3-bit 2-to-1 Multiplexer                     | 55 |

| Figure 4-8 Architecture of Plaintext Queue              | 56 |

| Figure 4-9 Multiplexer (Gate Level)                     | 57 |

| Figure 4-10 Demultiplexer (Gate Level)                  | 57 |

| Figure 4-11 Architecture of Ciphertext Queue            | 59 |

| Figure 4-12 Updated Version of Plaintext Queue          | 62 |

| Figure 4-13 Updated Version of Ciphertext Queue         | 63 |

| Figure 4-14 Left Shift Barrel Shifter65                                          |

|----------------------------------------------------------------------------------|

| Figure 4-15 Right Shift Barrel Shifter65                                         |

| Figure 4-16 Improved Ciphertext Queue with Barrel Shifter                        |

| Figure 4-17 I/O Diagram of LFSR71                                                |

| Figure 4-18 I/O Diagram of Sync Pattern Scanner                                  |

| Figure 4-19 Architecture of Sync Pattern Scanner                                 |

| Figure 4-20 Data Reading from Registers                                          |

| Figure 4-21 Single Scan Logic Part (Fixed)                                       |

| Figure 4-22 Single Scan Logic Part (General Purpose)                             |

| Figure 4-23 I/O Diagram of 128 bit Priority Encoder                              |

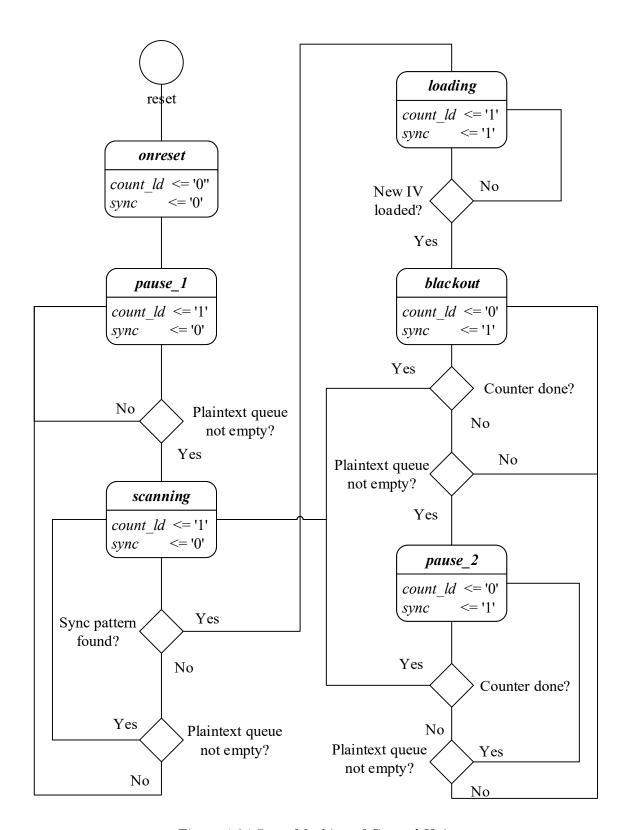

| Figure 4-24 State Machine of Control Unit                                        |

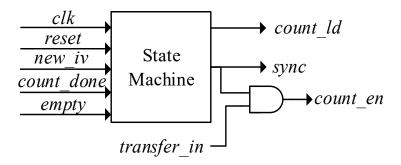

| Figure 4-25 I/O Diagram of Control Unit80                                        |

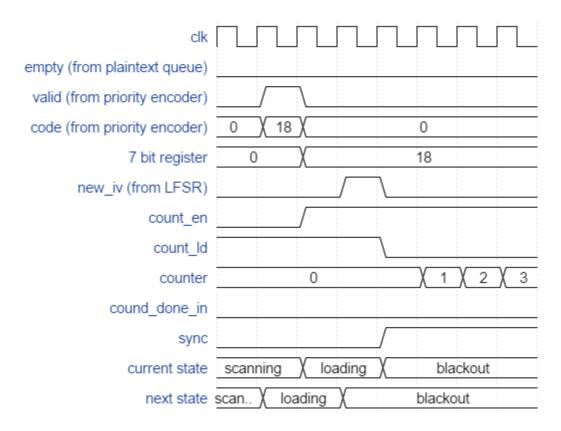

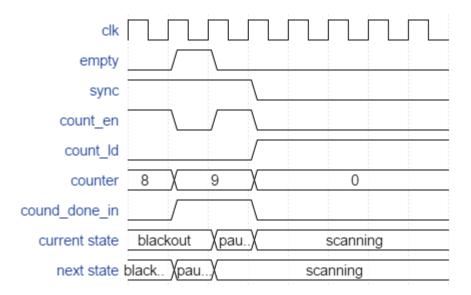

| Figure 4-26 Timing Diagram for Loading State83                                   |

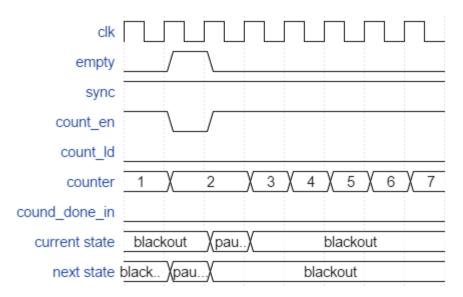

| Figure 4-27 Pause in Blackout Period85                                           |

| Figure 4-28 Pause at the Last Block in Blackout Period                           |

| Figure 4-29 Barrel Shifter in PSCFB Encryption System87                          |

| Figure 4-30 Barrel Shifter in PSCFB Decryption System87                          |

| Figure 4-31 Right Shift Barrel Shifter in PSCFB                                  |

| Figure 4-32 Alternative Option to Place Barrel Shifters in Encryption System89   |

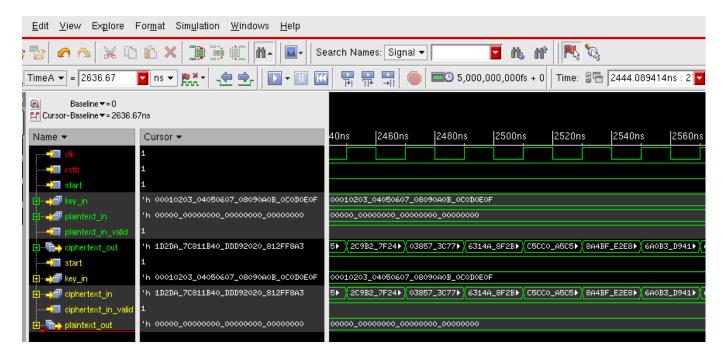

| Figure 5-1 Timing Diagram of Testing Encryption and Decryption Systems93         |

| Figure 5-2 First Four Layers of Cascading Demultiplexers in Ciphertext Queue. 95 |

# Lists of Symbols, Nomenclature or

### **Abbreviations**

ASIC

CBC

| Κ                             | The number of bits in the secret key.                              |

|-------------------------------|--------------------------------------------------------------------|

| B                             | The length of a block                                              |

| D                             | The data rate between PSCFB system and others devices              |

| d                             | The transmission rate between plaintext queue and ciphertext queue |

| L                             | The number of pipeline stages                                      |

| R                             | The final round number of AES                                      |

| s                             | The number of feedback bits in CFB and OFB                         |

| D(K, Y)                       | Decryption of ciphertext $Y$ using secret key $K$                  |

| E(K,X)                        | Encryption of plaintext $X$ using secret key $K$                   |

| $\mathrm{GF}(2^{\mathrm{n}})$ | The finite field of order $2^n$                                    |

| AES                           | Advanced Encryption Standard                                       |

|                               |                                                                    |

Application-Specific Integrated Circuit

Cipher Block Chaining

CFB Cipher Feedback

CMC Canadian Microelectronics Corporation

CMOS Complementary Metal-Oxide-Semiconductor

CTR Counter

DC Design Compiler

DES Data Encryption Standard

ECB Electronic Code Book

FIFO First In, First Out

FPGA Field-programmable Gate Array

IV Initialization Vector

KSG Key Stream Generator

LUT Lookup Table

NAND Negative-AND

NIST National Institute of Standards and Technology

NRE Non-Recurring Engineering

OFB Output Feedback

PSCFB Pipelined Statistical Cipher Feedback

SCFB Statistical Cipher Feedback

TSMC Taiwan Semiconductor Manufacturing Company

VHDL Very High Speed Integrated Circuit Hardware Description Language

XOR Exclusive OR

### Chapter 1

### Introduction

Cryptography is widely applied in software and hardware so as to provide security. In the modern age, data security sometimes matters more than data itself. Important information has to be kept safe without letting others know about it. It is the fact that there are always people who want to steal the secret information from others and make profit. In the domains of business, politics and the military, information leakage will cause serious consequences. Based on this, important information should not only be kept in a safe place, but also be encrypted. Encryption is one of the many ways to keep information secure. During the Second World War, some cipher machines were invented to encrypt and decrypt messages. Cryptography was applied on radio transmission during the war, because radio frequencies can be received by anyone with a radio receiver.

There are five concepts describing security objectives: confidentiality, integrity, availability, authenticity and accountability [1]. Confidentiality is the process of

preserving private information from being seen by unauthorized people. Integrity means the content of information is correct, so that if someone is able to maliciously modify the information, this is detected. Availability is the property that allows important information to be accessed without any denial. Authenticity ensures the validity of user's identity and the data source of information received. Accountability means every user in the system has the responsibility for every single action they take. With the complexity resulting from the need for all five security objectives, it is often not easy to establish a secure system.

The action of attempting to acquire the unauthorized information can be regarded as a security attack. There are two general categories of attacks: passive attack and active attack [1]. In a passive attack a third party can acquire the message in transmission, or even find the pattern of the encrypted message. An active attack contains actions like pretending to be an authorized person, receiving the message and then sending it to the original receiver. The message content may be modified in an active attack. The attacker could also stop the network service by attacking the server.

In cryptography, a symmetric key cipher is the cryptographic system where encryption and decryption use the same secret key. The plaintext is the original message and the ciphertext is the encrypted message. In a block cipher, the encryption or decryption system operates on a single block of data, which contains a fixed number of bits. Different from the block cipher, a stream cipher encrypts only one bit at a time. It generates the key stream, which is to be XORed with the

incoming plaintext stream. Although block ciphers encrypt a whole block of data, modes of operation are defined as various ways for encryption with the same block cipher.

There are some special requirements for modes of operation. Based on the natural characteristic of the communication channel, one or more bits may be lost during transmission, so that the decryption process will be affected and the message cannot be successfully recovered. Hence, a cipher system with self-synchronization is needed to solve the problem. A successful system is able to automatically self-synchronize frequently on both encryption and decryption. Even if the bit slip occurs in ciphertext during transmission, only one or several blocks of data are affected before next self-synchronization and it will not have influence on further blocks.

As a solution to the problem discussed above, the Statistical Cipher Feedback (SCFB) mode [2] is proposed. SCFB mode scans the ciphertext for a specific bit pattern and regards it as a sign of self-synchronizing. The mechanism of SCFB mode resembles a combination of output feedback (OFB) mode and cipher feedback (CFB) mode. However, it has self-synchronization that OFB mode does not and has higher efficiency than CFB mode.

#### 1.1 Motivation

In the context of a passive attack, an insecure communication channel will allow a message to be eavesdropped. One such insecure channel might be in an optical network using the protocol of Synchronous Optical Networking (SONET) and Synchronous Digital Hierarchy (SDH). Such network channels can reach 40 Gbit/s or even 100 Gbit/s speed. Providing security to transmission lines with such a high speed is a challenge. Our goal is to provide communication security in physical layer of high speed networks.

In our work, we investigate the hardware implementation of Pipelined Statistical Cipher Feedback (PSCFB), a high speed, self-synchronizing cipher mode. PSCFB is based on SCFB mode, which is designed to effectively achieve self-synchronization. Hence, with high speed and self-synchronization, PSCFB mode can be applied to high speed SONET/SDH to provide security.

In an SCFB system, a well-known block cipher, the Advanced Encryption Standard (AES) [3] would be typically used. AES has a 128, 192 or 256-bit key, which provides high security. Since AES has at least 10 rounds of operations to encrypt/decrypt one block of data, it takes a long time to generate desired output. In order to be efficiently implemented in hardware, pipelining can be used in a block cipher. To make changes for block ciphers with pipelining architecture, SCFB mode is modified and a new mode, the Pipelined Statistical Cipher Feedback (PSCFB) mode [4], was recently proposed. In [4], the structure and algorithm of PSCFB is explained. It is simulated for performance analysis and security is also investigated.

In this thesis, PSCFB mode hardware implementation will be discussed and analyzed. In particular, the digital hardware design and implementation will be

presented. Simulation and synthesis are conducted in FPGA and CMOS environments.

#### 1.2 Thesis Outline

The thesis organization is as follows.

Chapter 2 is the cryptography background. Basic knowledge of cryptography is introduced, including block ciphers and stream ciphers. Some well-known modes of operation will also be introduced. As the most applied block cipher today, the Advanced Encryption Standard (AES) [3] is the major algorithm in this chapter. Statistical Cipher Feedback (SCFB) mode [2] and Pipelined Statistical Cipher Feedback (PSCFB) mode [4] are the focus of this thesis and are also introduced in Chapter 2.

Chapter 3 describes the detail of pipelining architecture of block ciphers and the implementation of pipelined AES in a PSCFB system.

Chapter 4 describes the hardware design of a PSCFB mode. The architecture of PSCFB must meet the requirement of high speed, low latency and capability of self-synchronization. The plaintext queue and ciphertext queue components are two significant aspects of the design which can influence the performance of whole PSCFB system. Another component, the sync pattern scanner is used to search the ciphertext stream for a pattern. A pipelined AES implementation is used in PSCFB to reach high throughput. A Linear Feedback Shift Register (LFSR) is applied to a counter mode configuration for AES.

Chapter 5 discusses the implementation of PSCFB targeted to Altera Cyclone IV FPGA and TSMC 180 nm CMOS process environments. The synthesis result is presented and compared. Based on pipelined AES, there is a small modification to PSCFB mode itself.

Chapter 6 is the conclusion and future work.

### Chapter 2

### Background

In this chapter, some cryptography knowledge is introduced.

### 2.1 Symmetric Key Ciphers

A symmetric key cipher uses the same secret key for both encryption and decryption. In encryption, the plaintext, which is the original data, is processed with the encryption algorithm. The encryption process can be written as

$$Y = E(K, X) \tag{2-1}$$

where X represents the original data or message, E is the encryption function, K is the key and Y is the generated ciphertext. The ciphertext is the unreadable code and it appears to be random.

On the contrary, decryption is the process that ciphertext is converted back to the original plaintext message. It can be written as

$$X = D(K, Y) \tag{2-2}$$

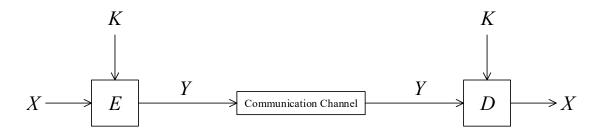

where D is the decryption function. Together, the algorithm to realize the encryption and decryption functions are referred to as a cipher. Figure 2-1 shows the symmetric key cipher with encryption and decryption, where Y' is the received ciphertext and X' is the recovered plaintext.

Figure 2-1 Symmetric Key Cipher

In order to securely apply a symmetric key cipher, a strong algorithm is a must. An attacker may know the algorithm and one or more ciphertexts (and even possibly the corresponding plaintexts), but cannot determine the secure key. Hence, a strong algorithm will stop the opponent, who does not know the key, from decrypting the ciphertext. In addition, since encryption and decryption require the same key, a secure mechanism is necessary to distribute the secret key to both sides.

### 2.2 Block Ciphers and Stream Ciphers

A block cipher operates on a single block of data, which contains a fixed number of bits. Typical block sizes might be 64, 80 or 128 bits. AES and the Data Encryption Standard (DES) [5] are two well-known block ciphers, and they are also symmetric key ciphers. Since the block cipher processes a whole block of data at a

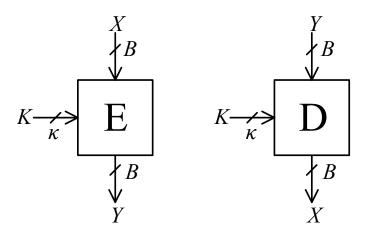

time, the message which is not the multiple of a block size may have to be padded. Figure 2-2 is the diagram of a block cipher with encryption and decryption. Plaintext X and ciphertext Y are both B bits. The key consists of  $\kappa$  bits.

Figure 2-2 Block Cipher

In contrast, a stream cipher operates on a single bit of data. Unlike a block cipher, in a stream cipher, the plaintext bit is usually XORed with a keystream bit to produce a ciphertext bit. The keystream is a pseudorandom sequence, and this is generated using a keyed pseudorandom bit generator. For decryption, in order to recover the plaintext, the keystream must be identical to the encryption keystream, and synchronized so that when a keystream bit is XORed with a ciphertext bit, the correct plaintext bit is produced. A keystream generator should have a long cycle period so that the keystream is not expected to repeat and the pseudorandom keystream should also appear to be similar to a random bit stream. Figure 2-3 is the diagram of a stream cipher. The initialization vector (IV) is used to initialize the keystream generator (KSG). In the encryption part, the keystream is XORed

with incoming the plaintext stream, producing ciphertext Y. Y' is the received ciphertext stream via communication channel and X' is the recovered plaintext.

Figure 2-3 Stream Cipher

### 2.3 Advanced Encryption Standard (AES)

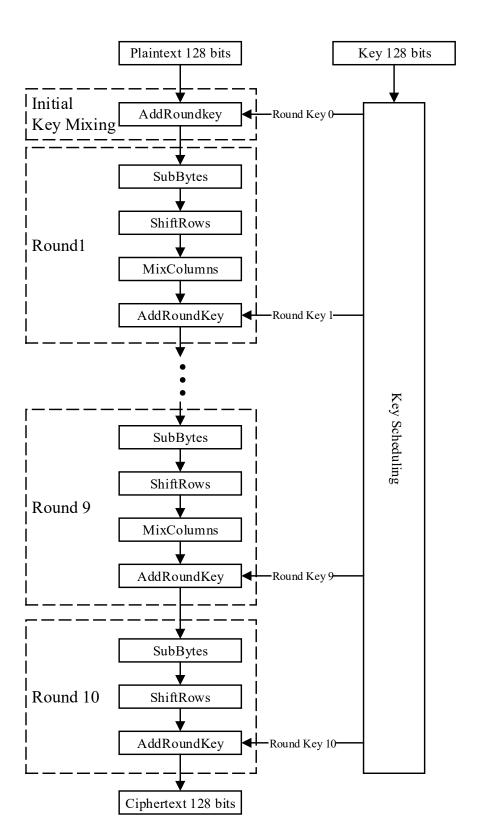

The Advanced Encryption Standard (AES) was been announced by NIST in 2001 [3]. AES is a symmetric key block cipher. It was shown that DES [5] is no longer secure for many applications when it was broken in 1998 [1]. AES was designed to take the place of DES, and now it has been used worldwide. In this section, only AES encryption is described. As for our work, we do not need to use the decryption process.

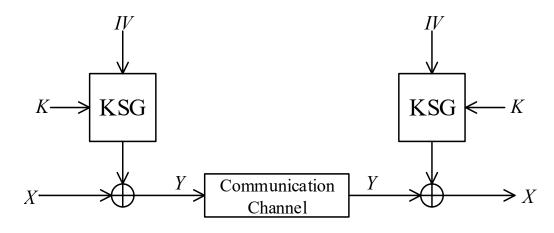

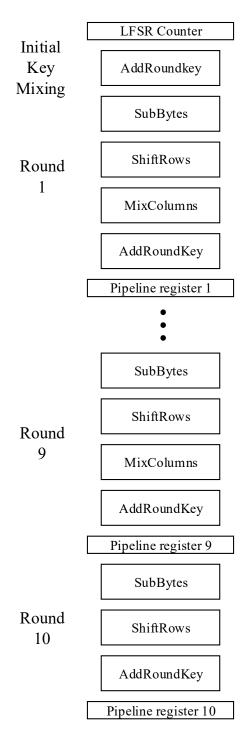

AES can have 128-bit, 192-bit or 256-bit key, with 10, 12 or 14 rounds, respectively. The AES encryption process with 128-bit key and 10-round iteration is referred to as AES-128 and is shown in Figure 2-4. There is an initial key mixing, which uses the first round key. It only contains one transformation, AddRoundKey. Letting R

Figure 2-4 AES-128 Encryption Process

represent the final round number, the first R - 1 rounds (i.e. 9 rounds out of 10 rounds in AES-128) have four transformations, and they are in the same order. These are SubBytes, ShiftRows, MixColumns and AddRoundKey. The final round only has three transformations, which are SubBytes, ShiftRows and AddRoundKey.

| $S_{0,0}$           | $S_{0,1}$           | $S_{0,2}$           | $S_{0,3}$           |

|---------------------|---------------------|---------------------|---------------------|

| $\mathcal{S}_{1,0}$ | $\mathcal{S}_{1,1}$ | $\mathcal{S}_{1,2}$ | $S_{1,3}$           |

| $S_{2,0}$           | $S_{2,1}$           | $S_{2,2}$           | $S_{2,3}$           |

| S <sub>3,0</sub>    | S <sub>3,1</sub>    | $S_{3,2}$           | $\mathcal{S}_{3,3}$ |

Figure 2-5 AES State Array

In AES, all the 128 bits of data are processed based on the two-dimensional state array. It contains 16 bytes, which are placed in 16 cells. The byte mapping is based on the equation

$$S(row, column) = data(row + 4 \times column)$$

(2-3)

where S is the byte cell in the state array, data is the 16-byte input/output data, and row and column range from 0 to 3.

#### 2.3.1 SubBytes

In the transformation of SubBytes, a  $16\times16$  lookup table is used to perform the byte-by-byte substitution. Each byte in the state array is replaced by a value in the S-box. The mapping rule is to use left hexadecimal value (x) as the row and right hexadecimal value (y) as the column. For example, the hexadecimal value A7

at the input of an S-box means row A and column 7, which will lead us to the S-box's output value 5C.

|   |   | y  |    |    |    |    |    |    |             |    |    |    |    |    |    |    |    |

|---|---|----|----|----|----|----|----|----|-------------|----|----|----|----|----|----|----|----|

|   |   | 0  | 1  | 2  | 3  | 4  | 5  | 6  | 7           | 8  | 9  | A  | В  | C  | D  | E  | F  |

| x | 0 | 63 | 7C | 77 | 7B | F2 | 6B | 6F | C5          | 30 | 01 | 67 | 2B | FE | D7 | AB | 76 |

|   | 1 | CA | 82 | C9 | 7D | FA | 59 | 47 | F0          | AD | D4 | A2 | AF | 9C | A4 | 72 | C0 |

|   | 2 | В7 | FD | 93 | 26 | 36 | 3F | F7 | $^{\rm CC}$ | 34 | A5 | E5 | F1 | 71 | D8 | 31 | 15 |

|   | 3 | 04 | C7 | 23 | C3 | 18 | 96 | 05 | 9A          | 07 | 12 | 80 | E2 | EB | 27 | B2 | 75 |

|   | 4 | 09 | 83 | 2C | 1A | 1B | 6E | 5A | A0          | 52 | 3B | D6 | В3 | 29 | E3 | 2F | 84 |

|   | 5 | 53 | D1 | 00 | ED | 20 | FC | В1 | 5B          | 6A | CB | BE | 39 | 4A | 4C | 58 | CF |

|   | 6 | D0 | EF | AA | FB | 43 | 4D | 33 | 85          | 45 | F9 | 02 | 7F | 50 | 3C | 9F | A8 |

|   | 7 | 51 | A3 | 40 | 8F | 92 | 9D | 38 | F5          | BC | В6 | DA | 21 | 10 | FF | F3 | D2 |

|   | 8 | CD | 0C | 13 | EC | 5F | 97 | 44 | 17          | C4 | A7 | 7E | 3D | 64 | 5D | 19 | 73 |

|   | 9 | 60 | 81 | 4F | DC | 22 | 2A | 90 | 88          | 46 | EE | B8 | 14 | DE | 5E | 0B | DB |

|   | A | E0 | 32 | 3A | 0A | 49 | 06 | 24 | 5C          | C2 | D3 | AC | 62 | 91 | 95 | E4 | 79 |

|   | В | E7 | C8 | 37 | 6D | 8D | D5 | 4E | A9          | 6C | 56 | F4 | EA | 65 | 7A | ΑE | 08 |

|   | C | BA | 78 | 25 | 2E | 1C | A6 | В4 | C6          | E8 | DD | 74 | 1F | 4B | BD | 8B | 8A |

|   | D | 70 | 3E | B5 | 66 | 48 | 03 | F6 | 0E          | 61 | 35 | 57 | B9 | 86 | C1 | 1D | 9E |

|   | E | E1 | F8 | 98 | 11 | 69 | D9 | 8E | 94          | 9B | 1E | 87 | E9 | CE | 55 | 28 | DF |

|   | F | 8C | A1 | 89 | 0D | BF | E6 | 42 | 68          | 41 | 99 | 2D | 0F | B0 | 54 | BB | 16 |

Figure 2-6 AES S-box

#### 2.3.2 ShiftRows

In the ShiftRows transformation, a circular byte shift is conducted on each row. Assume i represents row number from 0 to 3. Row i is rotated i bytes to the left. The first row stays the same. The second row is shifted by 1 byte. The third row shifts by 2 bytes and 3 bytes circular left shift is performed on the fourth row.

#### 2.3.3 MixColumns

In the state array, the MixColumns transformation mixes data within columns. The calculation is performed on column data with the following matrix multiplication.

$$\begin{bmatrix} 02 & 03 & 01 & 01 \\ 01 & 02 & 03 & 01 \\ 01 & 01 & 02 & 03 \\ 03 & 02 & 01 & 01 \end{bmatrix} \begin{bmatrix} s_{0,0} & s_{0,1} & s_{0,2} & s_{0,3} \\ s_{1,0} & s_{1,1} & s_{1,2} & s_{1,3} \\ s_{2,0} & s_{2,1} & s_{2,2} & s_{2,3} \\ s_{3,0} & s_{3,1} & s_{3,2} & s_{3,3} \end{bmatrix} = \begin{bmatrix} s'_{0,0} & s'_{0,1} & s'_{0,2} & s'_{0,3} \\ s'_{1,0} & s'_{1,1} & s'_{1,2} & s'_{1,3} \\ s'_{2,0} & s'_{2,1} & s'_{2,2} & s'_{2,3} \\ s'_{3,0} & s'_{3,1} & s'_{3,2} & s'_{3,3} \end{bmatrix} \tag{2-4}$$

The matrix multiplication can be expressed as following equations.

$$s'_{0,j} = (2 \cdot s'_{0,j}) \oplus (3 \cdot s'_{1,j}) \oplus s'_{2,j} \oplus s'_{3,j}$$

$$s'_{1,j} = s'_{0,j} \oplus (2 \cdot s'_{1,j}) \oplus (3 \cdot s'_{2,j}) \oplus s'_{3,j}$$

$$s'_{2,j} = s'_{0,j} \oplus s'_{1,j} \oplus (2 \cdot s'_{2,j}) \oplus (3 \cdot s'_{3,j})$$

$$s'_{3,j} = (3 \cdot s'_{0,j}) \oplus s'_{1,j} \oplus s'_{2,j} \oplus (2 \cdot s'_{3,j})$$

(2-5)

Note that the addition and multiplication are performed in Galois Field GF(2<sup>8</sup>) based on generator polynomial  $m(x) = x^8 + x^4 + x^3 + x + 1$ , where addition can be regarded as bit-wise exclusive-or (XOR). From (2-5) it can be seen that there are only multiplications by 2 and 3. Because 3x = 2x + x, multiplication by 3 can be simplified so that we only need to implement multiplication by 2 followed by an addition. Moreover, multiplication by 2 can be simplified by implementing left shift by 1 bit. If the most significant bit of the original value is 1, then it should also be XORed with a binary value 00011011 to produce the resulting product in GF(2<sup>8</sup>).

### 2.3.4 AddRoundKey

In the AddRoundKey transformation, the state array is XORed with the round key. Each column of state array is XORed bit-by-bit with one word of the round key, which is w[i].

#### 2.3.5 Key Expansion

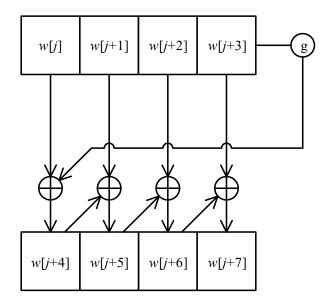

For AES-128, the key expansion algorithm produces 44 words (4 words for each round plus the initial key mixing). Each word is to be XORed with one column of the state array. As shown in the Figure 2-7, the beginning four words are created by concatenating four consecutive bytes in the state array. That is, every word is originally a column in the AES key. Then every subsequent word w[i] ( $4 \le i \le 43$ ) is produced based on w[i-1] and w[i-4]. For the three right most words, they are generated with the follow equation.

$$w[i] = w[i-1] \oplus w[i-4] \tag{2-6}$$

However, for the left most word, for which i is a multiple of 4, the function g in Figure 2-7 can be expressed as the following equation.

$$w[i] = w[i-1] \oplus (SubWord(RotWord(w[i-4])) \oplus Rcon[i/4]) \qquad (2-7)$$

The function RotWord() performs circular left shift on a word and SubWord() performs SubBytes on four bytes using the S-box. Then the result is XORed with Rcon[j], which is called the round constant. The round constants in hexadecimal are listed in the Table 2-1.

Table 2-1 AES Round Constants

| j    | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 |

|------|----|----|----|----|----|----|----|----|----|----|

| Rcon | 01 | 02 | 04 | 08 | 10 | 20 | 40 | 80 | 1B | 36 |

Figure 2-7 AES Key Expansion

### 2.4 Conventional Modes of Operation

When encrypting a message which is longer than one block, straightforward use of a block cipher can lead to security issues. As a result, various modes of operation are defined to work with block ciphers. In 1980, the National Institute of Standards and Technology (NIST) defined four modes of operation for block ciphers, specifically DES, including ECB, CBC, CFB and OFB mode in the Federal Information Processing Standards Publication 81 (FIPS PUB 81) [6]. Then in the NIST Special Publication 800-38A 2001 Edition (SP 800-38A), block cipher modes of operation were expanded to include counter (CTR) mode [7].

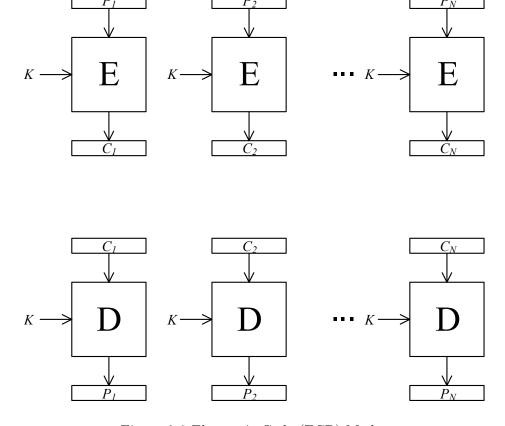

### 2.4.1 Electronic Codebook (ECB) Mode

Electronic codebook (ECB) mode [7] straightforwardly uses the block cipher to directly encrypt, or decrypt, each block of size B bits. For messages longer than

one block, the message will be broken into B bit blocks. The last block will be padded if it is not B bits. Figure 2-8 shows both encryption and decryption of ECB mode, where P is plaintext, C is ciphertext, K is key, E means encryption and D represents decryption. ECB mode uses the same key for a piece of message, so that every plaintext block corresponds to a unique ciphertext block (and vice versa). This characteristic makes it work like a c odebook.

ECB mode is typically used to transmit small amounts of data, such as cipher keys. For long messages, its codebook characteristic will be a disadvantage. Two identical plaintext blocks will lead to same ciphertext blocks, which may cause a problem if

Figure 2-8 Electronic Code (ECB) Mode

the message has a certain pattern. Also, if a 1 bit error occurs in the ciphertext block in the communication channel, the entire decrypted block is corrupted with about 1/2 bits in the recovered plaintext of the block being in error.

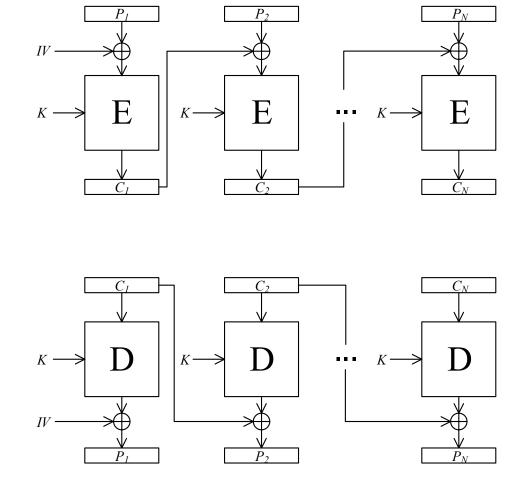

### 2.4.2 Cipher Block Chaining (CBC) Mode

Cipher block chaining (CBC) mode [7], as shown in Figure 2-9, is a chain structure, which is designed to eliminate the repeated ciphertext problem of ECB mode. The first plaintext block is XORed with an initialization vector (IV) before being encrypted. The second block of plaintext is XORed with the output block of the

Figure 2-9 Cipher Block Chaining (CBC) Mode

first encryption. This chain mode avoids the possibility that the same plaintext blocks will have the same ciphertext, thus improving security. Block padding is also needed in CBC mode. Decryption needs the same IV and key. We can also use ECB mode to transmit IV and secret keys. In CBC, a 1 bit error in the communication channel leads to corruption of the corresponding recovered plaintext block and a 1 bit error in the next block.

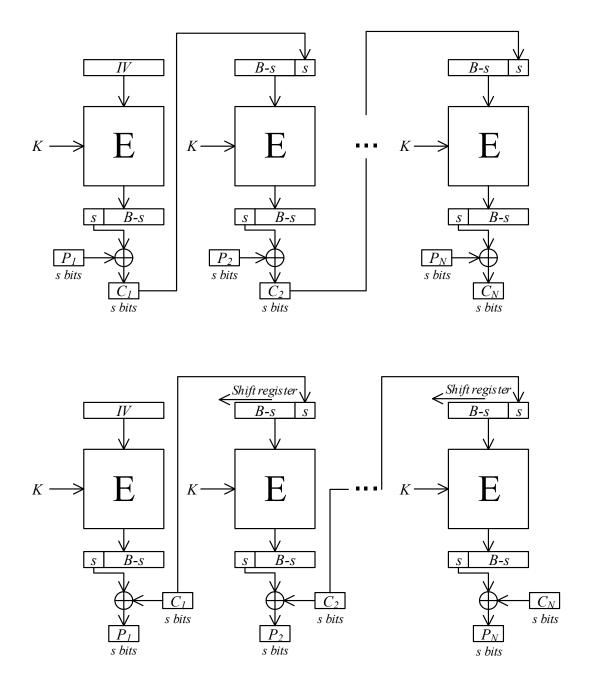

### 2.4.3 Cipher Feedback (CFB) Mode

Cipher feedback (CFB) mode [7] is used to configure a block cipher as a stream cipher. The block cipher is used to generate the keystream and the ciphertext is produced by XORing plaintext with the keystream. The ciphertext is sent back as the input of the block cipher. The plaintext is divided into several blocks of s bits. An IV is also used to initialize the encryption process. The most significant s bits of the B bit output of the block cipher is XORed with the s bit plaintext block. In CFB, a shift register is used to store the IV and fedback ciphertext. This shift register left shifts by s bits, and is then loaded with the s bit ciphertext block at the least significant position.

In the decryption process, the encryption algorithm of the block cipher is used instead of the decryption algorithm. This is because neither plaintext nor ciphertext has a direct relationship with the block cipher. Received ciphertext is XORed with the most significant s bits from block cipher's output, thus recovering the plaintext. The ciphertext block is also fed to a shift register similar to the process for encryption. For error propagation, a 1 bit error in the ciphertext block results in a

1 bit error in the recovered plaintext block and the entire next block is also corrupted.

Figure 2-10 Cipher Feedback (CFB) Mode

The CFB mode manipulates the block cipher in a stream cipher way. It is a self-synchronizing cipher because CFB can recover from bit slips. A bit slip refers to one or more bits being lost during the data transmission. CFB mode can recover from bit slips for which the number of lost bits is a multiple of s. To enable the self-synchronization capable of recovery from any number of bits, only one bit can be fed back to the input of block cipher, which means s=1. However, this will greatly reduce the efficiency comparing with ECB and CBC mode because only s=1 bit of data is encrypted or decrypted for each block of data passed through the block cipher. In ECB and CBC mode, the whole block of B bits is processed in a unit time. Assuming that the encryption function is AES with a 128 bit block size, the efficiency can only reach 1/128=0.78%.

### 2.4.4 Output Feedback (OFB) Mode

Output feedback (OFB) mode is another method of configuring a block cipher to operate as a stream cipher [7]. However, instead of feeding back ciphertext as in CFB mode, OFB mode feeds the block cipher's output back as its input. OFB mode can feedback the whole block of data most efficiently, but can also be configured to feedback any number of bits s ( $s \le B$ ), as shown in Figure 2-11. At the beginning of encryption, an IV is sent to the block cipher, to produce the first block. Then, s bits of this block is then XORed with the plaintext to generate the ciphertext. In addition, s bits of the block are used as the input of the block cipher for the next block. As with CFB, the block cipher encryption algorithm is also employed in the decryption process. Using the same key and IV could produce the same keystream

block, and then the plaintext is recovered by XORing the block with ciphertext. If a 1 bit error occurs in ciphertext block during transmission, the recovered plaintext block has only a 1 bit error.

Figure 2-11 Output Feedback (OFB) Mode

The OFB mode is also controlling a block cipher as a stream cipher. The block generated by the block cipher is actually a keystream block. XORing the keystream with plaintext is just like what a stream cipher does. One advantage of OFB mode is that bit errors will not propagate. The bit errors in the ciphertext block will only reflect on the corresponding recovered plaintext bits.

However, OFB mode cannot recover from bit slips and is not self-synchronizing. If one or more bits are lost, what is received at decryption part is not a full block of ciphertext. In the decryption process, the system will use some bits of the subsequent block to make up a full block. Hence, all the recovered plaintext after the bit slip is corrupted. Since OFB cannot self-synchronize, an extra module is needed for synchronization in the implementation, which will cost some additional resources.

## 2.4.5 Counter (CTR) Mode

Similar to CFB mode and OFB mode, counter (CTR) mode [7] also makes a block cipher work like a stream cipher. In CTR mode, a counter is used as the input for the block cipher. The counter is initialized with a value and then encrypted. The generated keystream block is XORed with the incoming plaintext block. The counter is increased by 1 each time, thus producing different keystream blocks. In decryption, CTR mode uses the encryption function of the block cipher, which is similar to CFB mode and OFB mode. The counter in decryption must be synchronized to the counter in encryption and, hence, CTR is not self-synchronizing

and cannot recover from bit slips. As for the error propagation issue, a 1 bit error in ciphertext will result in 1 bit error in recovered plaintext.

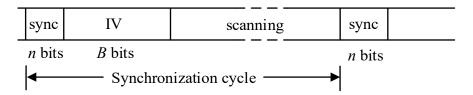

CTR mode is easier than ECB and CBC mode for implementation. Both the encryption and decryption needs only the encryption algorithm. Another major advantage is that CTR mode is suitable for pipelining. There is no feedback in CTR mode, thus a block cipher can be modified to a pipelined architecture.

Figure 2-12 Counter (CTR) Mode

# 2.5 Statistical Self-Synchronization

Due to the inefficiency of CFB mode with self-synchronizing and OFB without self-synchronizing, a mode is necessary to provide both high speed and self-synchronizing. In this section, a statistical self-synchronizing mode is introduced and discussed.

### 2.5.1 Statistical Cipher Feedback (SCFB) Mode

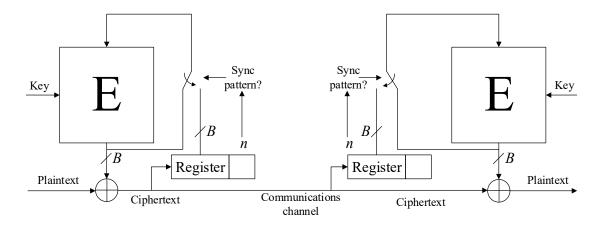

Statistical self-synchronization is proposed in [8] and Statistical Cipher Feedback (SCFB) mode is analyzed in [2] as a way to solve the efficiency problems associated with the self-synchronization approach of CFB. This mode of operation is designed for use in high speed communication channels. Nowadays, the synchronous optical network (SONET/SDH) has the data rate from 40 Gbps up to even 100 Gbps and it is commonly used around the world. It is not easy to implement an encryption system to reach such a high throughput in a SONET/SDN environment. Bit slips are another major situation needed to be considered in all kinds of communication channels, which means one or more bits are eliminated from the received data stream. If a bit slip occurs and the encryption and decryption systems cannot self-synchronize, the received ciphertext stream will be decrypted to perpetually random data until a costly resynchronizing procedure is undertaken. However, a system with self-synchronization can recover from bit slips by automatically resynchronizing based on received ciphertext data.

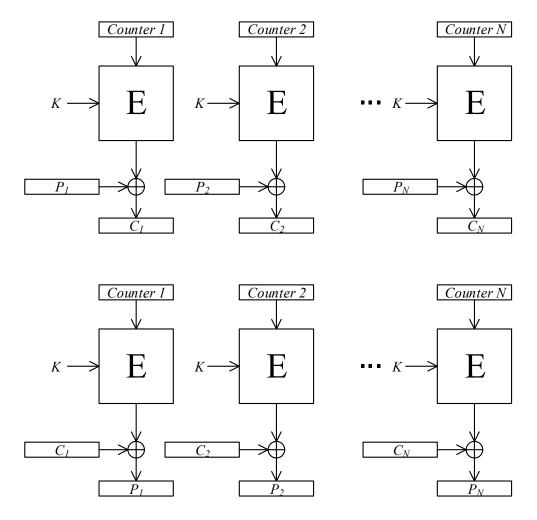

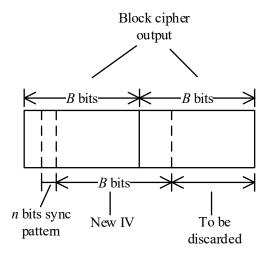

As proposed in [2], SCFB mode operates as OFB or CFB under different conditions. When the system is scanning for an n bit sync pattern in ciphertext, it works as OFB mode. When the sync pattern is found, the B bit ciphertext following the sync pattern will be loaded as a new IV as in CFB mode. Figure 2-13 shows the whole process of a synchronization cycle on the ciphertext stream.

Figure 2-13 SCFB Synchronization Cycle

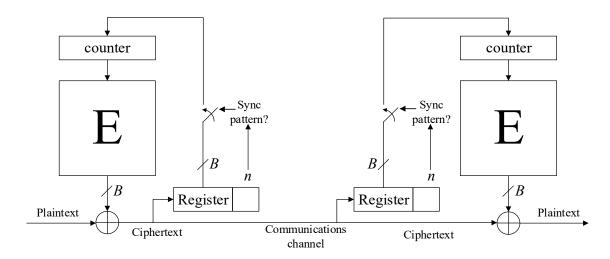

In detail, both of the encryption and decryption system search for the sync pattern in ciphertext stream during the scanning period. The system runs as OFB mode since the output of the block cipher is fed back to the input. When there is a pattern in ciphertext stream exactly the same as the given sync pattern, a new synchronization cycle begins. The subsequent B bits of ciphertext are collected and loaded to the input of the block cipher as a new IV. Obviously, this process is CFB mode. Also, during this ciphertext collecting process, any newly recognized sync pattern will be ignored. After the new IV has been loaded, the scanning is turned on again and the system will return to OFB mode. Figure 2-14 shows the diagram of SCFB mode.

Figure 2-14 Architecture of SCFB Mode

Note that there are some output bits from the block cipher to be discarded. Once the new IV is loaded, the new generated output is to XOR with plaintext, which means the unused bits from last output block must be discarded. Figure 2-15 shows the synchronization cycle from the perspective of the block cipher output. Note that the number of discarded bits can be from 0 to B - 1.

Figure 2-15 SCFB Synchronization Cycle Based on Blocks

### 2.5.2 SCFB Mode with Counter Mode

In SCFB, OFB mode can also be replaced by CTR mode [4]. As shown in Figure 2-16, the counter continuously generates input for the block cipher. If a sync pattern is found, the subsequent B bit ciphertext will be loaded to the counter as a new IV block. During the scanning period, the counter increases by one for each block encryption.

Figure 2-16 Architecture of SCFB Mode with Counter

#### 2.5.3 PSCFB Mode

Pipelining leads to high speed, which means high throughput in network communication. However, although SCFB is efficient in terms of the number of ciphertext bits produced per execution of the block cipher, conventional SCFB mode does not support a pipeline structure for the underlying block cipher. This is because OFB mode cannot be pipelined and SCFB mode was initially defined to operate as OFB mode.

Even with the CTR mode replacing OFB in SCFB, it is still difficult to implement pipelining. Assume 128 bit AES with 10-stage pipelining is used as the block cipher in SCFB with CTR mode. The corresponding output of the block cipher is expected 10 clock cycles later than an IV being loaded. The problem is that, when the newly collected IV is immediately loaded to AES, the remaining data still in the pipeline becomes useless and the outputs will be discarded. As a result, the data stream through the cipher has to stall and wait for the expected output from the pipelined AES. Hence, there is substantial time delay and pipelining is not suitable for SCFB mode. It is also a big challenge for the queue size of an implementation since the system has to absorb incoming data while waiting for the pipelined AES output. However, the advantage of CTR mode is that it is possible to implement a pipeline structure in a modified version of SCFB mode. Hence, Pipelined Statistical Cipher Feedback (PSCFB) mode was proposed in [4]. It can be regarded as a generalized version based off SCFB mode with counter.

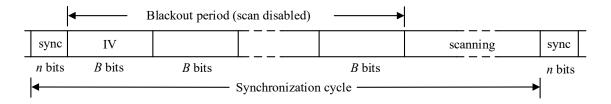

Figure 2-17 PSCFB Synchronization Cycle

As is shown in Figure 2-17, PSCFB mode works similarly to SCFB mode. It scans the ciphertext for an n bit sync pattern. Once the matched pattern appears, it starts to collect IV bits. During this collecting period, the scanning is disabled. However, assuming that PSCFB is using an L-stage pipelined AES, the output

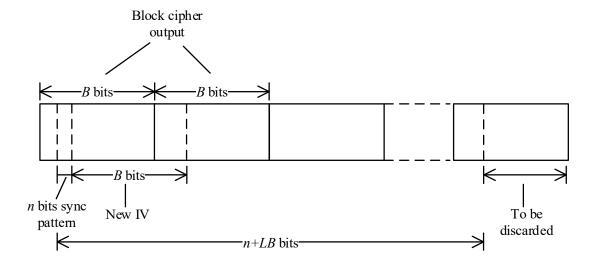

corresponding to newly loaded IV will only be available L clock cycles later. That is, only the output after L clock cycles can be scanned again for sync pattern. Hence, the period during which scanning is disabled is named the *blackout* period [4]. The length of the blackout period is L clock cycles, and the amount of processed bits is LB.

Note that there are some output bits of the block cipher to be discarded at the end of blackout period, just as in SCFB [4]. First of all, sync pattern is found with a B bit block of ciphertext, which is the result of B bit output of block cipher XORing with B bit plaintext. Also, the blackout period processes LB bits of data. These two facts make some unused bits left in the output of block cipher. To clarify, neither plaintext nor ciphertext will be eliminated from the stream. At the end of the blackout period, only the output of block cipher has 0 to B - 1 discarded bits. Figure 2-18 shows the synchronization cycle from the perspective of block cipher output.

Figure 2-18 PSCFB Synchronization Cycle Based on Blocks

## 2.6 Target Technologies

In this section, we will give introduction to Application-Specific Integrated Circuits (ASICs) and Field-Programmable Gate Arrays (FPGAs) and discuss the difference. ASIC and FPGA are our targeted synthesis environments and ASIC is our final goal.

### 2.6.1 Application-Specific Integrated Circuit (ASIC)

An ASIC is an integrated circuit for applications like a microprocessor, digital signal processor, wireless module and so on. There are different methodologies: full-custom, standard-cell, gate array and structured design [9]. In a full-custom design, each function is manually done by transistor level design, which costs the highest in the development process. In order to reduce the initial investment in design and manufacturing, standard-cell components have been created and contained in a library file, including commonly used gates, flip-flops and logic functions. However, standard-cell design may still be expensive, so gate-array based design is developed. An IC chip is initially fabricated with gate arrays and design engineers just need to define the gate types and interconnections. Structured design is a new concept, in which ASIC chips are designed with pre-defined metal layers, thus reducing cost and development time. ASIC design flow contains some major procedures: design specification, HDL coding, synthesis, floorplanning, place and route, fabrication and post-silicon validation.

### 2.6.2 Field-Programmable Gate Array (FPGA)

An FPGA is a logic device which can be programmed for different applications. Altera FPGAs contain logic elements (LEs) which are the basic logic components. A logic element has one lookup table (LUT) as combinational logic function and one flip-flop as sequential logic. Similar to gate array based ASICs, each LE in an FPGA can be connected with others. Hence, logic elements and interconnections can be programmed by the engineers to implement different circuits. A typical FPGA such as the Altera Cyclone IV FPGA offers an embedded RAM block. In our implementation of PSCFB, we will not use RAM.

FPGA design flow contains major procedures: design specification, HDL coding, synthesis, place and route, and final programming to FPGA. Compared with ASIC design flow, FPGA requires less time and human resources, thus reducing the cost.

#### 2.6.3 ASIC vs. FPGA

ASICs have several advantages over FPGAs. Compared with FPGA, ASICs can reach a faster clock frequency. An FPGA is an already produced chip with limited area. However, an ASIC chip can be designed to be either small or big depending on requirements. ASICs typically have lower power consumption than FPGAs. From economic perspective, ASICs have the lowest price for high-volume production.

However, ASICs do have disadvantages. Because an ASIC is a one-shot industry, which means ASIC chips will be put into market once after being fabricated. This

requires longer design cycle to guarantee there is no errors in logic and circuits, including long verification period to ensure functionality. Electronic Design Automation (EDA) tools are relatively expensive compared to FPGA tools. There are also high costs for buying Intellectual Property (IP) cores for some specific application areas, such as IP cores for SONET/SDH. The non-recurring engineering (NRE) [9] cost can be as high as billions of dollars. NRE is the charges to develop, design, test and manufacture. Hence, a company will not start to produce an ASIC chip unless it is expected to have significant profit.

FPGA has lower cost than ASIC for low to medium volume production. The design flow is really simple and it only requires one or two tools from the FPGA company, such as Quartus II from Altera. There are no NRE costs. The FPGA is a standard product thereby allowing engineers to have shorter design cycles. Due to FPGA's programmable feature, engineers can fix bugs and update quickly with less cost than ASIC.

FPGAs also have disadvantages. FPGAs typically have lower speed, thus leading to lower performance than ASIC. The overall FPGA is a digital circuit except for phase lock loops (PLLs) which are analog circuits. A design on FPGA consumes more power than on ASIC because FPGA does not have a better power optimization. A design on ASIC can be optimized for lower power.

#### 2.7 Previous Work of PSCFB

One hardware implementation of PSCFB is described in [10]. The pipelined AES with 128-bit key is implemented. There are three clocks in this PSCFB system. The first clk1 is the internal system clock, which is for data transfer between plaintext queue and ciphertext queue are used as two buffers to receive plaintext and send ciphertext because of the different clock frequency between the system and other devices. The second clk2 is used for data transfer between the system and other devices. Signal clk1 is set to twice the rate of clk2 to ensure the plaintext queue does not overflow. The third clock, clk3, is used for the block cipher.

In this implementation, the output of AES is stored in one of two identical 128 bit shift registers, which are used to save output from AES. The data transfer rate inside the system is 8 bits and it is based on clock clk1. The shift register sends out 8 bits of data out to XOR with 8 bits of plaintext, and then the ciphertext is received by the ciphertext queue. The queueing system is based on asynchronous FIFO, which has a write part and a read part due to two different clocks. For the plaintext queue, the write part is clocked by clk2, which deals with incoming data from other devices. The read part is clocked by clk2, which is in charge of sending data to the ciphertext queue. The ciphertext queue is reversed, with write part clocked by clk1 and read part clocked by clk2. An IV Shift Register, which is used to scan ciphertext and collect IV, receives the generated 8 bit ciphertext and scans

it for sync pattern. When the pattern matches, the IV Shift Register will start to collect the new IV for the counter.

This PSCFB implementation is synthesized in an ASIC environment with TSMC 180 nm CMOS standard cell. The clock period of clk2 is 24 ns, which is equal to 41.67 MHz as frequency. The clk2 is related to the write part of plaintext queue and read part of ciphertext queue, which means the input and output of PSCFB system. Hence, the final throughput of PSCFB system is 41.67 MHz  $\times$  8 bits = 333 Mbps, which is far too small compared with the ideal throughput of AES with 5.333 Gbps at the corresponding clock rate.

# 2.8 Summary

In this chapter, the necessary cryptography background is introduced, including symmetric key cipher, block cipher, stream cipher, modes of operation and AES. The self-synchronizing modes of operation, SCFB and PSCFB mode, are described and discussed. Hardware concepts of FPGA and ASIC are briefly introduced as this thesis is about hardware implementation of PSCFB. A previous work on hardware implementation of PSCFB mode is briefly introduced.

# Chapter 3

# Pipelined AES

In this section, a 10 stage pipelined implementation of AES used in the study of PSCFB mode is described. In addition, several structures of block cipher implementation are introduced, compared and analyzed.

## 3.1 Basic Architecture Without Pipelining

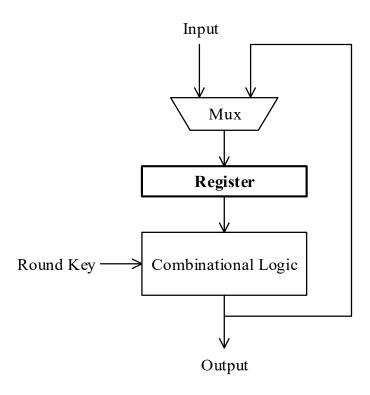

The basic way to implement a block cipher is to use an iterative architecture [11]. Figure 3-1 shows the iterative architecture of a block cipher. It is a single round with multiplexer, register and combinational logic. The combinational logic contains operations for each round, such as S-box, key mixing, SubBytes, MixColumns, ShiftRows and AddRoundKey. In the beginning round, the input data is sent to the register and then combinational logic. In the subsequent rounds, the output of combinational logic is fed back through the multiplexer into the

register, until the final round which presents the output from the combinational logic. Note that the structure for the round key is not illustrated in the figure.

Figure 3-1 Basic Iterative Architecture

It is obvious that basic iterative architecture has a major disadvantage for throughput. For AES with 128 bit key, assuming initial key mixing is integrated into the first round, it needs R=10 rounds of iteration, which means a single block occupies the block cipher for 10 clock cycles.

The throughput and latency are given in [11] as follows, where B is the block size, R is the number of rounds of AES and  $T_{clk}$  is the clock period.

$$Throughput_{iterative} = \frac{B}{R \times T_{clk}} \text{ bps}$$

(3-1)

$$Latency_{iterative} = R \times T_{clk} \text{ seconds}$$

(3-2)

# 3.2 Loop Unrolling

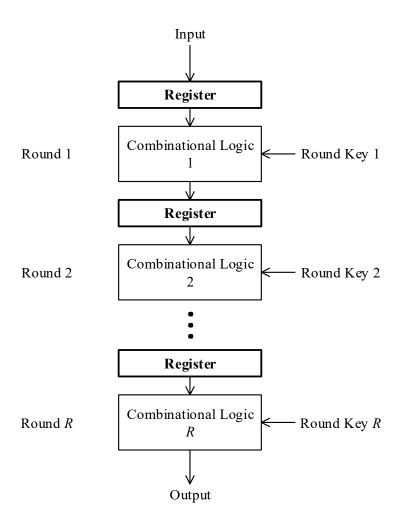

Loop unrolling is an effective way to reduce the number of clock cycles occupied by a data block. As shown in Figure 3-2, AES is fully unrolled by implementing and connecting the combinational logic parts of every round. In this case, the

Figure 3-2 Loop Unrolling

multiplexer is removed and all round keys must be generated simultaneously. Note that the round key structure is not shown.

However, employing the resulting large combinational logic leads to potentially a very long critical path. The clock period will increase due to the long critical path. If the synthesis tool optimizes the clock period  $T_{clk(loop\_unrolling)}$  to be smaller than  $R \times T_{clk}$  in iterative architecture, the loop unrolling architecture may have slightly lower latency and higher throughput.

$$Throughput_{loop\_unrolling} = \frac{B}{T_{clk(loop\_unrolling)}} \text{ bps}$$

(3-3)

$$Latency_{loop\_unrolling} = T_{clk(loop\_unrolling)} \text{ seconds}$$

(3-4)

# 3.3 Pipelining

Pipelining can be used to increase throughput by inserting registers in any part of the combinational logic of Figure 3-2. As a result, the length of critical path is reduced. There are two types of pipelining for AES, inner-round and outer-round [11].

### 3.3.1 Outer-Round Pipelining

Outer-round pipelining only inserts registers between rounds. In Figure 3-3, the pipeline register is inserted between each two rounds in the block cipher. Note that the key structure is not shown. Based on this, the latency is the same as in the iterative architecture. Although it also takes R clock cycles to get the output, this

architecture can simultaneously process R blocks of data, thus increasing the throughput.

Figure 3-3 Outer-round Pipelining

The throughput and latency of pipelined structure is given as follows in [11].

$$Throughput_{outer-round} = \frac{B}{T_{clk}} \text{ bps}$$

(3-5)

$$Latency_{outer\_round} = Latency_{iterative}$$

(3-6)

In this equation,  $T_{clk}$  is the clock period of one round, which is similar to the clock period in an iterative architecture. We can conclude that fully outer-round

pipelined structure has an R-fold increase in throughput, compared with an iterative implementation. Hence, for a 10 round pipeline of AES, this gives a 10 fold increase.

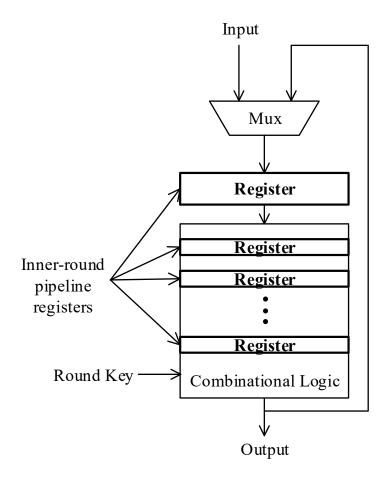

### 3.3.2 Inner-Round Pipelining

As the names states, the inner-round pipelining is the technique for which registers are inserted inside the round of a block cipher. For example, a single round of AES includes SubBytes, ShiftRows, MixColumns and AddRoundKey. The register can be inserted between any of these operations, and even in the middle of an operation. Figure 3-4 is an iterative structure with inner-round pipelining. Note that the key structure is not shown in this figure. The equations of throughput and latency of inner-round pipelining architecture are shown below.

$$Throughput_{inner\_round} = \frac{B \times k}{R \times k \times T_{clk(inner\_round)}} = \frac{B}{R \times T_{clk(inner\_round)}} \text{ bps} \quad (3-7)$$

$$Latency_{inner\ round} = R \times k \times T_{clk(inner\_round)} \text{ seconds}$$

(3-8)

$T_{clk(inner\_round)}$  is the clock period of a stage in an inner-round pipelining, and k means the number of stages of the inner-round pipelining. Although the equations look to be lower throughput than outer-round pipelining,  $T_{clk(inner\_round)}$  is much smaller than a round clock period  $T_{clk}$ , thus resulting in higher throughput. However, as shown in equation (3-8), the latency is uncertain. If the synthesis tool is able to shorten the critical path to make  $k \times T_{clk(inner\_round)}$  smaller than a round clock period  $T_{clk}$ , the inner-round pipelining will reach lower latency.

Figure 3-4 Inner-round Pipelining

# 3.4 Pipelined AES in PSCFB

In this thesis, only outer-round pipelining is applied to AES. Figure 3-5 is the architecture of pipelined AES. An AES implementation with a 128 bit key has 10 rounds, so that 10 pipeline registers are inserted between rounds. Note that as assumed above, the first pipeline stage includes initial key mixing plus round 1.

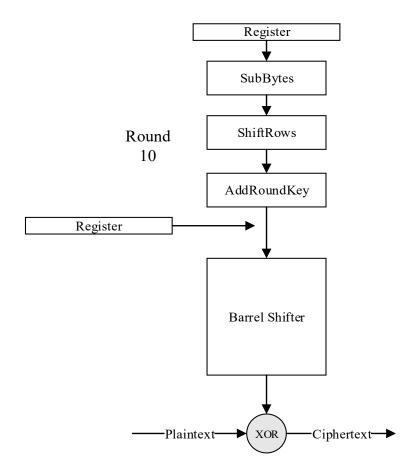

Figure 3-5 Pipelined AES in PSCFB

Unlike the method in the outer-round pipelining in Figure 3-3, the registers are put after each round. An LFSR counter is placed at the input of AES, so that there is

no need to put another register between the LFSR counter and the AddRoundKey combinational logic. In the last round of AES, we have SubBytes, ShiftRows and AddRoundKey. In addition, from the overall perspective, in our design of PSCFB mode, the output of AES will pass through a barrel shifter, which contains layers of multiplexers, and XOR gates. Hence, it is reasonable to place the pipeline register between the last AddRoundKey and barrel shifter. As shown in Figure 3-6, the critical path is shortened and the system will have better performance. This will be discussed in Section 4.6.

Figure 3-6 Register Insertion

### 3.5 Modified Blackout Period

As will be discussed in Chapter 4, in our implementation of PSCFB mode, when a new IV is collected by the sync pattern scanner and sent to LFSR counter, it will take one more clock cycle for AES to receive the IV. If we consider the LFSR counter as an extra pipeline stage, the pipelining is then increased to 11 stages. For an 11 stage pipeline, it will take 11 clock cycles to get the desired output. Hence, the blackout period for PSCFB mode is extended to L=11 blocks of B bits.

### 3.6 Summary

This chapter has discussed how the pipelined AES is implemented for our implementation of PSCFB mode. The description is started from showing the basic iterative architecture of block ciphers. The basic iterative architecture is then unfolded, which is called loop unrolling. The pipeline architecture is achieved by inserting registers between rounds. Although there are inner and outer-round pipelining architectures for block ciphers, only outer-round pipelining is discussed and implemented. Because an LFSR is used and connected with a 10 stage pipelined AES, the length of the blackout period for PSCFB is extended to 11 blocks.

# Chapter 4

# Design of PSCFB

In this chapter, the hardware design of the PSCFB mode of operation will be investigated. Pipelined AES with a 128 bit key has been applied as the block cipher. In studying the algorithm of PSCFB, we propose several different structures for data queues and other components. Each new structure has fewer hardware resources and smaller latency, thus achieving higher performance. The higher throughput can be reached by increasing bit width and improving frequency, which results from lower delay of the critical path. Since PSCFB mode is designed for use in high speed networks, the goal is to reduce the hardware resource usage as much as possible without affecting the throughput.

# 4.1 Design Considerations

As discussed in the last chapter, a partial block generated by the block cipher may be processed at the end of a blackout period. The amount of data, which is needed from plaintext or generated as ciphertext, can be less than the data width at the input and output ports. Based on that, two data queues, the plaintext queue and the ciphertext queue, are necessary as buffers to temporarily store the input plaintext and newly produced ciphertext [4].

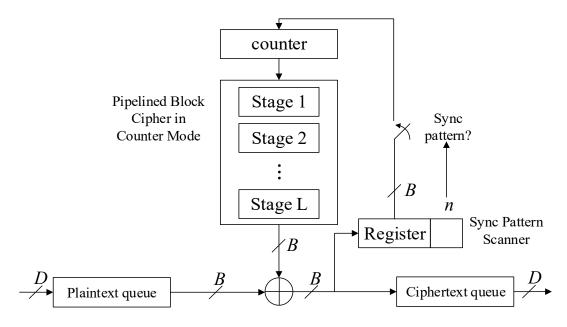

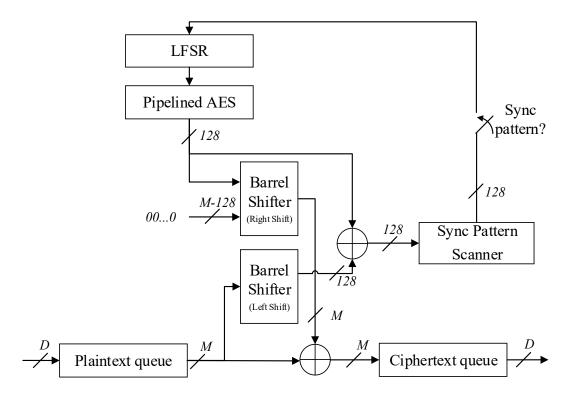

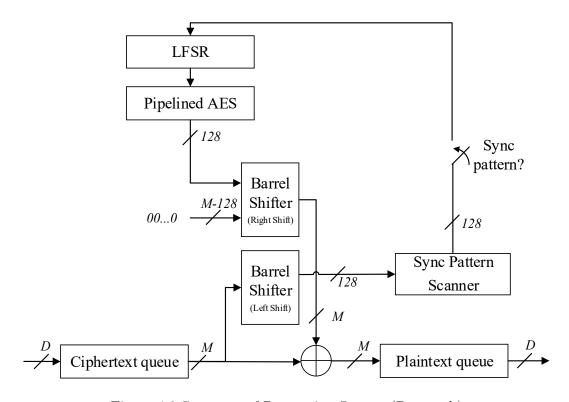

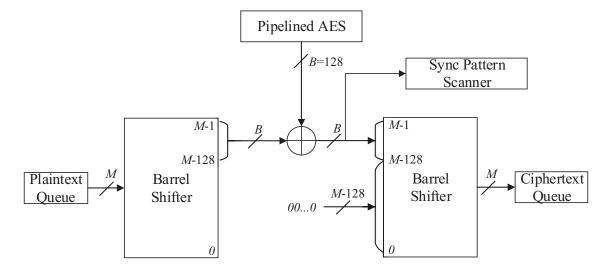

Figure 4-1 Architecture of PSCFB Encryption [4]

Figure 4-1 shows the encryption part of PSCFB. From the figure, B represents the block size inside the PSCFB system and D stands for data width in bits entering and leaving the system in every clock cycle. In other words, D effectively represents the data rate at which flows data through the system in terms of bits per clock cycle.

Data transfer between the plaintext queue and the ciphertext queue is split into three separate cases in [4]. In the first case, a whole block of data is being processed when the sync pattern is being scanned for, when the new IV is being collected and when in the blackout period, which means B bits of data are transferred. In the second case, the queue pauses when there is not sufficient data for transfer. The third case exactly comes from partial block at the end of the blackout period, and the number of bits ranges from 1 to 127 since for AES B=128.

If we set d to represent the number of bits to be processed, we have the following tables.

Table 4-1 Cases in Data Transmission for Plaintext Queue

| Plaintext<br>Queue<br>Process | Case 1 | Case 2 | Case 3        |

|-------------------------------|--------|--------|---------------|

| Enqueued bits                 | D      | D      | D             |

| Dequeued bits                 | d=B    | d = 0  | $1 \le d < B$ |

Table 4-2 Cases in Data Transmission for Ciphertext Queue

| Ciphertext Queue Process | Case 1 | Case 2  | Case 3          |

|--------------------------|--------|---------|-----------------|

| Enqueued bits            | d = B  | d=	heta | $1 \le d \le B$ |

| Dequeued bits            | D      | D       | D               |

These tables are based on the operation of a data queue as described in [4]. Taking the plaintext queue as an example, D bits are enqueued at every clock cycle. As long as the queue has more than B bits data (cases 1 and 3), it dequeues d bits and XORs these bits with the output of the block cipher. The ciphertext queue has the reversed input/output compared with plaintext queue. It enqueues d bits from the XOR gates and dequeues D bits.

In addition, overflow and underflow are to be considered. Assume pipelined AES is used so that B=128 bits. To ensure a stable queue and to avoid overflow in a plaintext queue or underflow in a ciphertext queue, D must be less than B. From [4], we can know that  $D \leq \frac{BL}{L+1} = 116$  when using pipelined AES with B=128 and L=10 to ensure that the plaintext (ciphertext) queue does not overflow (underflow). Hence, the minimum queue size, M, can be calculated from the equation  $M \geq B + 3D - 2 = 474$  bits<sup>1</sup>.

As a result, a FIFO structure with the above properties is a primary design issue and will affect the other parts of the PSCFB system, including the state machine. The resulting throughput of PSCFB system is determined by the data queues.

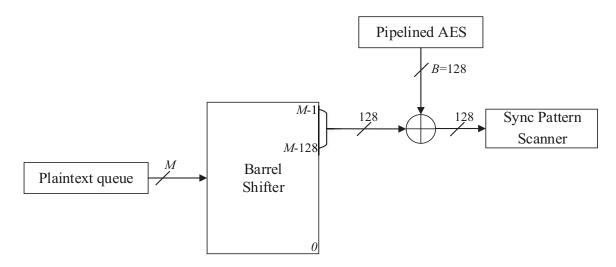

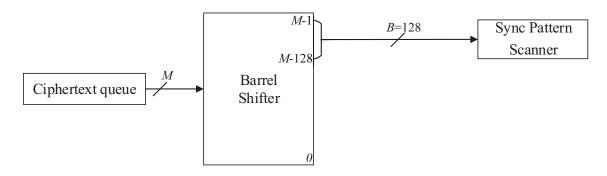

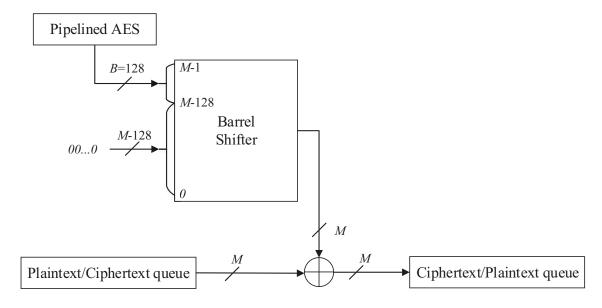

### 4.2 Overall Structure

Figure 4-2 and Figure 4-3 represent the two overall structures of the PSCFB encryption and decryption datapaths, with Design 3 of the queueing system (which will be discussed in the upcoming sections). There are 7 major components in a single PSCFB system. AES with 128 bit key is implemented with a 10 stage pipeline. The queueing system works as a buffer necessary due to the different data widths, D and B. The LFSR works as the counter in the CTR mode in PSCFB. The sync pattern scanner is used to search the ciphertext blocks in order to self-synchronize. There are two barrel shifters for shifting data to the designated positions.

<sup>&</sup>lt;sup>1</sup> Note that this is a correction to the constraint  $M \ge B + 2D - 2$  given in [3].

Figure 4-2 Structure of Encryption System (Datapath)

Figure 4-3 Structure of Decryption System (Datapath)

The structural difference between encryption and decryption is that decryption does not have the 128 bit XOR logic before the input of sync pattern scanner. The plaintext queue in encryption and ciphertext queue in decryption are exactly the same in structure. The ciphertext queue in encryption and plaintext queue in decryption are also the same.

## 4.3 Plaintext and Ciphertext Queue

A FIFO is a typical method to implement a data buffer. However, the FIFO in our system is quite different than a typical FIFO with fixed input and output width. According to the design considerations and architecture of PSCFB, for encryption the plaintext queue must have a D bit input and variable width output of d bits for scenarios where  $0 \le d \le 128$  bits are necessary. The ciphertext queue can be regarded as reversed queue to the plaintext queue, and it has variable width input of d bits and fixed D bit output. Although D and B are two different parameters, there is no padding in the queueing system.

In addition, the plaintext queue and ciphertext queue are set to be complementary to each other [4]. If the plaintext queue is being filled up, the ciphertext queue is being evacuated at the same time. In this way the system is balanced so that D bits can enter and D bits can exit the system every clock cycle. When the system is initialized, the plaintext queue is empty and ciphertext queue is full of random data. Every clock cycle, the plaintext queue receives D bits of data from an external device and ciphertext queue sends out D bits of data. At the same time, d bits (0)

$\leq d \leq 128$  for three cases) of data is transferred from the plaintext queue to ciphertext queue, with XORing with the AES output (which is the keystream). The sum of the number of bits in the plaintext queue and the number of bits in the ciphertext queue is constant and equals M.

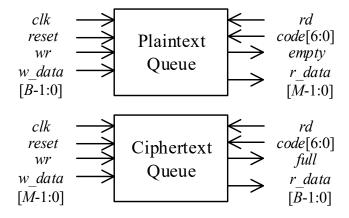

Figure 4-4 shows the I/O diagram of the final version of the plaintext queue and ciphertext queue in PSCFB. The signals wr and rd mean enable signals for writing and reading, respectively. The empty signal means the plaintext queue does not have enough data to send and full means the cipheretxt queue has no more space to save. The data ports,  $w\_data$  and  $r\_data$ , for writing and reading are different in the two queues.

Figure 4-4 I/O Diagram of Queueing System

### 4.3.1 Design 1: Basic Structure With Reduced Hardware

## Resource Usage

In this research, the data queues have simplified structure. The plaintext queue is firstly designed for a small scale system, which is easy to modify and test. Note that part of this content is presented as [12].

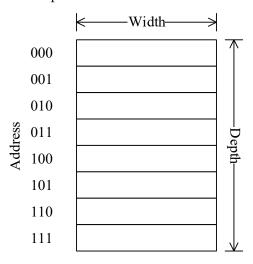

Either synchronous or asynchronous, a normal FIFO has fixed width input/output. However, such a queue cannot be used as a data queue in PSCFB. Basically, a general FIFO has registers as a data buffer, which has two parameters, width and depth. The width is usually the same as, or a multiple of, the input/output width. The depth means how many data elements (compared of a number of bits defined by the width) can be stored. The size of the FIFO in bits can be calculated by multiplication of width and depth.

Figure 4-5 General FIFO

As shown in Figure 4-5, in the general FIFO, the data is saved and fetched as individual data elements. For example, in a FIFO with 8-bit width, the data is saved byte by byte, which is easy to implement in digital hardware.

#### 4.3.1.1 Plaintext Queue: A Small Scale Example

In the PSCFB system, the variable output width in the plaintext queue has caused the issue that the data manipulation is based on the units of bit, thus causing difficulties in the implementation of the queueing system. In this section, the queueing system is similar to the one dimensional data array, rather than an array with given width and depth.

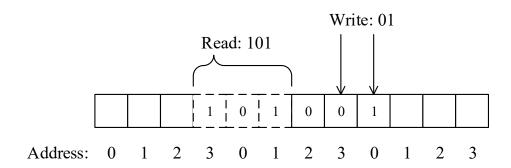

Figure 4-6 Reading and Writing Process in PSCFB

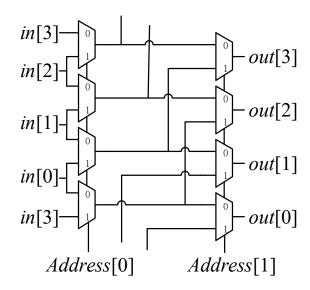

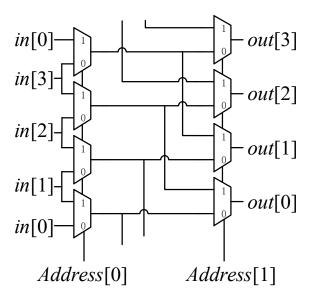

Consider an example queue where the read width is  $0 \le d \le 3$  since B = 3 bits, while the write width is D = 2 bits. The data processing is shown in Figure 4-6. This imbalance in the input and output processes leads to unpredictability in the data manipulation. Hence, fixed width and depth have no use and two-dimensional register array will not be applied in a PSCFB implementation. The PSCFB queue of data is not difficult to implement in one dimension in a software programming language. The registers align along a straight line, so that the array is one dimensional and circular, where it is necessary to keep track of the queue head and tail, which are pointers used to select the position of where data is removed and where data is added, respectively.

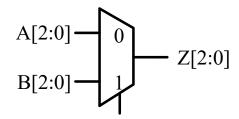

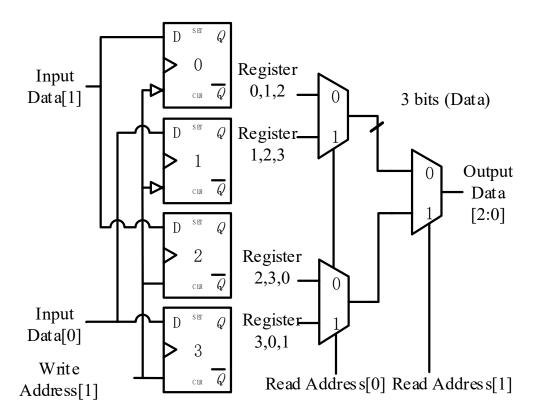

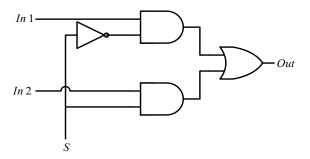

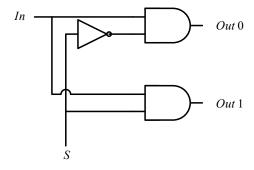

We now consider the design of a simple plaintext queueing system with B=3, D=2 and M=4 in hardware. In the system, a fixed number of D=2 bits is written in every clock cycle, and a variable number of bits are read,  $0 \le d \le 3$ , when B=3. In digital circuits, a 2-to-1 multiplexer (mux) and a 1-to-2 demultiplexer (demux)

can perform selection by selecting one out of two inputs (mux) or outputs (demux). As shown in Figure 4-7, a mux can be expanded to be a 3-bit mux, which means the data width of each port is 3 bits.

Figure 4-7 3-bit 2-to-1 Multiplexer

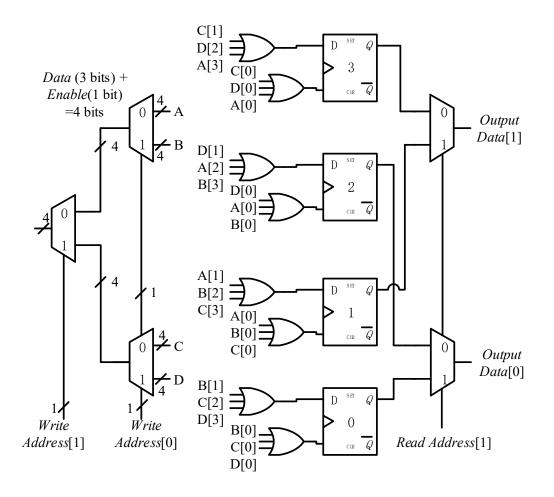

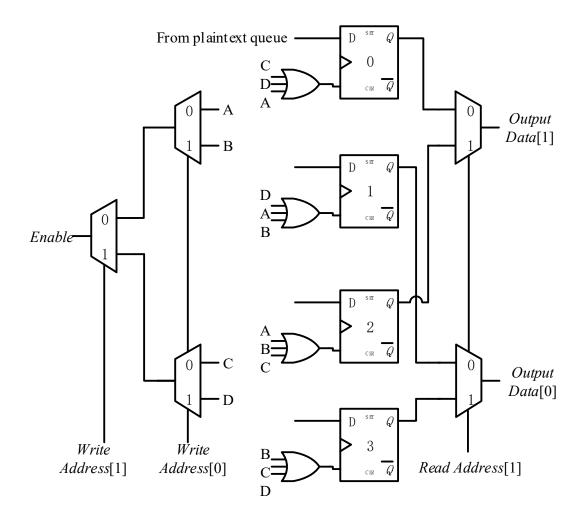

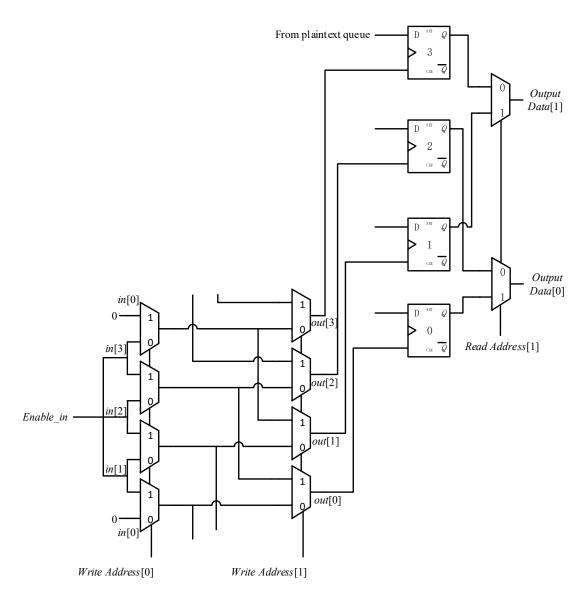

By piling up the 3-bit 2-to-1 muxes, a cascading structure can select the data from 4 inputs with 2 address lines. In Figure 4-8, the cascading structure is used at the output part of the queue. (Since the connections are complex, they have not been drawn.) Three muxes are piled up to perform as a 4-to-1 mux and connect four registers to 3 output bits. Assume four register bits are marked as 0, 1, 2 and 3 from top to the bottom, and  $Q_n$ ,  $0 \le n \le 3$ , is the output of each D flip-flop. The connecting method is as follows.

- (1)  $Q_0$ ,  $Q_1$  and  $Q_2$  are connected to the first input of pyramid structure.

- (2) Q<sub>1</sub>, Q<sub>2</sub> and Q<sub>3</sub> are connected to the second input of pyramid structure.

- (3) Q<sub>2</sub>, Q<sub>3</sub> and Q<sub>0</sub> are connected to the third input of pyramid structure.

- (4)  $Q_3$ ,  $Q_0$  and  $Q_1$  are connected to the fourth input.

The connection method is reasonable since we can find four possible combinations of three consecutive numbers among 4 register bits. By using this connection method and pyramid structure, it is guaranteed that each three consecutive bits can be selected.

Figure 4-8 Architecture of Plaintext Queue

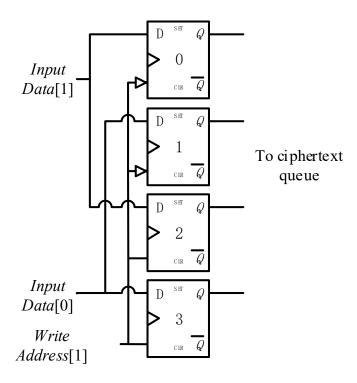

In Figure 4-8, we illustrate a small scale plaintext queue (M=4, B=3, and D=2) with the cascading structure used as the output part. For the input side of the queue, a simplified hardware structure is used by making the number of queue bits a multiple of the input width (in this case,  $M=2\times D$ ). For this small queue with the relationship between M and D, there are only two cases: (1) the write address starts at 00 and data is written to 00 and 01, and (2) the write address starts at 10 and data is written to 10 and 11. The higher bit of address is enough to select the placement of the 2 incoming data bits. The inputs will be sent to either  $D_0D_1$  or

D<sub>2</sub>D<sub>3</sub>. Since there is no combinational logic to route data input bits to register bits in this simple design (only appropriate wiring), the resource cost and propagation delay of the combinational logic on the input side is zero.

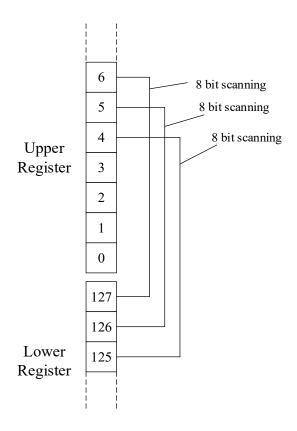

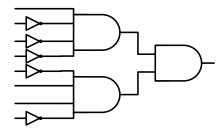

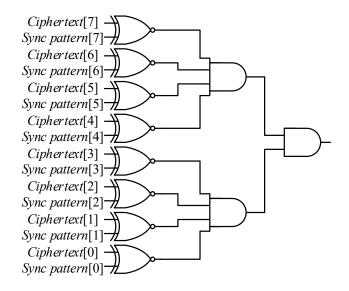

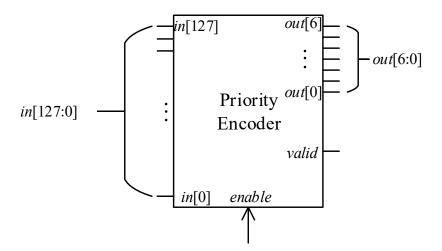

#### 4.3.1.2 Design Considerations for Full Scale System